Изобретение относится к запоминающим устройствам и может быть исполь зовано для производственного контроля блоков постоянной памяти/ выполненных на больших интегральных схемах (БИС ПЗУ). Известно устройство, содержащее микропрограммный автомат, регистр схем совпадения, регистр компараторов уровней и позволяющее контролировать постоянное запоминающее устройство по заданной таблице истинности, занесенной в память ЭВМ Недостатками этого .устройства являются большой объем оборудования и необходимость совместной работы с ЭВ Наиболее близким к изобретениюявляется устройство для контроля бло ка постоянной памяти, содержащее эталонное запоминакяцее устройство синхронизатор, счетчик адреса, блок сравнения, блок управления, блок пре образования уровней, блок измерения уровней, причем первый вход блока преобразования уровней соединен с первым выходом синхронизатора, второй - с выходом счетчика адреса, вход которого соединен с вторым вьисо дом синхронизатора, управляющий вход .которого соединен с первым выходом блока управления, второй выход блока управления соединен с первым вхо-, дом блок-а сравнения, выход которого соединен с первым входом блока управления, второй вход которого подключен к третьему выходу синхронизатора, а третий вход - к входу устройства 2. Недостатком данного устройства является низкое быстродействие вследствие необходимости иметь эталон для каждого типа блока постоянной памяти большой длительности и трудоемкости операций выбора и периодической перепроверки эталонов. Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в устройство, содержащее синхронизатор, .блок согласования уровней напряжения, счетчик адреса, блок управления, схему сравнения к- усилитель считывания, причем первый выход синхронизатора соединен с первым входом блока согласования уровней напряжения, второй вход и выход которого подключен соответственно к выходу счетчика адреса и к выходу устройства, вход усилителя считывания подключен ко входу устройства, второй и

третий выходы и вход синхронизатора соединены соответственно со входом счетчика адреса, с первым входом и с первым выходом блока управления вторые вход и выход которого подключены соответственно к первым выходу и входу схемы сравнения, введены муд ьтиплексор, сумматор по модулю два, регистр сдвига и регистр эталонного кода, выход которого подключен ко второму входу схемы сравнения, тактовый вход и один из выходов регистра, сдвига соединены соответственно с четвертым выходом синхронизатора и с третьим входом схемы сравнения,информационный вход и другие выходырегистра сдвига подключены соответственно ,к выходу и к одному из входов сумматора по модулю два, другой вход которого соединен с выходом мультиплексора, информационный и адресный входы которого Г1одключены соответственно к выходу усилителя считывания и к третьему выходу блока управления.

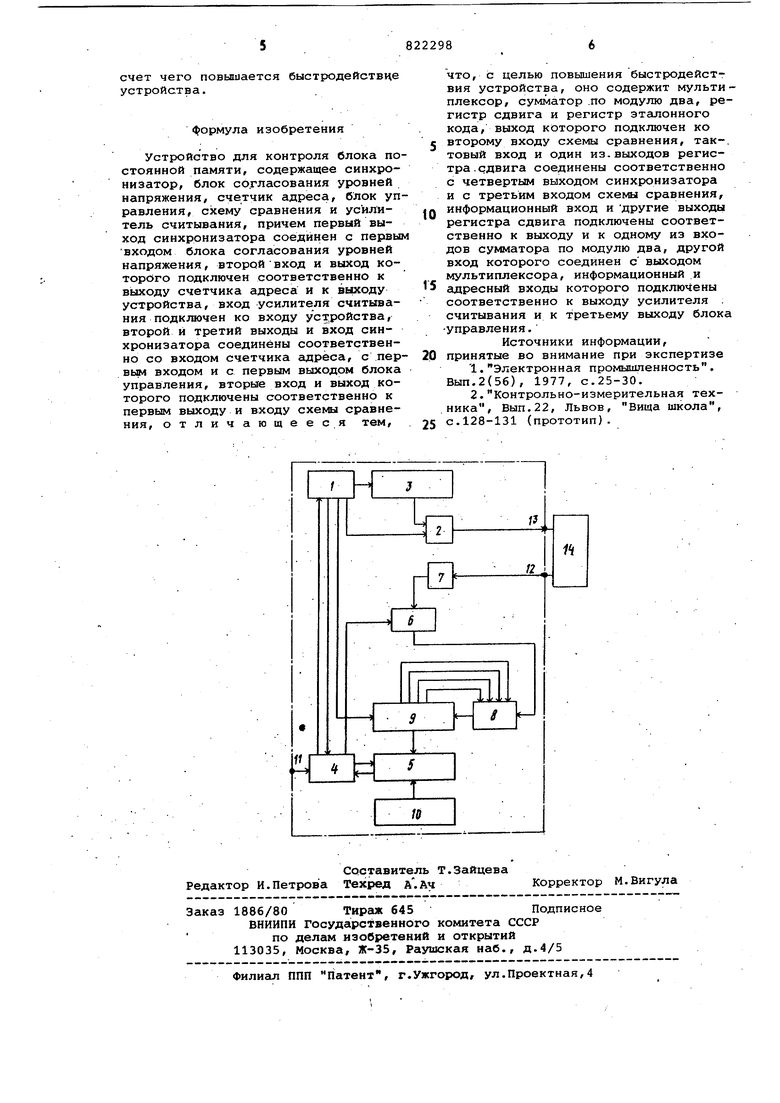

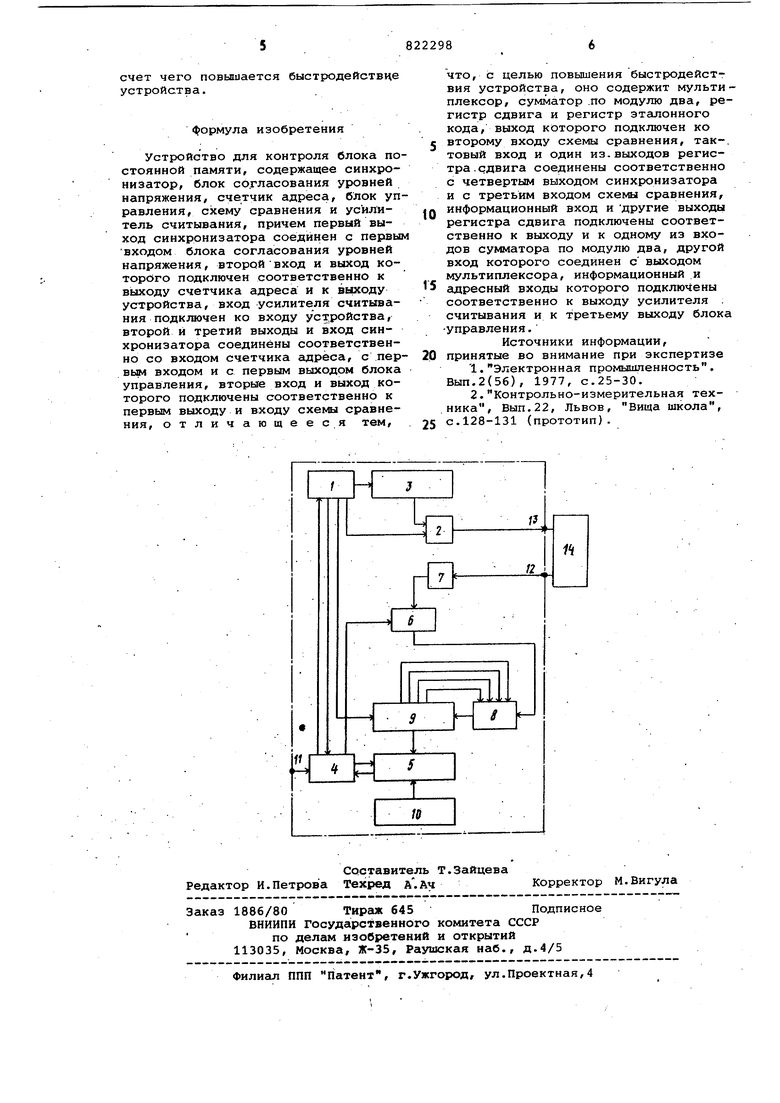

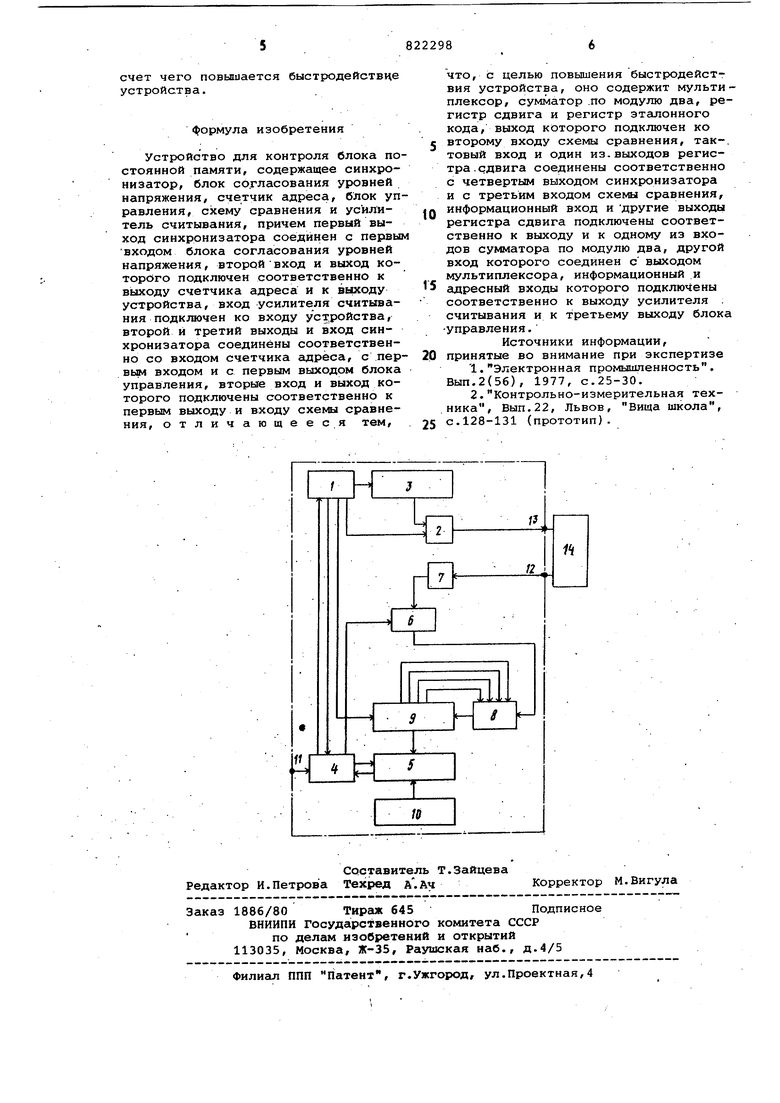

На чертеже изображена принципиальная схема предлагаемого устройства.

Устройство содержит синхронизатор 1, блок 2 согласования уровней напряжения, счетчик 3 адреса, блок 4 управления, схему 5 сравнения, мультиплексор б, усилитель 7 считывания, сумматор 8 по модулю два, регистр 9 сдвига, регистр 10 эталонного кода, управляющий вход 11,вход 12 и выход 13.

. Первый выход синхронизатора 1 соединен с первым входом блока 2 согласования уровней напряжения, второй вход и выход которого подключен соответственно к выходу счетчика 3 адреса и к выходу устройства 13. Вход усилителя 7 считывания подключен ко. входу устройства 12. Второй и третий выходы и вход синхронизатора 1 соединены соответственно со входом счетчика 3 адреса, с первым входом и первым выходом блока 4 управления, вторые вход и выход которого подключены соответственно к первым выходу и входу схемы 5 сравнения. Выход регистра 10 эталонного кода подключен ко второму входу схемы 5 сравнения. Тактовый вход и один из выходов регистра 9 сдвига соединены соответственно с четвертым выходом синхронизатора 1 и с третьим входом схемы 5 сравнения Информационный вход и другие выходы регистра 9 сдвига подключены соответственно к выходу и к одному из вхо. дов сумматора 8 по модулю два, другой вход которого соединен с выхо, дом мультиплексора б, информационный и адресный входы которого подключены соответственно к выходу усилителя 7 считывания и к третьему выходу блока 4 управления. Вход 12;И выход устройства соединяются с выходом и входом контролируемого блока 14 постоянной памяти. Контролируемый блок .14 постоянной памяти выполнен на больших интегральных схемах (БИСПЗУ)

Устройство работает следующим образом.

По сигналу, поступающему на вход 11 блок 4 управления запускает синхронизатор 1. Синхронизатор 1 формирует тактовые импульсы и сигналы управления, необходимые для работы контролируемого блока 14 постоянной памяти в соответствии с заданной временной диаграммой, и выдает их на блок 2 согласования уровней напряжения. Кроме того, синхронизатор 1 формирует импульсы сдвига, поступающие на счетчик 3 адреса и обеспечивающие его своевременное перек лючение. Код. адреса со счетчика 3 адреса поступает на блок 2 согласования уровней напряжения, который обеспечивает формирование уровней адресных, тактовых и управляющих сигналов, необходимых для работы контролируемого блока 14 постоянной памяти. Поступающие с блока 2 согласования уровней напряжения сигналы обеспеч1 вают последовательную выб;Орку информации по всем адресам контролируемого блока 14 постоянной памяти, сигналы с выхода которого поступают на усилитель 7 считывания, где их. уровни сравниваются с опорными напряжениями, и результаты сравнения поступают на информационный .вход мультиплексора б. Адрес канала мультиплексора б формируется блоком 4 управления. Информация с выхода мультиплексора б поступает на вход регистра 9 сдвига через сумматор 8 по модулю два. Сдвиг информации в регистре 9 сдвига осуществляется импульсами, поступающими с синхронизатора 1. После того, как через сумматор 8 по модулю два на регистр 9 сдвига поступит вся информация, считанная с контролируемого блока 14 постоянной памяти, блок 4 управления останавливает синхронизатор 1 и выдает стробирующий сигнал на схему 5 сравнения. По этому сигналу происходит сравнение информации находящейся в регистре 9 сдвига, с кодовой комбинацией, хранящейся в регистре 10 эталонного кода. В регистре 10 эталонного кода хранится код, соответствующий состоянию регистра 9- сдвига по окончании контроля блока 14 постоянной памяти., если он работает правильно. Результат сравнения фиксируется блоком 4 управления.

Технико-экономическое преимущество предлагаемого устройства заключается в том, что оно при обеспечении высокой точности контроля уменьшает время, необходимое для полного цикла контроля блока постоянной памяти,на 20% по сравнению с известным, за

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1986 |

|

SU1332322A1 |

| Телевизионный координатор | 1983 |

|

SU1109956A1 |

| Анализатор спектра Фурье | 1985 |

|

SU1302293A1 |

| Цифровой коррелятор | 1982 |

|

SU1073776A1 |

| Устройство для обхода узлов сеточной модели | 1985 |

|

SU1322332A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1983 |

|

SU1142825A1 |

| Устройство для контроля хода микропрограмм | 1988 |

|

SU1501067A2 |

| Устройство отождествления наборов данных | 1989 |

|

SU1654810A1 |

| Многофункциональный цифровой коррелометр | 1986 |

|

SU1363246A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1094071A1 |

Авторы

Даты

1981-04-15—Публикация

1979-04-16—Подача