Изобретение относится к вычислительной и измерительной технике и может использоваться в устройствах управляющих ЦВМ, цифровых вольтметрах, системах автоматизированного управления, контроля и регистрации параметров.

Известен цифровой милливольтметр следящего уравновешивания постоянного тока, содержащий нуль-орган, образованный двумя преобразователями напряжение - частота и блоком вычитания частот, реверсивный десятичный счетчик, преобразователь кодансшог, ключи, отсчетное устройство, блок управления, реверсивный счетчик непи автоматической компенсации дрейфа нуля и преобразователь код аисшог цепи автоматической компенсации дрейфа нуля JL

Недостатком данного устройства является сложность схемы, сравнительно невысокая надежность и точность преобразования.

Известен также преобразователь напряжение - код, содержащий генератор тактовых импульсов, подключенный к первому входу элемента запрета, преобразователь код - напряжение входы которого соединены с единичнами выходами п элементов памяти, а выход соединен с первым входом элемента сравнения, второй вход которого подключен к шине входного сигнала, нулевые входы элементов памяти подключены к выходу соответствующих вентилей сброса, первые входы которых соединены вместе, единичные входы каждого элемента памяти, кро0ме п-го, подключены к выходу соответствующего вентиля установки, один из входов вентиля установки первого элемента памяти соединен с выходом элемента запрета, вторым входом вен5тиля сброса и входом вентиля переноса этого элемента памяти, выход вентиля переноса каждого более младшего разряда элемента памяти подключен к входам вентиля сброса, пере0носа и установки элемента памяти с смежного старшего разряда, кроме п-го, выход вентиля переноса п-1-го разряда подключен к входу вентиля сброса п-го элемента памяти, причем

5 единичный выход каждого элемента памяти, кроме первого, подключен к единичному входу предыдущего эле.мента памяти через соответствующий вентиль установки, а нулевой выход

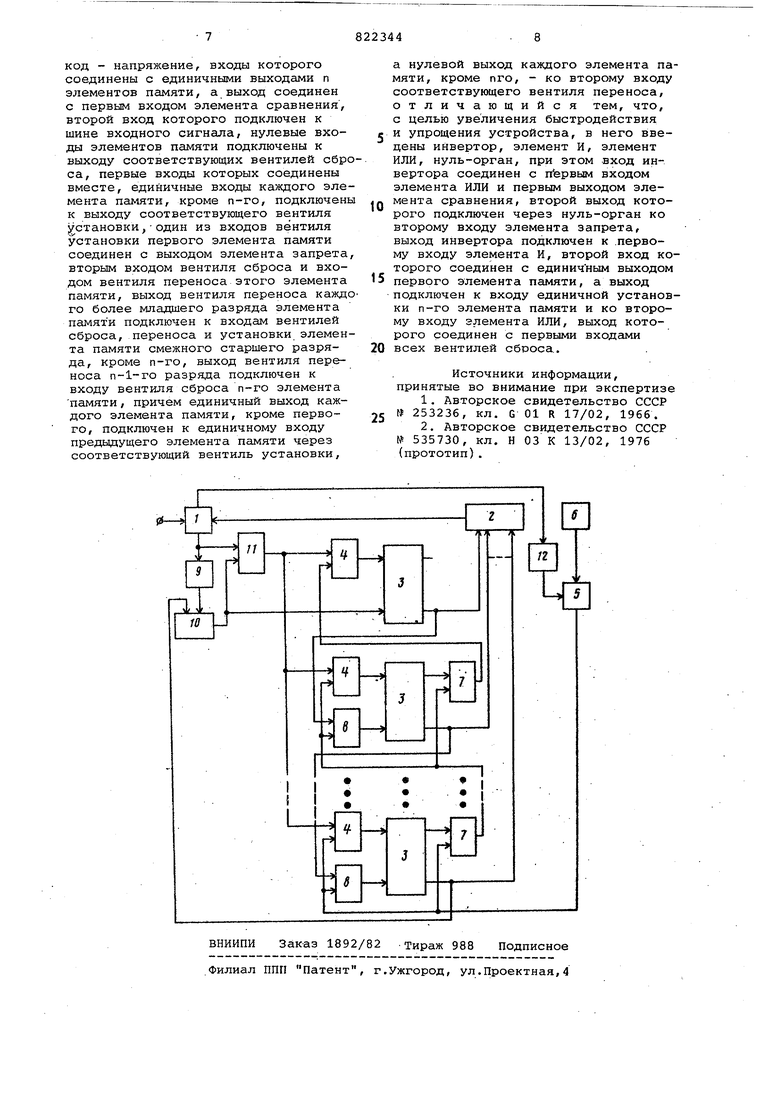

0 каждого элемента памяти, кроме п-гс КО второму входу соответствующего вентиля переноса . .Однако для преобразования в код измеряющейся входной величины напряжения с помощью известного устройства необходимо периодически сбрасывать элементы памяти в исходное состояние, чем значительно снижается, общее быстродействие преобразователя напряжение - код и услож няется его схема. Цель изобретения - увеличение быстродействия и упрощение устройст ва. Поставленная цель достигается тем, что в преобразователь напряжение - код, содержащий генератор так товых импульсов, подключенный к первому входу элемента запрета, преобразователь код - напряжение, входы которого соединены с единичными выходами п элементов памяти, а выход соединен с первым входом элемента сравнения, второй вход которого подключен к шине входного сигнала и у которого нулевые входы эле ментов памяти подключены к выходу своих вентилейi- сброса, первые входы которых соединены вместе, единич ные входы каждого элемента памяти, кроме п-го, подключены к выходу сво го вентиля установки, один из.входо вентиля установки первого элемента памяти соединен с выходом элемента запрета, вторым входом вентиля сбро са и входом вентиля переноса этого элемента памяти, выход вентиля переноса каждого более младшего раз ряда элемента памяти подключен к входам вентилей сброса, переноса и установки элемента памяти смежног старшего разряда, кроме п-го, выход вентиля переноса п-1-го разряда под ключен к входу вентиля сброса п-го элемента памяти, причем единичный выход каждого элемента Пс1мяти, кроме первого, подключен к единичному входу предыдущего элемента памяти через соответствующий вентиль установки, а нулевой выход Кс1ждого эле мента памяти, кроме п-го, - ко второму входу соответствующего вентиля переноса, введены инвертор, элемент И, элемент ИЛИ, нуль-орган, при этом вход инвертора соединен с пер вым входом элемента ИЛИ и первым выходом элемента сравнения, второй выход-которого подключен через нул орган ко второму входу элемента запрета, выход инвертора подключен к первому входу элемента И, второй вход которого соединен с единичным выходом первого элемента памяти, а выход подключен к входу единично установки п-го элемента памяти и к второму входу элемента ИЛИ, выход которого соединен с первыми вхЬдами всех вентилей сброса. На чертеже изображена структурая схема устройства. Преобразователь напряжение - код одержит элемент 1 сравнения, пребразователь 2 код - напряжение, элементов 3 памяти, п вентилей 4 сброса, элемент 5 запрета, генераор 6 тактовых импульсов, п-1 венилей 7 переноса, п-1 вентилей 8 усановки, инвертор 9, элемент И 10, лемент ИЛИ 11 и нуль-орган 12, Входы преобразователя 2 код - напяжение соединены с единичными выходами п элементов 3 памяти. При появлении потенциалов на этих выходах срабатывают соответствующие этим выходам разряды преобразователя код напряжение, вырабатывая соответствующие этим разрядам эталонные напряжения. Эталонные напряжения на выходе преобразователя 2 код-напряжение суммируются и поступают на один из входов элемента 1 сравнения, на второй вход которого подается входное напряжение, которое необходимо преобразовать в код, элемент 1 сравнения имеет два выхода, на первом из которых появляется потенциал логической единицы при превышении эталонным напряжением входного. Первый выход элемента 1 сравнения соединен с одним из входов элемента ИЛИ 11 и через инвертор9 - с одним из входов элемента И 10. Второй выход элемента 1 сравнения - это выход разностного напряжения между входным и этсшонным - подключен ко входу нуль-органа, на выходе которого исчезает потенциал логической единицы, когда напряжение на его входе становится меньше с1мплитуды эталонного напряжения наи-. меньшего разряда. Для случая, когда в преобразователе напряжение - код разряды эталонного напряжения преобразователя код-напряжение одинаковы по величине, нуль-орган 12 настраивается на срабатывание от напряжений на его входе в диапазоне от нуля до величины одного разряда эталонного напряжения. Другой вход элемента ИЛИ 11 соединен с выходом элемента И 10 и с входом единичной установки п-го элемента 3 памяти. Другой вход элемента И 10 подключен к единичному выходу первого элемента 3 памяти. Шлход нуль-органа 12 соединен с одним из входов элемента 5 запрета, другой вход которого подключен к выходу генератора б тактовых импульсов. Нулевые входы элементов 3 памяти подключены к выходу своих вентилей 4 сброса, первые входы которых соединены вместе и подключены к выходу элемента ИЛИ 11, единичные входы каждого элемента 3 памяти, кроме п-го, подключены к выходу своего вентиля 8 установки. Один из входов вентиля 8 установки первого элемента 3 памяти соединен с выходом элемента 5 запрета, вторым входом вентиля 4 сброса и входо вентиля 7 переноса этого элемента 3 Пс1мяти,. выход вентиля 7 переноса каждого более младшего разряда элемента 3 памяти подключен к входам вентилей 4 сброса, 7 переноса и 8 установки элемента 3 памяти смежног старшего разряда, кроме п-го, а так же к входу вентиля 4 сброса, п-го элемента 3 памяти, причем единичный выход каждого элемента 3 памяти, кр ме первого, подключен к единичному входу предыдущего элемента памяти через соответствующий вентиль 8 уст новки, а нулевой выход каждого элемента 3 памяти, кроме п-го, - к дру гому входу соответствующего вентиля 7 переноса. Преобразователь напряжение - код работает следующим образом. Предположим, что после включения преобразователя напряжение-код все элементы 3 памяти, кроме второго и третьего, устанавливаются в состояние О или, что в какой-тб момент времени это состояние соответствует равенству эталонного напряжения пре образователя 2 код - напряжение и входного напряжения. По потенциалу с единичного выхода второго, и треть го элементов 3 памяти включаются вт рой и третий разряды преобразователя 2 код - напряжение, а на вход элемента 1 сравнения поступает суммарное эталонное напряжение. Спустя какое-то время, допустим, величина входного напряжения увеличивается. При этом равенство входных напряжений элемента 1 сравнения нарушается и на втором выходе устанавливается потенциал, который откры вает элемент 5 запрета через нульорган 12 для прохождения частоты генератора 6 тактовых импульсов. По заднему фронту первого импульса тактовой частоты через вентиль 8 установки устанавливается в состояние 1 первый элемент 3 памяти. По потенциалу с единичного выхода этого элемента 3 памяти включается 1-й раз ряд преобразователя 2 код - напряжвние, и на элемент 1 сравнения поступает дополнительное эталонное напрЯ жение. Если разница межяу входншш напряжениями элемента 1 сравнения меньше величины наименьшей ступеньки эталонного напряжения, на выходе нуль-органа 12 появляется потенциал, который закрывает элемент 5 запрефа.

Предположим, что напряжение от источника входного сигнала снова становится больше выработанного эталонного напряжения. При этом, кг1К и в предьщущих случаях, на первом выходе элемента 1 сравнения еще не появляется логический потенциал.

60

Формула изобретения

Преобразователь напряжение - код, содержащий генератор тактовых импульсов, подключенный к первому входу элемента запрета, преобразователь т.е. на этом выходе сохраняется уровень логического О. Этот логический О инвертируется инвертором 9, и на первом входе элемента И 10 он присутстсэует логической 1. А так как на втором входе эдемента И 10 уже присутствует логическая 1 с единичного выхода первого элемента 3 памяти, то через элемент ИЛИ 11 эта логическая 1 поступает на первые входы всех вентилей 4 сброса. При приходе заднего фронта .тактового импульса через вентиль установки 8 первый элемент 3 памяти устанавливается в состояние О. Это приводит к отключению первого разряда преобразователя 2 код - напряжение и уменьуменьшению этсшонного напряжения, появлению на первых входах всех вентилей 4 сброса логического О, а перед этим и на выходе элемента И 10, что приводит к установке в состояние 1 п-го элемента 3 памяти. По потенциалу-с единичного выхода п-го элемента 3 памяти включается п-й разряд преобразователя 2 код - напряжение, а на вход элемента 1 сравнения поступает дополнительное эталонное напряжение, соответствующее этому разряду. Предположим, что напряжение от источника входного сигнала меньше выработанного эталонного напряжения, при этом первый элемент 1 сравнения на первом своем выходе уже формирует потенциал логической 1, который через элемент ИЛИ 11 поступает на первые входы всех вентилей 4 сброса. При поступлении заднего фронта следующего тактового импульса с выхода вентиля 7 переноса через вентиль 4 сброса устанавливается п-й элемент 3; памяти в состояние О, вызывая отключение п-го разряда преобразователя 2 код - напряжение. Одновременно по заднему фронту этого же тактового импульса через вентиль 8 установки п- 1-й элемент 3 памяти устанавливается в состояние 1. По потенциалу с единичного выхода п-1-го элемента 3 памяти включается n-1-й разряд преобразователя 2 код - напряжение, при этом на вход элемента 1 сравнения поступает эталонное напряжение этого разряда. Если это напряжение равно входному, то элемент 1 сравнения закрывает элемент 5 запрета, закончив, таким образом, процесс преобразования до следующего изменения входного напряжения.

код - напряжение, входы которого соединены с единичными выходами п элементов памяти, а выход соединен с первым входом элемента сравнения , второй вход которого подключен к шине входного сигнала, нулевые входы элементов памяти подключены к выходу соответствующих вентилей сбрса, первые входы которых соединены вместе, единичные входы каждого элемента памяти, кроме п-го, подключен к выходу соответствующего вентиля / становки, - один из входов вентиля установки первого элемента памяти соединен с выходом элемента запрета вторым входом вентиля сброса и входом вентиля переноса этого элемента памяти, выход вентиля переноса кажд го более младшего разряда элемента памяти подключен к входам вентилей сброса, переноса и установки, элемента памяти смежного старшего разряда, кроме п-го, выход вентиля переноса П-1-ГО разряда подключен к входу вентиля сброса п-го элемента памяти, причем единичный выход каждого элемента памяти, кроме первого, подключен к единичному входу предыдущего элемента памяти через соответствующий вентиль установки.

а нулевой выход каждого элемента памяти, кроме пго, - ко второму входу соответствующего вентиля переноса, отличающийся тем, что, с целью увеличения быстродействия 5 и упрощения устройства, в него введены инвертор, элемент И, элемент ИЛИ, нуль-орган, при этом вход инвертора соединен с первым входом элемента ИЛИ и первым выходом элеQ мента сравнения, второй выход которого подключен через нуль-орган ко второму входу элемента запрета, выход инвертора подключен к .первому входу элемента И, второй вход которого соединен с единичным выходом

5 первого элемента памяти, а выход подключен к входу единичной установки п-го элемента памяти и ко второму входу элемента ИЛИ, выход которого соединен с первыми входами

0 всех вентилей сбооса.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 5 ff 253236, кл. G 01 R 17/02, 1966.

2.Авторское свидетельство СССР № 535730, кл. Н 03 К 13/02, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь напряжение-код | 1975 |

|

SU535730A1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU984041A1 |

| Устройство для измерения погрешности аналого-цифрового преобразователя | 1982 |

|

SU1115219A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Аналого-цифровой преобразователь в кодах с естественной избыточностью | 1986 |

|

SU1381698A1 |

| Устройство для контроля логических блоков | 1988 |

|

SU1553980A1 |

| Устройство для ввода аналоговой информации | 1988 |

|

SU1501026A1 |

| Преобразователь двоичного кода в число-импульсный код | 1980 |

|

SU943704A1 |

| Аналого-цифровой преобразователь | 1988 |

|

SU1547062A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМ ЗАМКОМ | 2002 |

|

RU2209909C1 |

Авторы

Даты

1981-04-15—Публикация

1979-05-07—Подача