Изобретение относится к импульсной технике и может быть использовано, например, в качестве выходного усилителя постоянных запоминающих устг ройств.

Известен формирователь выходных сигналов, содержащий первый элемент И-НЕ, второй элемент И-НЕ, выход которого соединен с входом инвертора, выход которого соединен с входом выходного каскада lj .

Недостатками устройства являются О1 раничен,ность функциональных возможностей и сложность изготовления.

. Наиболее близким к предлагаемому является усилитель-формирователь выходных сигналов постоянных запоминающих устройств на МОП-транзисторах, содержащий триггер, первый выход которого соединен с входом первого инвертора, второй выход - с входом второго инвертора, ключевой транзистор, включенный между точкой соединения истоков ключевых транзисторов триггера и общей шиной устройства, а затвор ключевого транзистора соединен с шиной тактового сигнала, выходной усилительный каскад, прямую и инверсную шины ввода данных 2

Недостатком данного устройства является низкое быстродействие.

Цель изобретения - повышение быстродействия.

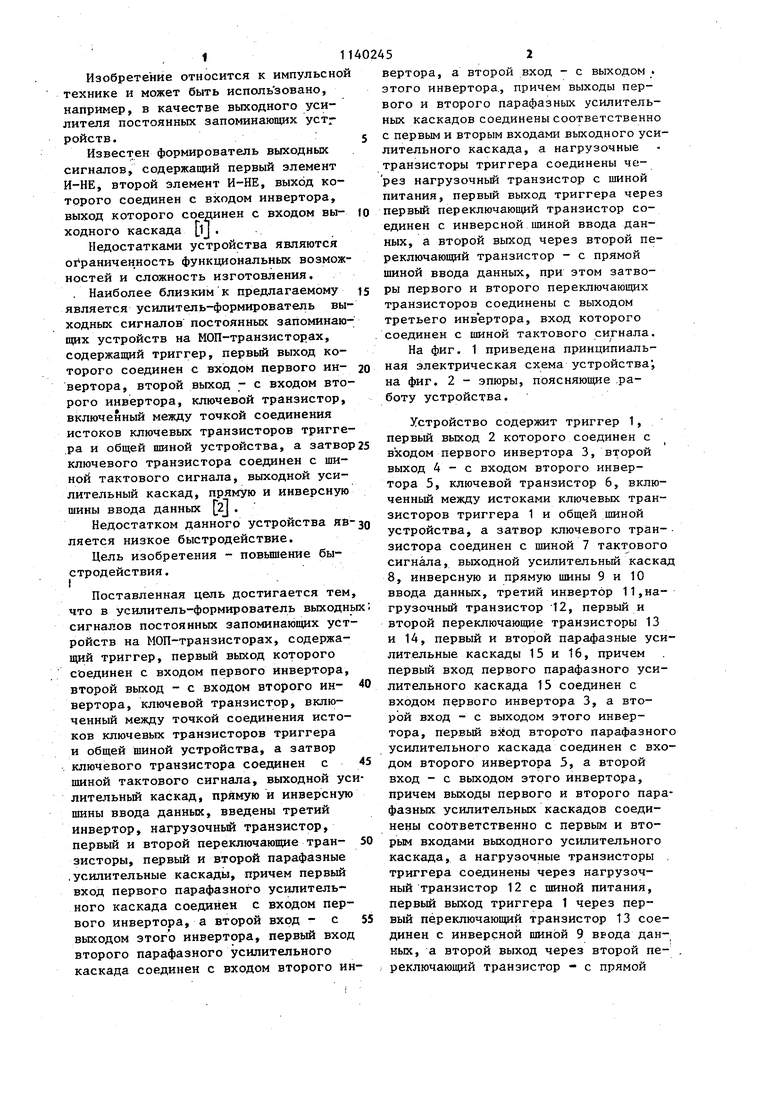

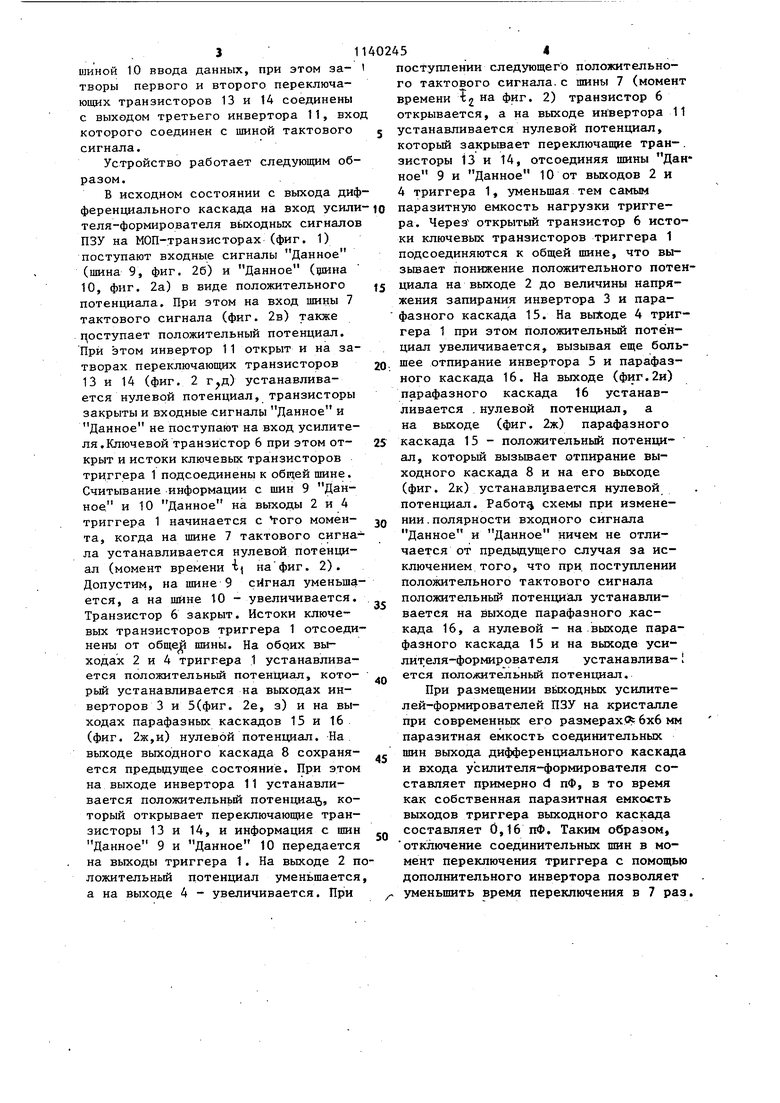

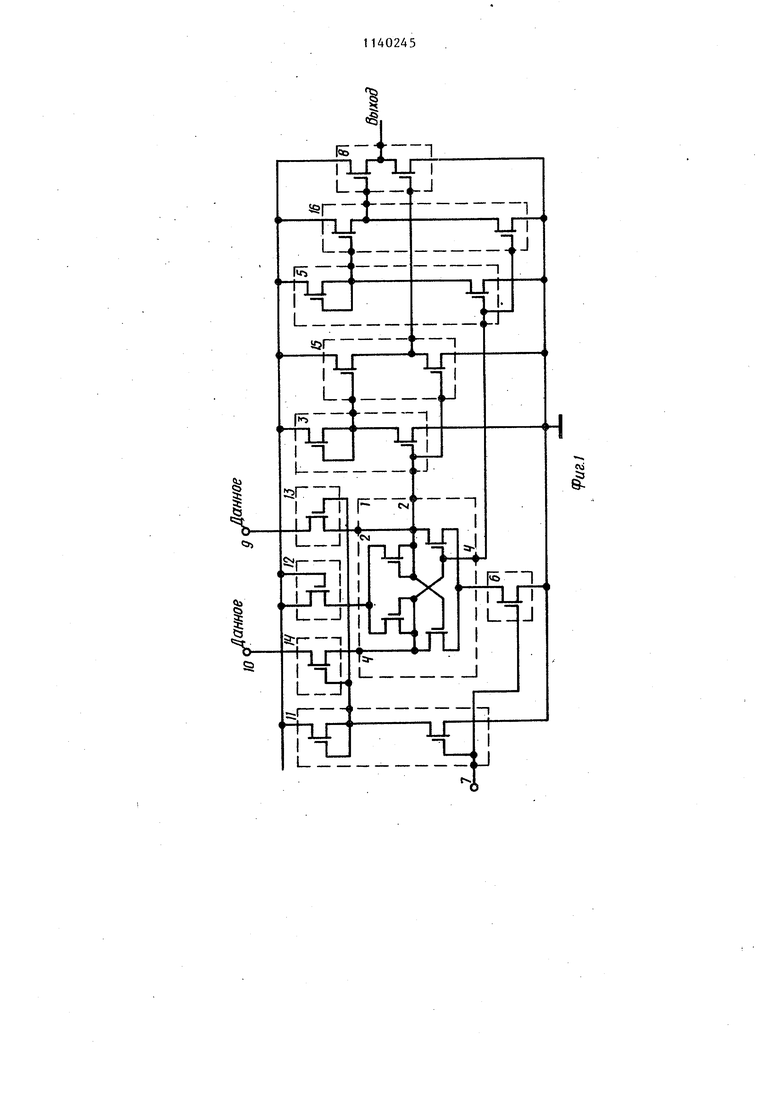

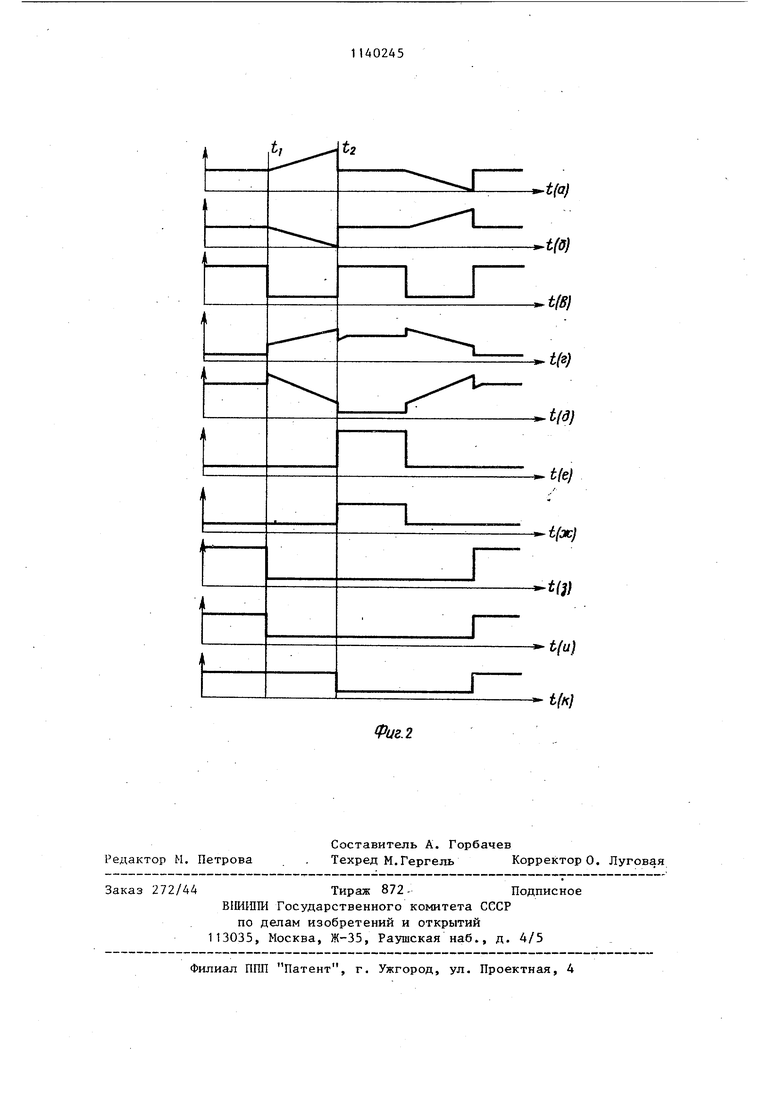

Поставленная цель достигается тем что в усилитель-формирователь выходнь сигналов постоянных запоминающих устройств на МОП-транзисторах, содержащий триггер, первый выход которого соединен с входом первого инвертора, второй выход - с входом второго инвертора, ключевой транзистор, включенный между точкой соединения истоков ключевых транзисторов триггера и общей шиной устройства, а затвор ключевого транзистора соединен с щиной тактового сигнала, выходной усилительный каскад, прямую и инверсную шины ввода данньк, введены третий инвертор, нагрузочный транзистор, первый и второй переключающие транзисторы, первый и второй парафазные .усилительные каскады, причем первый вход первого парафазного усилительного каскада соединен с входом первого инвертора, а второй вход - с выходом этого инвертора, первый вход второго парафазного усилительного каскада соединен с входом второго инвертора, а второй вход - с выходом . этого инвертора., причем выходы первого и второго парафазных усилительных каскадов соединены соответственно с первым и вторым входами выходного усилительного каскада, а нагрузочные транзисторы триггера соединены через нагрузочный транзистор с шиной питания, первый выход триггера через первый переключающий транзистор соединен с инверсной шиной ввода данных, а второй выход через второй переключающий транзистор - с прямой шиной ввода данных, при этом затворы первого и второго переключаюш 1Х транзисторов соединены с выходом третьего инвертора, вход которого соединен с шиной тактового сигнала. На фиг. 1 приведена принципиальная электрическая схема устройства; на фиг. 2 - эпюры, поясняющие .работу устройства.

Устройство содержит триггер 1, первый выход 2 которого соединен с входом первого инвертора 3, второй выход 4 - с входом второго инвертора 5, ключевой транзистор 6, включенный между истоками ключевых транзисторов триггера 1 и общей шиной устройства, а затвор ключевого транзистора соединен с шиной 7 тактового сигнала, выходной усилительный каска 8, инверсную и прямую шины 9 и 10 ввода данных, третий инвертор 11,нагрузочный транзистор 12, первый и второй переключающие транзисторы 13 и 14, первый и второй парафазные усилительные каскады 15 и 16, причем первый вход первого парафазного усилительного каскада 15 соединен с входом первого инвертора 3, а второй вход - с выходом этого инвертора, первый вз4оД второто парафазног усилительного каскада соединен с входом второго инвертора 3, а второй вход - с выходом этого инвертора, причем выходы первого и второго парафазных усилительных каскадов соединены соответственно с первым и вторым входами выходного усилительного каскада, а нагрузочные транзисторы триггера соединены через нагрузочный транзистор 12 с шиной питания, первый выход триггера 1 через первый переключающий транзистор 13 соединен с инверсной шиной 9 ввода данных;, а второ.й выход через второй переключающий транзистор - с прямой шиной 10 ввода данных, при этом затворы первого и второго переключающих транзисторов 13 и 14 соединены с выходом третьего инвертора 11, вхо которого соединен с шиной тактового сигнала. Устройство работает следующим образом. В исходном состоянии с выхода диф ференциального каскада на вход усили теля-формирователя вькодных сигнало ПЗУ на МОП-транзисторах (фиг. 1) поступают входные сигналы Данное (шина 9, фиг. 26) и Данное (1шна 10, фиг. 2а) в виде положительного потенциала. При этом на вход шины 7 тактового сигнала (фиг. 2в) также г оступает положительный потенциал. При этом инвертор 11 открыт и на затворах переключающих транзисторов 13 и 14 (фиг. 2 ) устанавливается нулевой потенциал, транзисторы закрыты и входные сигналы Данное и Данное не поступают на вход усилителя. Ключевой транзистор 6 при этом открыт и истоки ключевых транзисторов триггера 1 подсоединены к общей шине. Считывание информации с шин 9 Данное. и 10 Данное на выходы 2 и 4 триггера 1 начинается с того момента, когда на шине 7 тактового сигна ла устанавливается нулевой потенциал (момент времени i нафиг. 2). Допустим, на шине 9 сигнал уменьша ется, а на шине 10 - увеличивается. Транзистор 6 закрыт. Истоки ключевых транзисторов триггера 1 отсоеди нены от обще шины. На обоих выходах 2 и 4 триггера 1 устанавливается положительный потенциал, который устанавливается на выходах инверторов 3 и 5(фиг. 2е, з) и на выходах парафазных каскадов 15 и 16. (фиг. 2ж,и) нулевой потенциал. На выходе выходного каскада 8 сохраняется предьщущее состояние. При этом на выходе инвертора 11 устанавливается положнтельньй пoтeнциaJг„ который открывает переключающие транзисторы 13 и 14, и информация с шин Данное 9 и Данное 10 передается на выходы триггера 1. На выходе 2 п ложительный потенциал уменьшается а на выходе 4 - увеличивается. При поступлении следующего положительного тактового сигнала.с шины 7 (момент времени 2 Фиг. 2) транзистор 6 открывается, а на выходе инвертора 11 устанавливается нулевой потенциал, который закрывает переключащие трав-. зисторы 13 и 14, отсоединяя шины Данное 9 и Данное 10 от выходов 2 и 4 триггера 1, уменьшая тем самым паразитную емкость нагрузки триггера. Через открытый транзистор 6 истоки ключевых транзисторов триггера 1 подсоединяются к общей шине, что вызывает понижение положительного потенциала на выходе 2 до величины напряжения запирания инвертора 3 и парафазного каскада 15. На выХоде 4 триггера 1 при этом положительный потенциал увеличивается, вызывая еще большее отпирание инвертора 5 и парафазного каскада 16. На выходе (фиг.2и) парафазного каскада 16 устанавливается .нулевой потенциал, а на выходе (фиг. 2ж) парафазного каскада 15 - положительный потенциал, который вызьгоает отпирание выходного каскада 8 и на его выходе (фиг. 2к) устанавливается нулевой потенциал. Работу схемы при изменении .полярности входного сигнала Данное и Данное ничем не отличается от предьщущего случая за исключением того, что при. поступлении положительного тактового сигнала положительный потенциал устанавливается на выходе парафазного каскада 16, а нулевой - на выходе парафазного каскада 15 и на выходе усилителя-формирователя устанавливается положительный потенциал. При размещении вькодных усилителей-формирователей ПЗУ на кристалле при современных его размерах ; 6x6 мм паразитная емкость соединительных шин выхода дифференциального каскада и входа усилителя-формирователя составляет примерно d пФ, в то время как собственная паразитная емкость выходов триггера выходного каскада составляет 0,16 пФ. Таким образом, отключение соединительных шин в момент переключения триггера с помощью дополнительного инвертора позволяет уменьшить время переключения в 7 раз.

t(d)

| название | год | авторы | номер документа |

|---|---|---|---|

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Усилитель-формирователь | 1982 |

|

SU1065883A1 |

| Выходной усилитель | 1981 |

|

SU1015436A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU841047A1 |

| Формирователь выходного сигнала на МДП-транзисторах | 1986 |

|

SU1338055A1 |

| Стробируемый усилитель | 1986 |

|

SU1332525A1 |

| Формирователь тактовых импульсов | 1975 |

|

SU566355A1 |

| Буферное устройство | 1979 |

|

SU822366A1 |

| Выходное устройство | 1978 |

|

SU771874A1 |

| ЛОГИЧЕСКОЕ КОНВЕЙЕРНОЕ УСТРОЙСТВО | 2000 |

|

RU2175811C1 |

УСИЛИТЕЛЬ-ФОРМИ{ ОВАТЕЛЬ ВЫХОДНЫХ СИГНАЛОВ ПОСТОЯННЫХ ЗАПОМИНАЮЩИХ УСТРОЙСТВ НА МОП-ТРАНЗИСТОРАХ, содержащий триггер, первый выход которого соединен с входом первого инвертора, второй выход - с входом второго инвертора, ключевой транзистор, включенньм между точкой соединения истоков ключевых транзисторов триггера и общей шиной устройства, затвор ключевого транзистора соединен с шиной тактового сигнала, выходной усилительный каскад, прямую и инверсную шины ввода данных, отличающийся тем, что, с целью повышения быстродействия, в него введены третий инвертор, нагрузочный транзистор, первый и второй переключающие транзисторы, первый и второй парафазные усилительные каскады, причем первый вход первого парафазного усилительного каскада соединен с входом первого инвертора, а второй вход - с выходом этого инвертора5 первый вход второго парафазного усилительного каскада соединен с входом второго инвертора, а второй вход - с выходом этого инвертора, причем выходы первого и второго парафазных усилительных каскадов соединены соответственно с первым и вторым входами выходного усилительного каскада, а нагрузочные транзисторы триггера соединены через (/) нагрузочньй транзистор с шиной питания, первый выход триггера через первый переключающий трназистор соединен с инверсной шиной ввода данных, а второй выход через второй переключающий транзистор - с прямой шиной ввода данных, при этом затворы 4 первого и второго переключающих транзисторов соединены с выходом третьего инвертора, вход которого соединен с шиной тактового сигнала. СП

Ir

t(e)

/

-i(x)

t(j)

W

i(K}

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-02-15—Публикация

1983-04-27—Подача