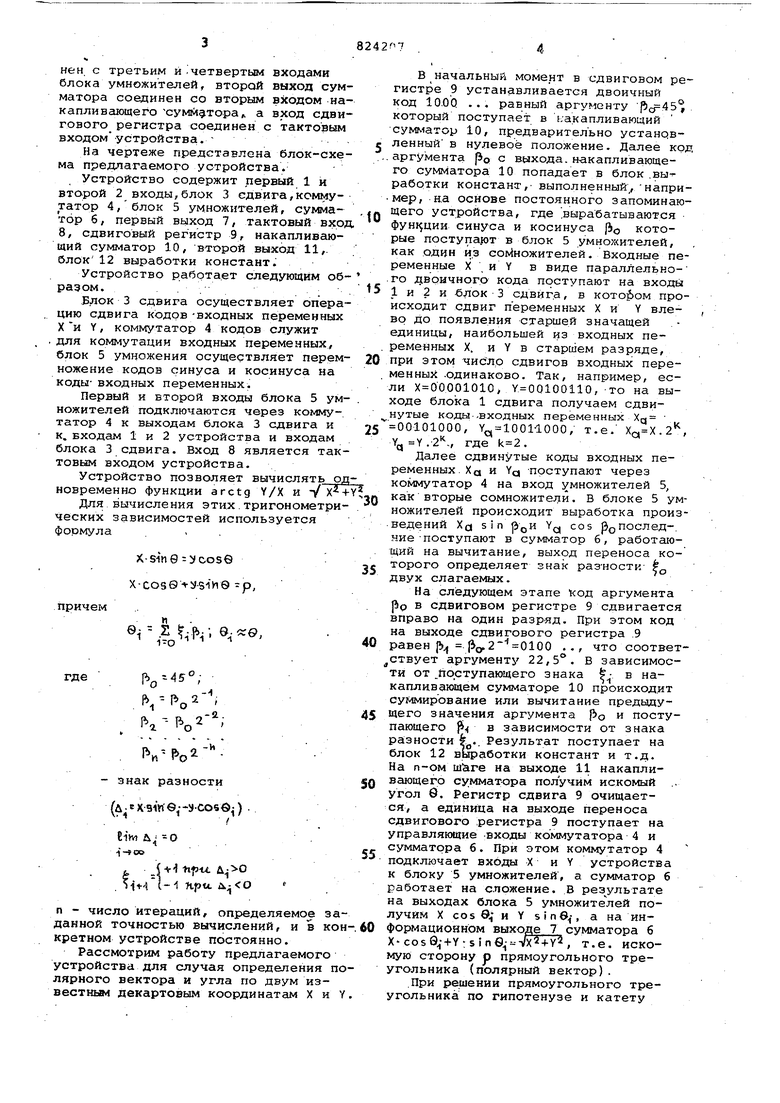

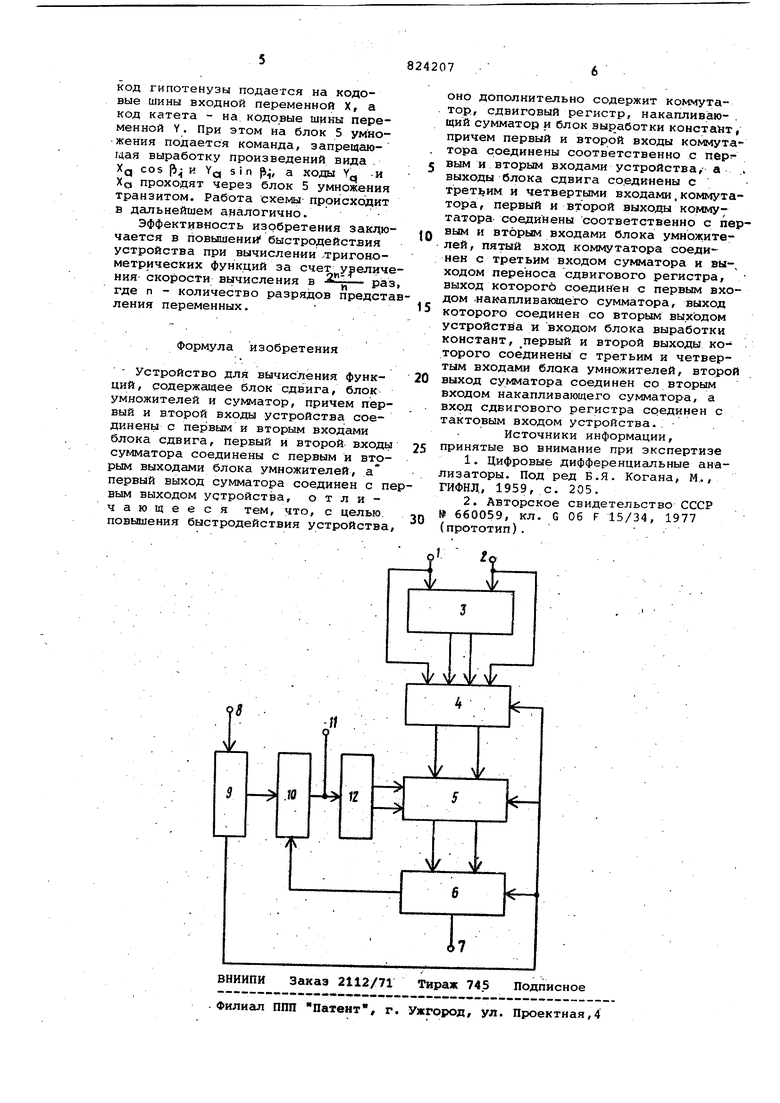

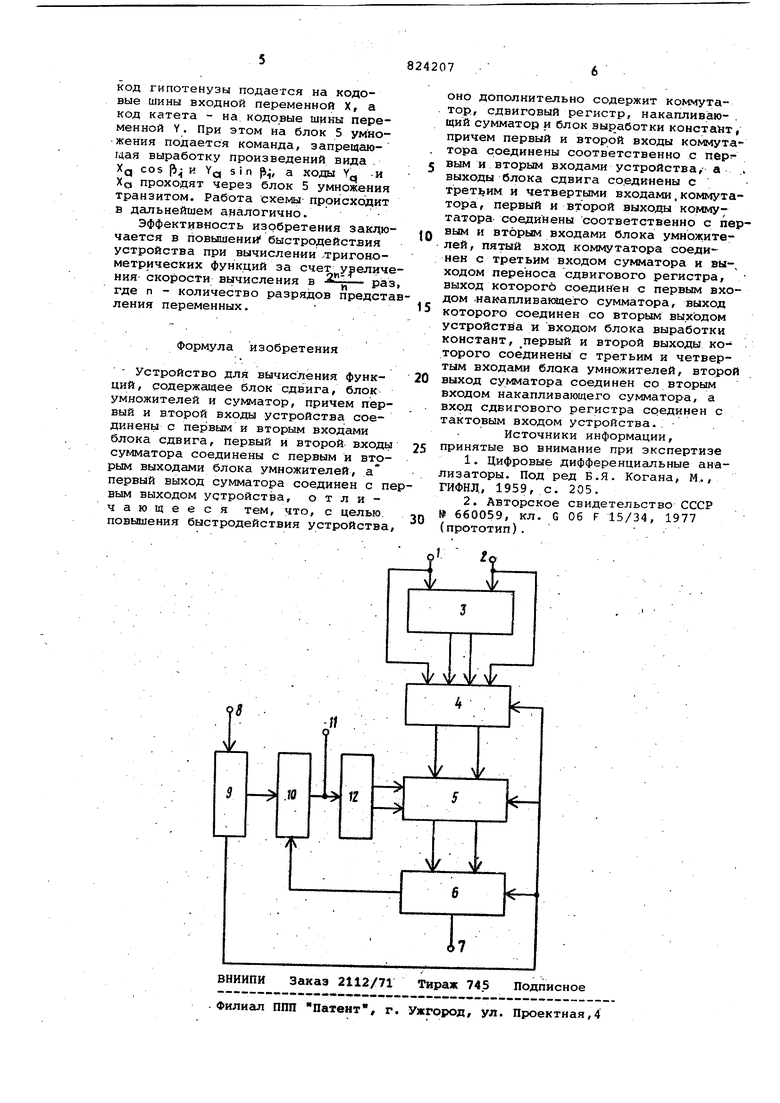

.. t Изобретение относится к автоматике и вычислительной технике и может быть использовано в устройствах Ц11Ф рового автоматического управления и в тригонометрических вычислителях ЦВМ. Известны устройства для вычислени функций, использующих метод интегрирования цифровых сигналов 1 . Недостатком этих устройств являют ся значительные аппаратурные затраты. Известно также устройство для вычисления функций, использующее итерационный метод 2. Наиболее близким техническим реше нием к предлагаемому является устройство для вычисления функций, содержсццее блок сдвига, блок умножиталей, функциональный генератор и ге нератор импульсов, сумматор,.компаратор, cxei-iy управления и схему или счетчик 2 .. Недостатком обоих устройств является недостаточное быстродействие при вычислениях функций. Цель изобретения - повышение быс родействия устройства за счет увели чения скорости вычисления. Поставленная цель достигается тем, что в устройство для вычисления функций, содержащее блок сдвига, блок умножителей и сумматор, причем пер-. вый и второй входы устройства соединены с первым и вторым входами блока сдвига, первый и второй входы сумматора соединены с первым и вторым выходами блока умножителей, а пер(ВЫй выход сумматора соединен с первым выходом устройства, дополнительно введены коммутатор, сдвиговый регистр, накапливающий сумматор и блок выработки констант, причем первый и второй входы коммутатора соединены соответственно с первым и вторым входами устройства, выходы блока сдвига Соединены с третьим и четвертыми входами коммутатора, первый и второй выходы коммутатора соединены соответственно с первым и вторым входами блока умножителей, пятый вход коммутатора соединен с третьим входом сумматора и выходом переноса сдвигового регистра, выход которого соединен с первым входом накапливающего сумматора, выход которого соединен со вторым выходом устройства и входом блока выработки констант, первый и второй выходы которого соединен с третьим и.четвертым входами блока умножителей, второй выход сум матора соединен со вторым взсодом на капливающего cyMiJt Topa а вход сдви гового регистра соединен с тактовым входомустройства, На чертеже представлена блок-схе ма предлагаемого устройства. Устройство содержит первый 1 и второй 2 входы,блок 3 сдвига,коммутатор 4,блок 5 умножителей, сумматор 6, первый выход 7, тактовый вхо 8, сдвиговый регистр 9, накапливающий сумматор 10, второй выход 11,. блок12 выработки констант. Устройство работает следующим об разом. . .. Блок 3 сдвига осуществляет опера цию сдвига кодов -входных переменных Xи Y, коммутатор 4 кодов служит для коммутации входных переменных, блок 5 умножения осуществляет перем ножение кодов синуса и косинуса на коды- входных переменных. Первый и второй входы блока 5 ум ножителей подключаются через коммутатор 4 к выходам блока 3 сдвига и к, входам 1 и 2 устройства и входам блока 3 сдвига. Вход 8 является так товым входом устройства. Устройство позволяет вычислять о новременно функции arctg Y/X и V Х Для вычисления этих.тригонометри ческих зависимостей используется формула . . . X-s-in0:i(cos© x-coes y-sinQ р, причем . 9,, ( Ро - знак разности (й.еХ91Пв- -С05«) ч. т. . Eih й О ь . Hpu u,O n - ЧИСЛО итераций, определяемое з данной точностью вычислений, и в ко кратном устройстве постоянно. Рассмотрим работу предлагаемого устройства для случая определения п лярного вектора и угла по двум известным Декартовым координатам X и В начальный момент в сдвиговом регистре 9 устанавливается двоичный код 10.0Q ... равный аргументу Рсг45° который поступает в накапливающий сумматор 10, предварительно установленный в нулевое положение. Далее код аргумента РО с выхода, накапливающего сумматора 10 попадает в блок ,выработки констант,, выполненный например, н.а основе постоянного запоминающего устройства, где .вырабатываются . синуса и косинуса которые поступа.ют в блок 5 умножителей, как один из сомножителей. Входные переменные X ,и Y в виде параллельного двоичного кода поступают на входы 1 и 2 и .блок 3 сдвига, в котобом происходит сдвиг переменных X и Y влево До появления старшей значащей единицы, наибольшей из входных переменных X. и Y в старшем разряде, при этом сдвигов входных переменных .одинаково. Так, например, если X 000pl010 Y 00100110,.то на выходе блока 1 сдвига получаем сдвинутые коды.-входных переменных Xq 00101000, Yq 10011000, т.е. Хс, Х.2, Yq Y.-2,, где . Далее сдвинутые коды входных переменных. X а и Yg Поступают через коммутатор 4 на вход умножителей 5, как вторые сомножители. В блоке 5 умножителей происходит выработка произ.ведений Хд s 1 n cos р послед-. ние-поступают в сумматор 6, работающий на вычитание, выход переноса которого определяет знак разности двух слагаемых. На следующем этапе код аргумента ро в сдвиговом регистре 9 сдвигается вправо на один разр.яд. При этом код на выходе сдвигового регистра .9 равен Ь Ро. .., что соответствует аргументу 22,5. В зависимости от .поступающего знака в накапливающем сумматоре 10 происходит суммирование или вычитание предыдущего значения аргумента и поступающего Р в зависимости от знака разности д.. Результат поступает на блок 12 выработки констант и т.д. На п-ом на выходе 11 накапливающего сумматора получим искомый .. угол б. Регистр сдвига 9 очищается, а единица на выходе переноса сдвигового регистра 9 поступает на управляющие .входы коммутатора 4 и сумматора 6. При этом коммутатор 4 подключает входы X и Y устройства к блоку 5 умножителей, а сумматор б работает на сложение. В рез ульгате на выходах блока 5 умножителей получим X cos Of и Y sine.,-, а на информационном выходе 7 сумматора 6 Х- cos : S i ne - --Vx2+Y , т.е. искомую сторону p прямоугольного треугольника (полярный вектор). .При решении прямоугольного треугольника по гипотенузе и катету код гипотенузы подается на кодовые шины входной переменной X, а код катета - на. кодовые шины переменной У. При этом на блок 5 умножения подается команда, запрещаюгдая выработку произведений вида . Хд COS (i и sin р, а ходы Y -и XQ проходят через блок 5 умножения транзитом. Работа cxeivw происходит в дальнейшем аналогично. Эффективность изобретения заклю чается в повышении быстродействия устройства при вычислении тригонометрических функций за счет увелич ния- скорости вычисления в ра где п - количество разрядов предст ления переменных. Формула изобретения - Устройство для вычисления функций, содержащее блок сдвига, блок умножителей и сумматор, причем пер вый и второй входы устройства соединены с первым и вторым входами блока сдвига, первый и второй вход cy Iмaтopa соединены с первым и вто рым выходами блока умножителей, а первый выход сумматора соединен с п вым выходом устройства, отличающееся тем, что, с целью повьниения быстродействия устройств

J

1о

/ оно дополнительно содержит коммутатор, сдвиговый регистр, накапливаю- . щий сумматор и блок выработки констаят, причем первый и второй входы коммутатора соединены соответственно с пер вым и вторым входами устройства,- а . выходы блока сдвига со.единены с третьим и четвертыми входами.коммутатора, первый и второй выходы коммутатора соединены соответственно с первым и вторым входами блока умножителей, пятый вход коммутатора соединен с третьим входом сумматора и вы-, ходом переноса сдвигового регистра, выход которогб соединен с первым входом накапливакяцего сумматора, выход которого соединен со вторым выходом устройства и входом блока выработки констант, первый и второй выходы которого соединены с третьим и четвертым входами блока умножителей, второй выход сумматора соединен со вторым входом накапливающего сумматора, а вход сдвигового регистра соединен с тактовым входом устройства.. - . Источники информации, принятые во внимание при экспертизе 1.Цифровые дифференциальные анализаторы. Под ред Б.Я. Когана, М.., ГИФНД, 1959, с. 205. 2.Авторское свидетельство СССР № 660059, кл. G 06 F 15/34, 1977 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления тригоно-МЕТРичЕСКиХ фуНКций | 1979 |

|

SU832555A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU983707A1 |

| Устройство для вычисления элементарных функций | 1983 |

|

SU1160454A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ МНОГОФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА В КОД ДЛЯ УСТРОЙСТВ ЭЛЕКТРОМЕХАНОТРОНИКИ | 1994 |

|

RU2094945C1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU955082A1 |

| Конвейерное устройство для вычисления тригонометрических функций | 1984 |

|

SU1168931A1 |

| Устройство для вычисления функций в модулярном коде | 1985 |

|

SU1278839A1 |

| Цифровой генератор колоколообразных функций | 1978 |

|

SU737936A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ | 2015 |

|

RU2602674C1 |

| Устройство для вычисления логарифмической функции | 1988 |

|

SU1596323A1 |

1

/1

f

Авторы

Даты

1981-04-23—Публикация

1978-12-22—Подача