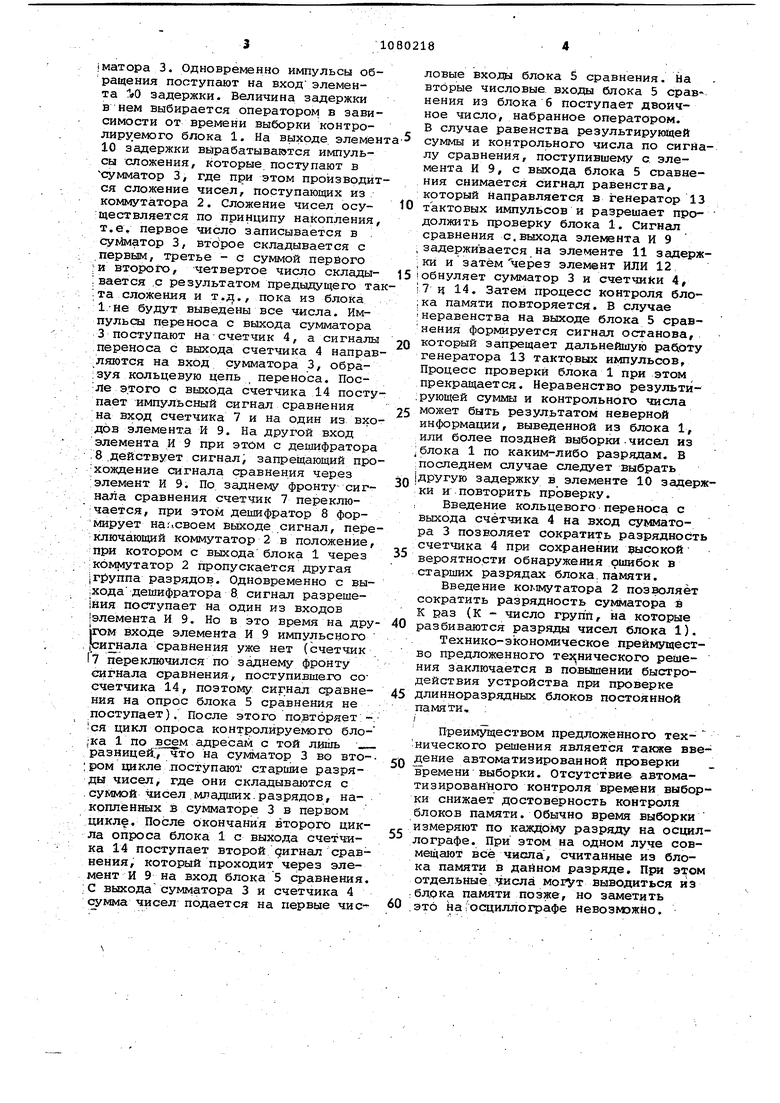

Изобретение относится к вычис. лительной технике и мсж.ет быть использовано при разработке, отладке и диагностике неисправностей запоминающих устройств. По основному авт. ев, № 858115 известно-устройство для контроля блоков постоянной памяти, содержащее сумматор, информационные входьт которого соединены с входами устройства, блок сравнения, первый вход которого соединен с тиной разрешения сравнения, блок установ ки контрольного двоичного числа, выходы которого подключены к одним из входов блока сравнения, информа ционные выходы сумматора соединены с другими входами блока сравнения, выход которого соединен.с выходом устройства, счетчик, вход которогр соединён с выходом переноса единиц сумматора, а выходы счетчика соединены с соответствующими входами бло ка сравнения l . Работа этого устройства основана на сложении многоразрядных чисел, считываемых из блока постоянной памяти. Единицы переполнения- при сложении поступают с выхода переноса старшего разряда сумматора в счетчик. После окончания сложения .всех чисел в блоке сравнения под действием сигнала сравнения осущест ляется сравнение результирующей суммы с контрольным двоичным числом .Если сумма совпадает с контрольным шслом, то вырабатывается сигнал сравнения и останов, Это устройство позволяет сЭбнаруживать многократные ошибки при неисправности в старших разрядах блока памяти. Вероятность обнаружения ошибки, зависит от количества разрядов с 5:етчика. Недостатком этого устройства является ограниченное быстродействие, обусловленное большим количеством разрядов сумматора и счетчика, вызванная этим повышенная трудоемкость набора контрольной суммы оператором повышенная вероятность ошибки оператора при Наборе контрольного числа, обусловленная многоразрядностью сумматора и счетчика, а также отсут ствие автоматизированного контроля времени выборки чисел (выполнение этого параметра требуется техническими условиями на блоки памяти). цель изобретения - повышение быс родействия путем сокращения разрядности сумматора и введения переноса с выхода счетчика на вход сумматора .и повышение достоверности . контроля блоков памяти путем автоматизации контроля времени выборки чисел из блоков памяти. Поставленная цель достигается тем, что в устройство для контроля блоков постоянной памяти введены последовательно соединенные счетчик адреса и генератор тактовых импульсов, вход которого подключен к выходу блока сравнения, коммутатор, элементы И и ИЛИ, элементы задержки, формирователь сигналов сброса, последовательно соединенные счетчик циклов и дешифратор, выход которого подключен к первому входу элемента И и управляющему входу коммутатора, выходы которого Соединены с одними из входов сумматора, другие входы которого подключены соответственно к одному из выходов счетчика и выходу перйого элемента задержки, вход которого подключен к выходу генератора тактовых импульсов, выход счетчика адреса, соединен с входом счетчика циклов и вторым входомэлемен,та И, вь1ход которого подключён непосредственно к входу блока сравнения, и через второй элемент; задержки к первому входу элемента ИЛИ, второй вход которого соединён с выходом формирователя сигналов сброса, а выход подключен к управляющим входам Сумматора и счетчиков. На чертеже изображена структур.ная схема устройства для контроля блоков постоянной па;мяти. Предложенное устройство, подключаемое к контролируемому блоку 1 постоянной памяти, содержит коммутатор 2, сумматор 3, счетчик 4, блок 5 сравнения, блок б установки контрольного двоичного числа, счетчик 7 циклов, дешифратор 8, элемент И 9, первый элемент 10 задержки, ис пользуемый в качествеузла контро- : ля времени выборки, второй элемент , 11 задержки/ элемент ИЛИ 12, генератор 13 тактовых импульсов, счетчик 14/адреса, формирователь 15 сигналов сброса, состоящий из кнопки 16 Пуск и триггера 17. Устройство работает следующим образом,„ Пуск устройства осуществляется оператором при нажатии кнопки 16 в формирователе. 15. Сигнал сброса через элемент ИЛИ 12 поступает на сумматор 3, счетчики 4,7 и 14. При этом с выхода дешифратора 8 на управляющий вход коммутатора 2 поступает сигнал, разрешающий прохождение через коммутатор 2 первой группы разрядов блока 1 на сумматор 3. При подаче на вход блока 1 последовательно изменяющегося кода ад-, реса со счетчика 14 и импульса обращения с выхода блока 1 первая группа разрядов считанного числа прохоит через коммутатор 2 на вход сум|матора 3. Одновременно импульсы обращения поступают на вход элемента лО задержки. Величина задержки в нем выбирается оператором в зависимости от времени выборки контролируемого блока 1. На выходе элемен 10 задержки вырабатываются импульсы сложения, которые поступают в сумматор 3, где при этом производит ся сложение чисел, поступающих из коммутатора 2. Сложение чисел осуществляется по принципу накопления т.е. первое число записывается в . сумматор 3, второе складывается с .первым, третье - с суммой первого ;и BTOpoiX), четвертое число склалыiвается .с результатом предыдущего та ; та сложения и т.., пока из блока 1.-не будут выведены все числа. Импульсы переноса с выхода сумматора 3 поступают на-счетчик 4, а сигналы переноса с выхода счетчика 4 направ ,ляются на вход сумматора 3, обра:зуя кольцевую цепь переноса. Пос-ле этого с выхода счетчика 14 посту пает импульсный сигнал сравнения на вход счетчика 7 и на один из вхо дов элемента И 9. На другой вход элемента И 9 при этом с дешифратора 8 .действует сигнал, запрещающий про хождение сигнала сравнения через :элемент И 9. По заднему фронту- сигнала сравнения счетчик 7 переклю:чается, при этом дешифратор 8 формирует наглсвоем выходе сигнал, пере ключающий коммутатор 2 в положение при котором с выхода блока 1 через Гкоммутатор 2 пропускается другая |riiynna разрядов. Одновременно с вы|ходадешифратора 8 сигнал разреше|ния поступает на один из входов Элемента И 9. Но в это время на дру jroM входе элемен а И 9 импульсного . сигнала сравнения уже нет (счетчик (7 переключился по заднему фронту сигнала сравнения, поступившего сосчетчика 14, поэтому сигнал сравнения на опрос блока 5 сравнения не поступает). После этого повторяет: ся цикл опроса контролируемого бло;ка 1 по всем адресам с той лишь - разницеС, что на сумматор 3 во вто:ром цикле .поступают старшие разряды чисел, где они складываются с .суммой чисел.младших разрядов, накопленных is сумматоре 3 в первом цикл. После окончания второго цикла опроса блока 1 с выхода счетчика 14 поступает второй дигнал срав нения, который проходит через элемент И 9 на вход блока 5 сравнения :С выходасумматора 3 и счетчика 4 сумма чисел подается на первые числовые входы блока 5 сравнения. На вторые числовые входы блока 5 сравнения из блока б поступает двоичное число, набранное оператором. В случае равенства результирующей суммы и контрольного числа по сигналу сравнения, поступившему с. элемента И 9, с выхода блока 5 сравнения снимается оигна равенства, который Направляется в генератор 13 тактовых импульсов и разрешает продолжить проверку блока 1. Сигнал сравнения с,выхода элемента И 9 задерживается на элементе 11 задержки и затем через элемент ИЛИ 12, обнуляет сумматор 3 и счетчики 4, 7 и 14. Затем процесс контроля блока памяти повторяется. В случае неравенства на выходе блока 5 сравнения формируется сигнал останова, который запрещает дальнейшую раб1оту генератора 13 тактовых импульсов, Процесс проверки блока 1 при этом прекращается. Неравенство результирующей суммы и контрольного числа может быть результатом неверной информации, выведенной из блока 1, или более поздней выборкичисел из .блока 1 по каким-либо разрядам. В последнем случае следует выбрать другую задержку в элементе 10 задержки и повторить проверку. Введение кольцевого переноса с выхода счётчика 4 на вход сумматора 3 позволяет сократить разрядность счетчика 4 при сохранении высокой вероятности обнаружения ошибок в старших разрядах блока. памяти. Введение коммутатора 2 позволяет сократить разрядность сумматора в К раз (К - число групп, на которые разбиваются разряды чисел блока 1). Технико-экономическое преимущество предложенного технического решения заключается в повышении быстродействия устройства при проверке длинноразр адных блоков постоянной памяти, :. Преимуществом предложенного технического решения является также введение автоматизированной проверки времени выборки. Отсутствие автоматизированного контроля времени выборки снижает достоверность контроля блоков памяти. Обычно время выборки измеряют по каждому разряду на осциллографе. При этом на одном луче совмещают всё числа , считанные из блока памяти в данном разряде. При отдельные.исла могут выводиться из :блока памяти позже, но заметить это йа(осциллографе невозмэжно.

i

Г5

/4

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2018 |

|

RU2708956C2 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР | 2009 |

|

RU2417409C2 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для исправления ошибок | 1990 |

|

SU1783622A1 |

ЕИ

Ч

/5 -//им1

сбоос

/7

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля блоков постоянной памяти | 1979 |

|

SU858115A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| св | |||

| Устройство для контроля блоков постоянной памяти | 1979 |

|

SU858115A1 |

Авторы

Даты

1984-03-15—Публикация

1983-01-10—Подача