1

Изобретение относится к вычислительной технике и может найти применение в специализирован1а1х процессорах решающих задачи цифровой фильтрации и спектрального анализа при обработке сейсморазведочной информации.

Известен спецпроцессор СКИФ, содержащий адресное устройство, включающее суммирующее устройство, регистры и коммутаторы адресов и индексов О .

Недостатком этого устройства является иизкая скорость вычисления адресов массива назначения при трансляции и использовании дополнительной области памяти для таблицы индексов .

Наиболее близким техническим решением к предлагаемому является а дресное устройство специализированного процессора СП-М222, содержащее сумматор , регистры адресов, регистры ин ексов, коммутаторы адресов и индексов 2 . ,

Однако в этом спецпрйцессоре при трансляции массивов для вычисления текущих адресов массива назначения индексы, для каждого операнда, подсум мируемые к начальному адресу, считываются из оперативного ЗУ, на что затрачивается время, равное времени чтения из оперативного ЗУ данных исходного массива. Кроме того, для размещения индексов в оперативном ЗУ требуется дополнительная область памяти, равная объему памяти для массива назначения.

Цель изобретения - повышение быстродействия устройства при трансляции массивов данных.

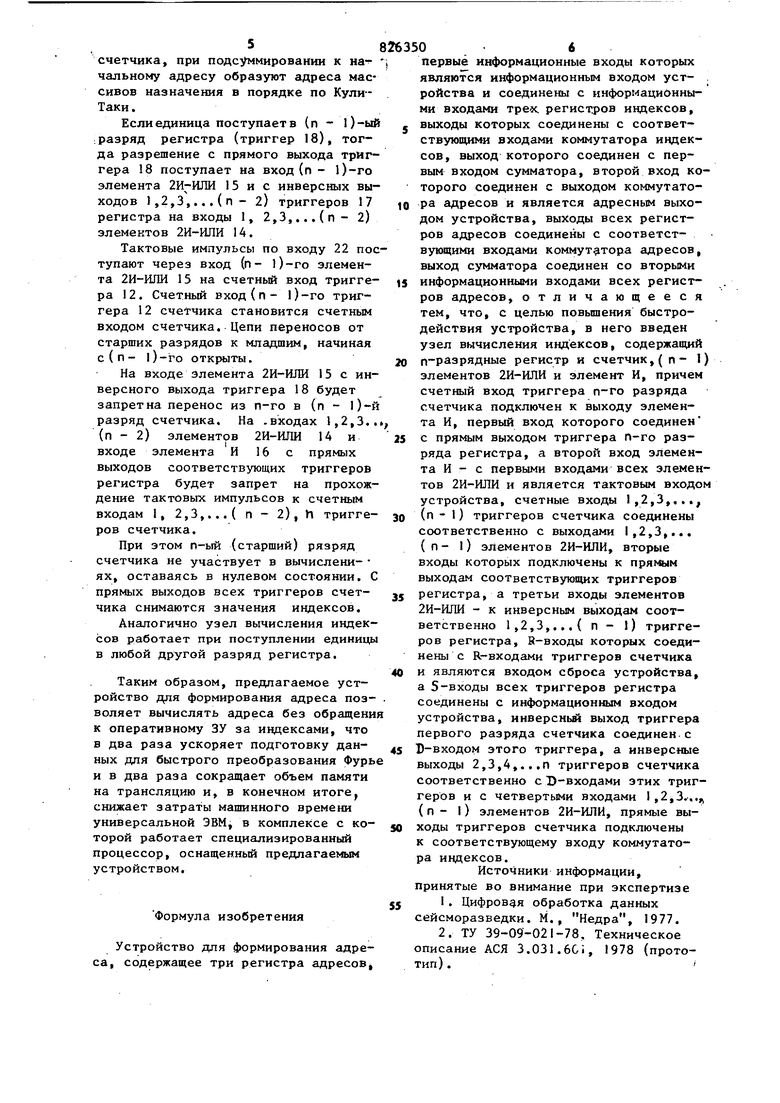

Поставленная цепь достнгается тем, что в устройство для формирования адреса, содержащее три регистра адресов, первые информационные входы которых являются информационным входом устройства и соединены с информационными входами трех регистров индексов, выходы которых соединены с соответствующими входами коммутатора индексов, выход которого соединен с первым входом сумматора, второй вход которого соединен с выходом коммутатора адресов и является адресным выходом устройства, выходы всех регистров адресов соединены с соответствукйцими входами коммутатора адресов, выход сумматора соединен со вторыми информационными входами всех регистров адресов, введен узел вычисления индексов, содержащий п-разрядные регистр и счетчик Л - 1 ) элементов 2И-ИЛИ и элемент И, причем счетный вход триггера п-го разряда счетчика подключен к выходу элемента И, первый вход которого соединен с прямым выходом триггера п-го разряда регистра, а второй вход - с первыми входами всех элементов 2ИИЛИ и является тактовым входом устройства, счетные входы 1,2,3,...(птриггеров счетчика соединены соответ ственно с выходами J,2,3,...(n- 1) элементов 2И-ИЛИ, вторые входы которых подключены к пря(1м выходам соот ветствующих триггеров регистра, а третьи входы - к инверсным выходам соответственно i,2,3,.,.(n - l) триг геров регистра, Ц-входы которых соединены с R-входами триггеров счетчика и являются входом сброса устройст ва, а S -входь всех триггеров регист ра соединены с информационным входом устройства, инверсный выход триггера первого разряда счетчика соединен с -входом этого триггера, а инверсные выходы 2,3,4,,..п триггеров счетчика соответственно с D-входами этих триггеров и с четвертыми входами 1,2,3.,...(п - 1) элементов 2И-ИЛИ, прямые выходы триггеров счетчика под ключены к соответствующему входу ком мутатора индексов. На чертеже изображено устройство для формирования адреса. Устройство ДЛЯ формирования адреса включает сумматор 1, регистры 2-А адресов, регистры 5-7 индексов, коммутаторы адресов 8 и индексов 9 и узел Ю вычисления индексов, который содержит триггеры 11-13 счетчика, (п - ) элементов 2И-ИЛИ 14 и 15, эле мент И 16, h триггеров 17-19 регист ра. К устройству для формирования адреса подводятся: вход 20 из устройст ва ввода-вывода спецпроцессора, по 504 которому передаются в регистры 2-4 адресов коды начальных адресов массивов, в регистры 5-7 индексов - ко-v ды индексов, и в узел 10 вычисления индексов - код длины массива назначения; выход 21, по которому передаются текущие адреса из регистров 2-4 адресов через коммутатор 8 адресов в оперативное запоминающее устройство; тактовый взюд 22, вход 23 сброса. Узел вычисления индексов работает следующим образом. Перед началом работы устройства счетчик и регистр узла вычисления индексов обнуляются сигналом, поступающим по входу 23 из устройства уп;равления спецпроцессора. Затем по входу 20 подается на S-входы регистра код в виде единицы в п-ом разряде ( i - показатель степени, 2 длина массива назначения, которая является исходным массивом для быстрого преобразования Фурье, например, когда длина массива равна 16, 4 и код, поступающий на S -вхо- ды регистра, содержит единицу в четвертом разряде), которая фиксируется в 1-ом разряде регистра. При максимальной длине массива назначения (i п) единица фиксируется в (старшем) разряде регистра (триггер 19) и разрешение с прямого выхода триггера 19 поступает на вход элемента И 16, Это позволяет тактовым импульсам проходить по входу 22 из устройства управления спецпроцессора через элемент И 16 на счетный вход триггера 13 П-го (старшего) разряда счетчика, Таким образом,- счетный вход счетчика определяется длиной массива назначения один раз в начале операции. С прямых выходов остальных триггеров 17 и 18 регистра поступает запрет на вторые входы, а с инверсных выходов - разрешегше на входы элементов 2И-ИЛИ, благодаря чему на счетные входы 1,2,3,,..(п- l) триггеров II и 12 счетчика поступают сигналы переносов от старших к младшим разрядам счетчика (от инверсных выходов триггеров 12 и 13 на четвертые входы элементов 2И-ИЛИ 14 и J5). С прямых выходов триггеров счетчика после каждого тактового импульса передается необходимый индекс в сумматор 1 через коммутатор 9 индексов. Индексы, получаемые на выходе

чальному адресу образуют адреса массивов назначения в порядке по КулиТаки.

Если единица поступает в (п - 1)-ый разряд регистра (триггер 18), тогда разрешение с прямого выхода триггера 18 поступает на вход (п - 1)-го элемента 2И-ИЛИ 15 и с инверсных выходов 1,2,3,...(п- 2) триггеров 17 регистра на входы 1, 2,3,...(п- 2) элементов 2И-ИЛИ 14.

Тактовые импульсы по входу 22 поступают через вход (п - 1)-го элемента 2И-ИЛИ 15 на счетньй вход триггера 12. Счетный вход ( п- О-го триггера 12 счетчика становится счетным входом счетчика. Цепи переносов от старших разрядов к младшим, начиная с(п- |)-го открыты. На входе элемента 2И-ИЛИ 15 с инверсного выхода триггера 18 будет запретна перенос из п-го в (п - 1)-й разряд счетчика. На .входах 1,2,3. (п - 2) элементов 2И-ИЛИ 14 и входе элемента И 16 с прямых выходов соответствующих триггеров регистра будет запрет на прохождение тактовых импульсов к счетным входам 1, 2,3,...( п - 2), h триггеров счетчика. При этом п-ый (старший) рязряд счетчика не участвует в вычислени- ях, оставаясь в нулевом состоянии. С прямых выходов всех триггеров счетчика снимаются значения индексов. Аналогично узел вычисления индексов работает при поступлении единицы в любой другой разряд регистра. Таким образом, предлагаемое устройство для формирования адреса позволяет вычислять адреса без обращени к оперативному ЗУ за индексами, что в два раза ускоряет подготовку данных для быстрого преобразования Фурь и в два раза сокращает объем памяти на трансляцию и, в конечном итоге, снижает затраты машинного времени универсальной ЭВМ, в комплексе с которой работает специализированный процессор, оснащенный предлагаемым устройством. Формула изобретения Устройство для формирования адреса, содержащее три регистра адресов

являются информационным входом уст- , ройства и соединены с информационными входами трех, регистров индексов,

выходы которых соединены с соответствующими входами коммутатора индексов, выход которого соединен с первым входом сумматора, второй вход которого соединен с выходом коммутатора адресов и является адресным выходом устройства, выходы всех регистров адресов соединены с соответствующими входами коммутатора адресов, выход сумматора соединен со вторыми информационными входами всех регистров адресов, отличающееся тем, что, с целью повьш1ения быстродействия устройства, в него введен узел вычисления индексов, содержащий п-разрядные регистр и счетчик, (п- 1) элементов 2И-ИЛИ и элемент И, причем счетный вход триггера п-го разряда счетчика подключен к выходу элемента И, первый вход которого соединен с прямым выходом триггера п-го разряда регистра, а второй вход элемента И - с первыми входами всех элементов 2И-ИЛИ и является тактовым входом устройства, счетные входы 1,2,3,..., (п - 1) триггеров счетчика соединены соответственно с выходами 1,2,3,,.. ( п- О элементов 2И-ИЛИ, вторые входы которых подключены к прямым выходам соответствуюпщх триггеров регистра, а третьи входы элементов 2И-ИЛИ - к инверсным выходам соответственно 1,2,3,...( п - 1) триггеров регистра, 8-входы которых соединены с R-входами триггеров счетчика и являются входом сброса устройства, а S-входы всех триггеров регистра соединены с информационным входом устройства, инверсньй выход триггера первого разряда счетчика соединен с Г-входом этого триггера, а инверсные выходы 2,3,4,...п триггеров счетчика соответственно с D-входами этих триггеров и с четвертыми входами I ,2,3.-.,, (п - I) элементов 2И-ИЛИ, прямые выходы триггеров счетчика подключены к соответствующему входу коммутатора индексов. Источники информации, принятые во внимание при экспертизе 1.Цифровая обработка данных сейсморазведки. М., Недра, 1977. 2.ТУ 39-09-021-78, Техническое описание АСЯ 3.031.6Gi, 1978 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Устройство адресации | 1987 |

|

SU1418712A1 |

| Устройство управления процессора двухмерного преобразования Фурье | 1982 |

|

SU1121677A1 |

| Устройство для преобразования контролируемых параметров | 1986 |

|

SU1320816A1 |

| Устройство управления для процессора быстрого преобразования Фурье | 1984 |

|

SU1270775A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Медианный фильтр | 1988 |

|

SU1562902A1 |

| Функциональный преобразователь | 1987 |

|

SU1481750A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| Конвейерное устройство для вычисления функции Y=е @ | 1981 |

|

SU962927A1 |

Авторы

Даты

1981-04-30—Публикация

1979-08-07—Подача