С/)

С

Изобретение относится к вычисли- л вльной технике и может быть исполь- |3овано при построении устройств фор- |Мирования адресов данных в универсал :Кык и специализированных вычислительных машинах.

Целью изобретения является расши- рение функциональных возможностей за счет обеспечения двоично-разрядной инверсии адр.есов, необходимой При реализации алгоритмов БПФ.

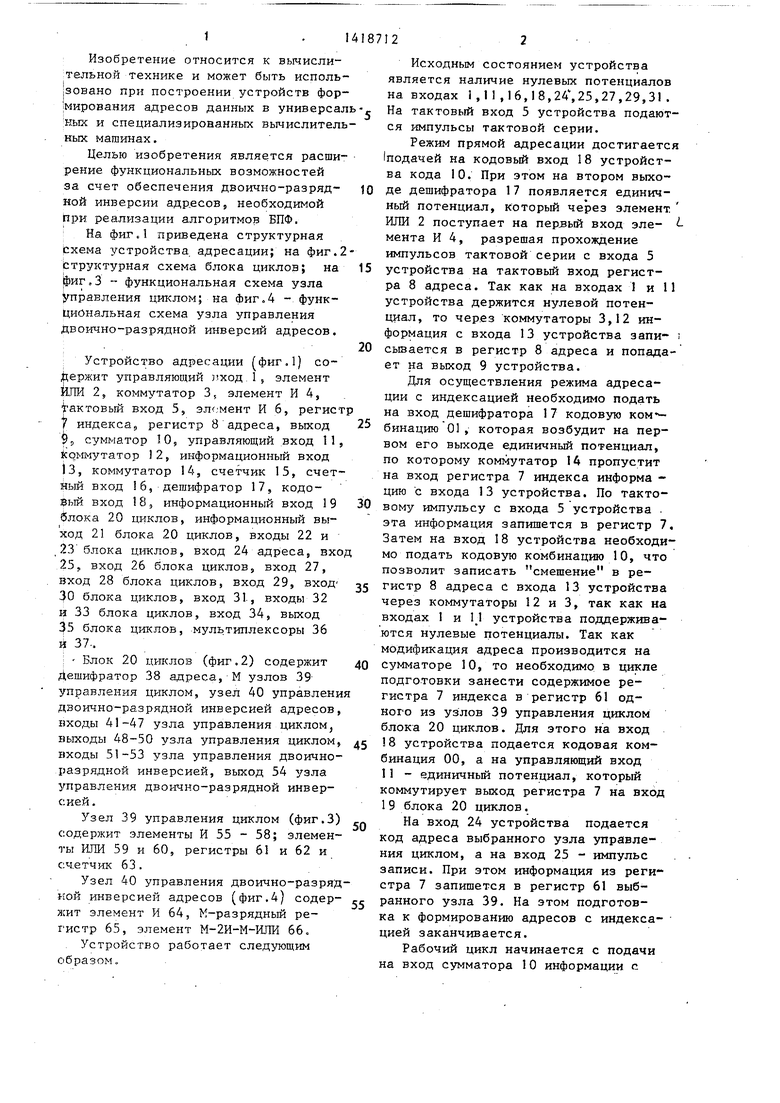

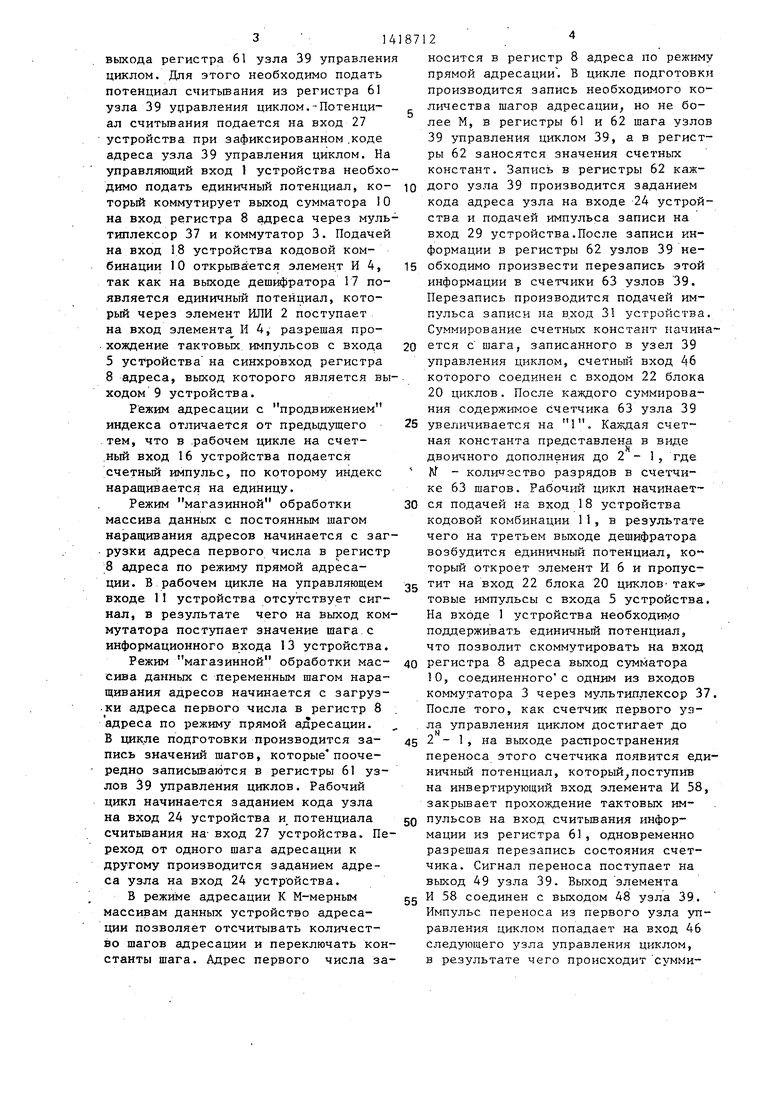

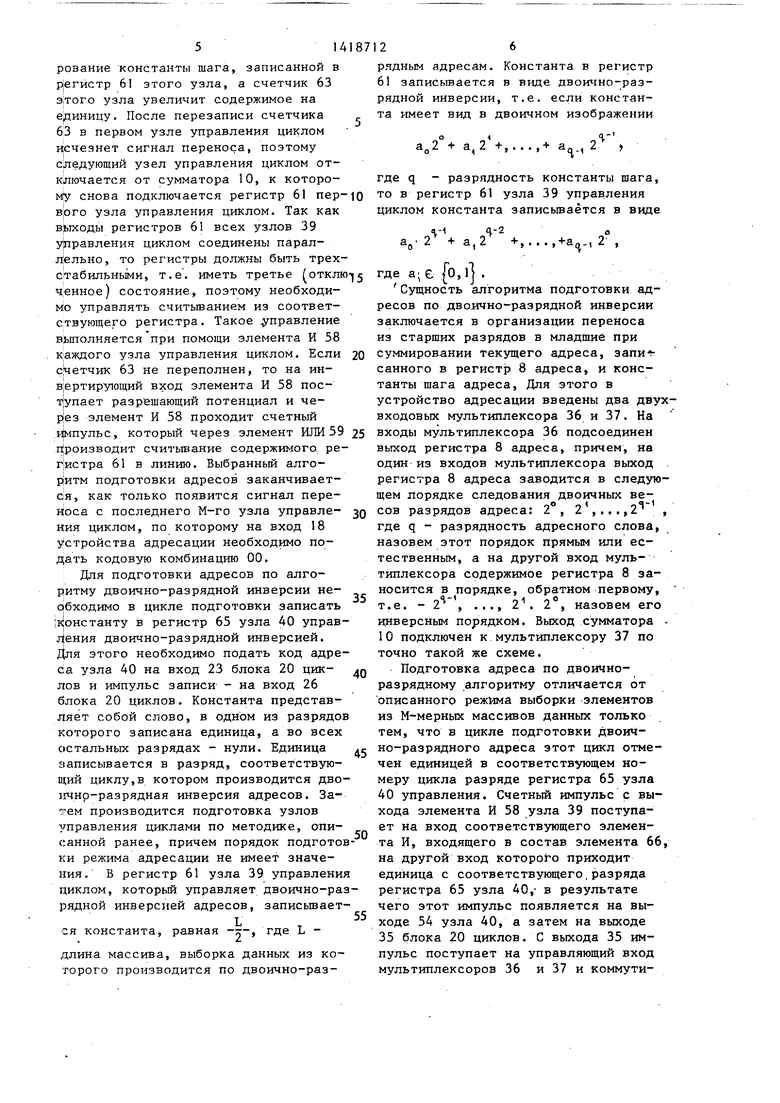

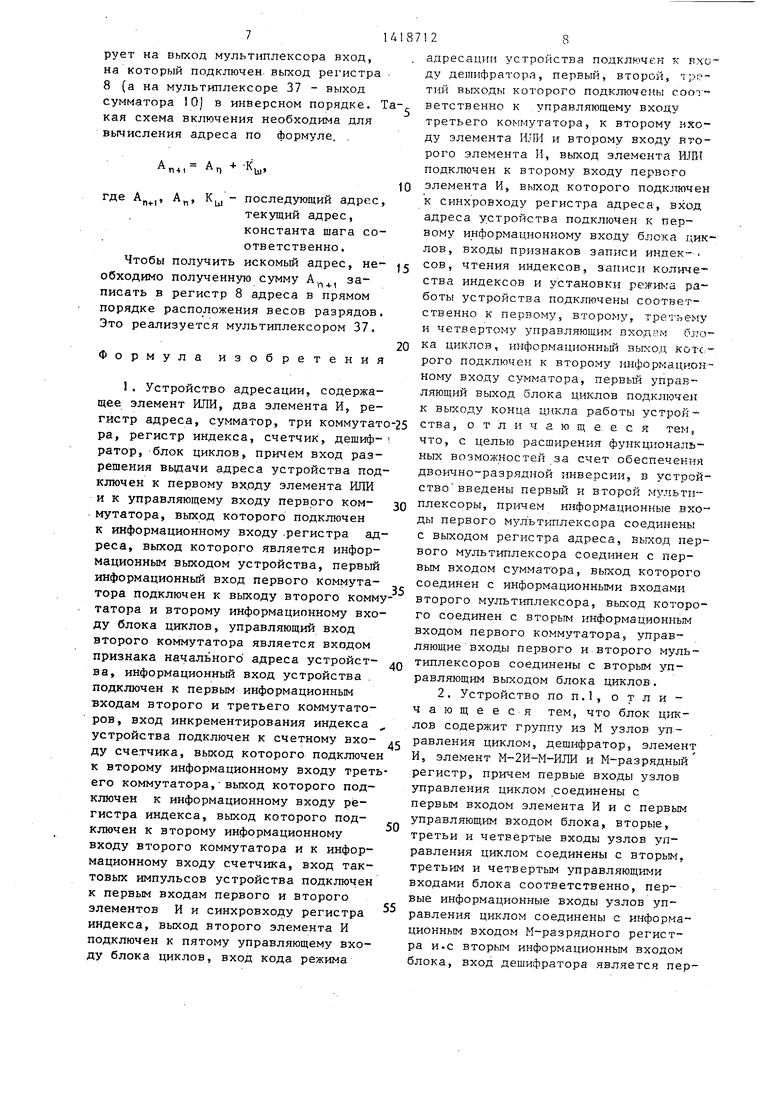

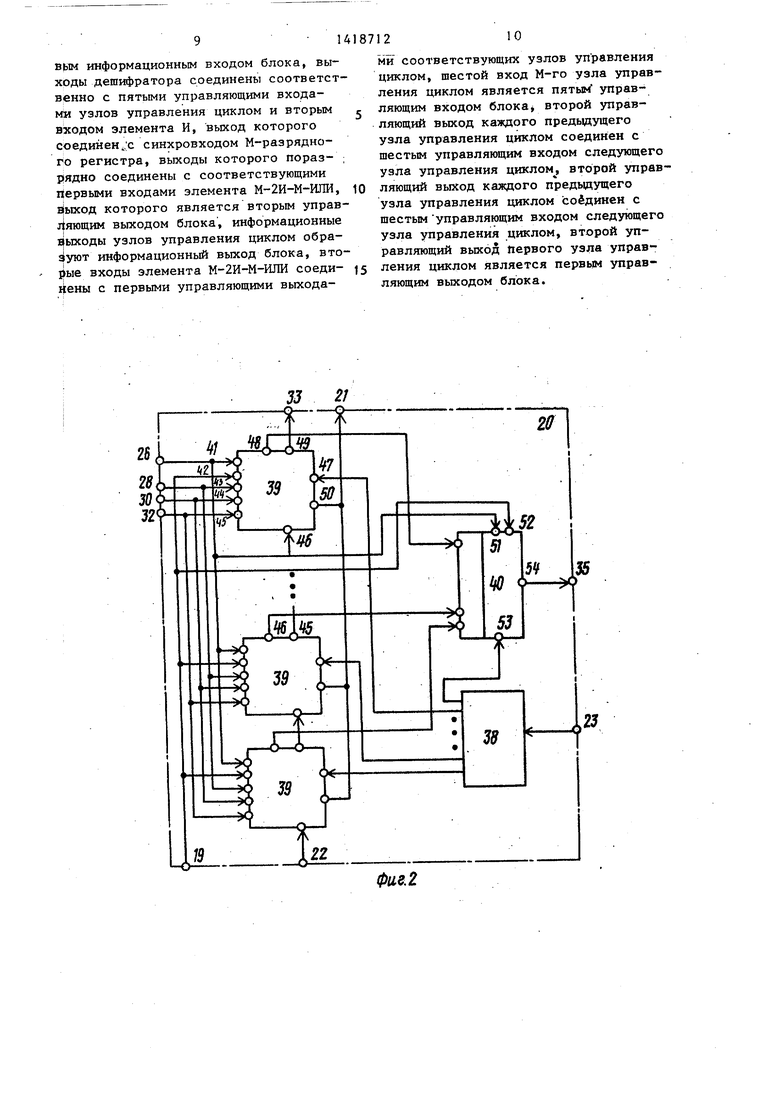

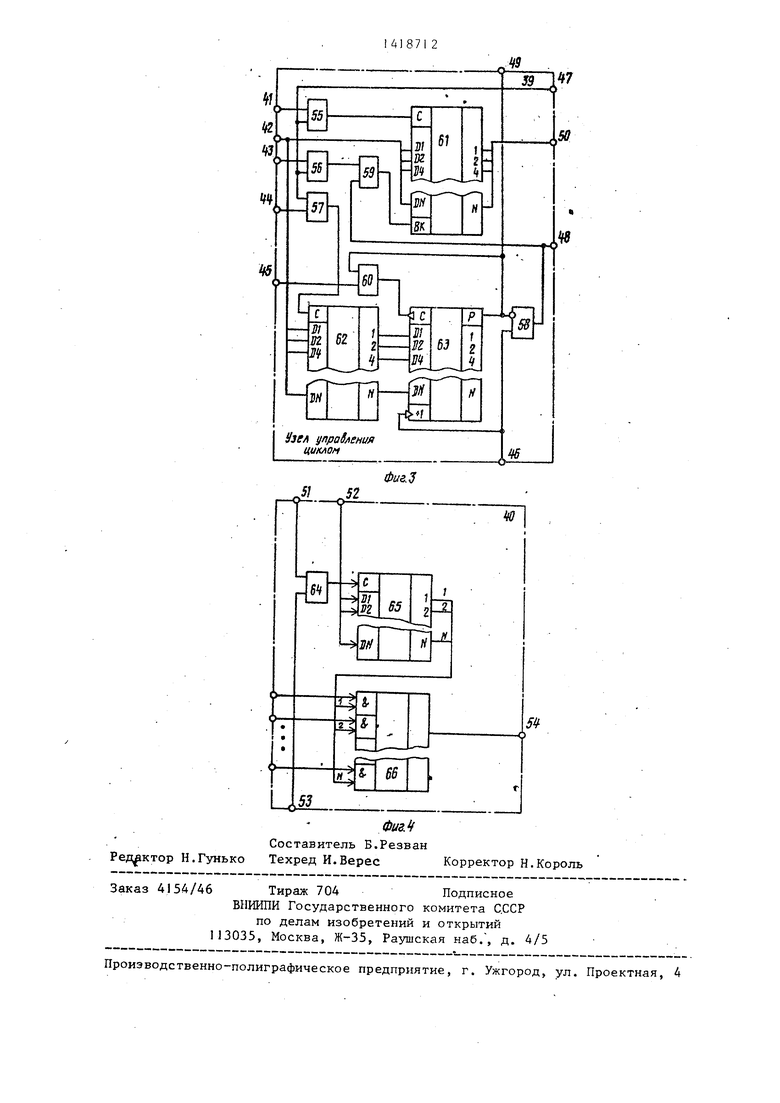

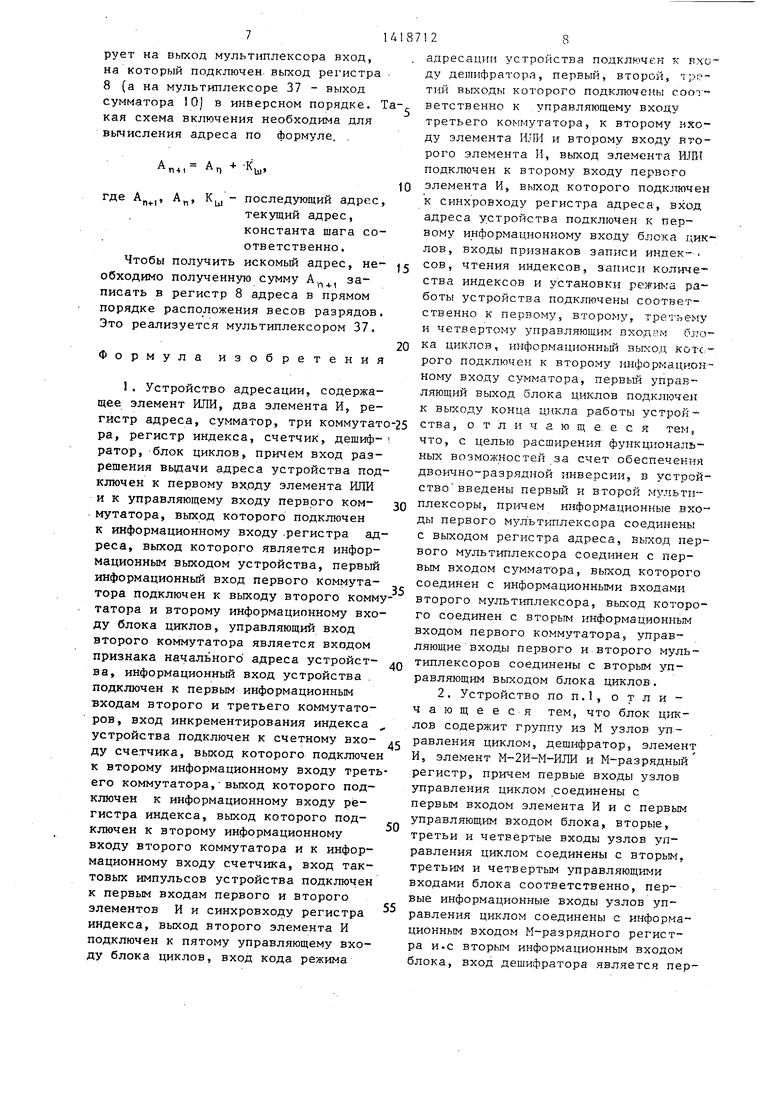

На фиг.1 приведена структурная схема устройства, адресации; на фиг.2 Структурная схема блока циклов; на фиг, 3 -- функциональная схема узла управления циклом; на фиг.4 -.функциональная схема узла управления Двоично-разрядной инверсий адресов.

: Устройство адресации (фиг,1) содержит управляющий ) ход, 1 , элемент ИЛИ 2, коммутатор 3, элемент И 4, актовый вход 5, эл(;мент И 6, регист t индексва регистр 8 адреса, вькод 95 сумматор 10, управляющий вход 11, Коммутатор 2,, информационный вход |3, коммутатор 14, счетчик 15, счетный вход 16, дешифратор 17, кодовый вход 18j информационный вход 19 блока 20 циклов, информационный выход 21 блока 20 циклов, входы 22 и ,23 блока циклов, вход 24 адреса, вхо 25., вход 26 блока циклов, вход 27, вход 28 блока циклов, вход 29, вход- 30 блока циклов, вход 31-, входы 32 и 33 блока циклов, вход 34, выход 35 блока циклов, мультиплексоры 36 и 37..

; Блок 20 циклов (фиг.2) содержит Дешифратор 38 адреса, М узлов 39- управления циклом, узел 40 управлени двоично-разрядной инверсией адресов, входы 41-47 узла управления циклом, выходы 48-50 узла управления циклом, входы 51-53 узла управления двоично- разрядной инверсией, выход 54 узла управления двоично-разрядной инверсией.

З зел 39 управления циклом (фиг.З) содержит элементы И 55 - 58; элементы ИЛИ 59 и 60, регистры 61 и 62 и счетчик 63.

Узел 40 управления двоично-разрядной инверсией адресов (фиг.4) содержит элемент И 64, М-разрядный регистр 65, элемент М-2И-М-ИЛИ 66. . Устройство работает следующим образом.

5

Исходным состоянием устройства является наличие нулевых потенциалов на входах 1 ,1 1 ,1 6,1 8, 24,25,27,29,31 .

j На тактовый вход 5 устройства подаются импульсы тактовой серии.

Режим прямой адресации достигается 1подачей на кодовый вход 18 устройства кода 10. При этом на втором выхо0 де дешифратора 17 появляется единич- ый потенциал, который через элемент ИЛИ 2 поступает на вход эле- i- мента И 4, разрешая прохождение импульсов тактовой серии с входа 5

5 устройства на тактовый вход регистра 8 адреса. Так как на входах 1 и 11 устройства держится нулевой потенциал, то через коммутаторы 3,12 информация с входа 13 устройства запи- i

0 сьгвается в регистр 8 адреса и попадает на выход 9 устройства.

Для осуществления режима адресации с индексацией необходимо подать на вход дешифратора 17 кодовую бинациго 01, которая возбудит на первом его выходе единичный потенциал, по которому коммутатор I4 пропустит на вход регистра 7 индекса информа - цию с входа 13 устройства. По такто0 вому импульсу с входа 5 устройства . эта информация запишется в регистр 7, Затем на вход 18 устройства необходимо подать кодовую комбинацию 10, что позволит записать смешение в ре5 гистр 8 адреса с входа 13 устройства через коммутаторы 12 и 3, так как на входах 1 и 1J устройства поддерживаются нулевые потенциалы. Так как модификация адреса производится на

0 сумматоре 10, то необходимо в цикле подготовки занести содержимое регистра 7 индекса в регистр 61 одного из узлов 39 управления циклом блока 20 циклов. Для этого на вход

5 8 устройства подается кодовая комбинация 00, а на управляющий вход 11 - единичньй потенциал, который коммутирует выход регистра 7 на вход 19 блока 20 циклов.

На вход 24 устройства подается код адреса выбранного узла управления циклом, а на вход 25 - импульс записи. При этом информация из регистра 7 запишется в регистр 61 выб5 ранного узла 39. На этом подготовка к формированию адресов с индексацией заканчивается.

Рабочий цикл начинается с подачи на вход сумматора 10 информации с

0

3 14 выхода регистра 61 узла 39 управлени циклом. Для этого необходимо подать потенциал считывания из регистра 61 узла 39 управления циклом.-Потенци- ал считьшания подается на вход 27 устройства при зафиксированном .коде адреса узла 39 управления циклом. На управляющий вход 1 устройства необходимо подать единичный потенциал, ко- торый коммутирует выход сумматора 10 на вход регистра 8 адреса через мультиплексор 37 и коммутатор 3. Подачей на вход 18 устройства кодовой комбинации 10 открыва ется элемент И 4, так как на выходе дешифратора 17 появляется единичный потенциал, который через элемент ИЛИ 2 поступает на вход элемента И 4, разрешая про- хождение тактовых импульсов с входа 5 усттзойства на синхровход регистра 8 адреса, выход которого является выходом 9 устройства.

Режим адресации с продвижением индекса отличается от предьщущего .тем, что в .рабочем цикле на счет- .ный вход 16 устройства подается счетньш импульс, по которому индекс наращивается на единицу.

Режим магазинной обработки массива данных с постоянным шагом наращивания адресов начинается с заг рузки адреса первого числа в регистр 8 адреса по режиму прямой адресации. В рабочем цикле на управляющем входе 11 устройства отсутствует сигнал, в результате чего на выход коммутатора поступает значение шага.с информационного входа 13 устройства.

Режим магазинной обработки мае- сива данных с переменным шагом наращивания адресов начинается с загруз- .ки адреса первого числа в регистр 8 адреса по режиму прямой адресации. В цикле подготовки производится за- пись значений шагов, которые поочередно записьтаются в регистры 61 узлов 39 управления циклов. Рабочий цикл начинается заданием кода узла на вход 24 устройства и потенциала считьшания на- вход 27 устройства. Переход от одного шага адресации к другому производится заданием адреса узла на вход 24 устройства.

В режиме адресации К М-мерным массивам данных устройство адресации позволяет отсчитывать количество шагов адресации и переключать константы шага. Адрес первого числа за12 . 4

носится в регистр 8 адреса по режиму прямой адресации. В цикле подготовки производится запись необходимого количества шагор адресации, но не более М, в регистры 61 и 62 шага узлов 39 управления циклом 39, а в регистры 62 заносятся значения счетных констант. Запись в регистры 62 каждого узла 39 производится заданием кода адреса узла на входе -24 устройства и подачей импульса записи на вход 29 устройства.После записи информации в регистры 62 узлов 39 необходимо произвести перезапись этой информации в счетчики 63 узлов 39. Перезапись производится подачей импульса записи па вход 31 устройства Суммирование счетных констант начинается с шага, записанного в узел 39 управления циклом, счетньш вход 46 которого соединен с входом 22 блока 20 циклов. После каждого суммирования содержимое счетчика 63 узла 39 увеличивается на 1. Каждая счетная константа представлена в ыаде двоичного дополнения до 2 - 1, где - количество разрядов в счетчике 63 шагов. Рабочий цикл начинается подачей на вход 18 устройства кодовой комбинации 11, в результате чего на третьем выходе дешифратора возбудится единичньш потенциал, ко торый откроет элемент И 6 и пропустит на вход 22 блока 20 циклов так- товые импульсы с входа 5 устройства. На входе 1 устройства необходимо поддерживать единичньш потенциал, что позволит скоммутировать на вход регистра 8 адреса выход сумматора 10, соединенного с одним из входов коммутатора 3 через мультиплексор 37 После того, как счетчик первого узла управления циклом достигает до 2 - 1 , на выходе расттространения переноса этого счетчика появится единичный потенциал, который,поступив на инвертирующий вход элемента И 58, закрывает прохождение тактовых импульсов на вход считьшания информации из регистра 61, одновременно разрешая перезапись состояния счетчика. Сигнал переноса поступает на выход 49 узла 39. Выход элемента И 58 соединен с выходом 48 узла 39. Импульс переноса из первого узла управления циклом попадает на вход 46 следующего узла управления циклом, в результате чего происходит суммирование константы шага, записанной в регистр 61 этого узла, а счетчик 63 э;того узла увеличит содержимое на единицу. После перезаписи счетчика 63 в первом узле управления циклом исчезнет сигнал переноса, поэтому следующий узел управления циклом отключается от сумматора 10, к которо- Ну снова подключается регистр 61 пер-ю врго узла управления циклом. Так как в.гходы регистров 61 всех узлов 39 у|правления циклом соединены парал- 1{ельно, то регистры должны быть трех- стабильньми, т.е. иметь третье отклю ченное) состояние, поэтому необходимо управлять считыванием из соответствующего регистра. Такое .управление въшолняется при помощи элемента И 58 К;аждого узла управления циклом. Если 20 сметчик 63 не переполнен, то на ин- в;ертирующий вход элемента И 58 пос- т;упает разрешающий потенциал и че- pie3 элемент И 58 проходит счетный i-ft fflynbc, который через элемент ИЛИ 59 25 йроизводит считьшание содержимого ре- г)истра 61 в линию. Выбранньй алго- р:итм подготовки адресов заканчивает- dH, как только появится сигнал переноса с последнего М-го узла управле- зо ния циклом, по которому на вход 18 Устройства адресации необходимо подать кодовую комбинацию 00.

Для подготовки адресов по алгоритму двоично-разрядной инверсии необходимо в цикле подготовки записать |к|онстанту в регистр 65 узла 40 управления двоично-разрядной инверсией. Для этого необходимо подать код адре- Са узла 40 на вход 23 блока 20 цик- Q лов и импульс записи - на вход 26 блока 20 циклов. Константа представляет собой слово, в одном из разрядов которого записана единица, а во всех остальных разрядах - нули. Единица ,г записывается в разряд, соответствую- пций циклу,в котором производится дво- 1гчнр-разрядная инверсия адресов. Затем производится подготовка узлов управления циклами по методике, описанной ранее, причем порядок подготовки режима адресации не имеет значения. В регистр 61 узла 39 управления циклом, который управляет двоично-разрядной инверсией адресов, записьюаетL.55

оя константа, равная п, где L длина массива, выборка данных из которого производится по двоично-раз14187126

рядным адресам. Константа в регистр 61 записьшается в виде двоично-разрядной инверсии, т.е. если константа имеет вид в двоичном изображении

а„2 + а,2 +,

Я-

35

где q - разрядность константы шага, то в регистр 61 узла 39 управления циклом константа записьшается в виде

ам а-2о

а,- 2 + а,2 +,...,, 2 ,

где а;е O,l .

Сущность алгоритма подготовки адресов по дво.ично-разрядной инверсии заключается в организации переноса из старших разрядов в младшие при суммировании текущего адреса, запи санного в регистр 8 адреса, и константы шага адреса. Для этого в устройство адресации введены два дву входовых мультиплексора 36 и 37. На входы мультиплексора 36 подсоединен выход регистра 8 адреса, причем, на один из входов мультиплексора выход регистра 8 адреса заводится в следую щем порядке следования двоичных весов разрядов адреса: 2°, 2..,,2 где q - разрядность адресного слова, назовем этот порядок прямым или естественным, а на другой вход мультиплексора содержимое регистра 8 заносится в порядке, обратном первому, т.е. -2 , ..., 2 2°, назовем его инверсным порядком. Выход сумматора 10 подключен к мультиплексору 37 по точно такой же схеме.

Подготовка адреса по двоично- разрядному алгоритму отличается от описанного режима выборки -элементов из М-мерных массивов данных только тем, что в цикле подготовки двоично-разрядного адреса этот цикл отмечен единицей в соответствующем номеру цикла разряде регистра 65 узла 40 управления. Счетный импульс с выхода элемента И 58 узла 39 поступает иа вход соответствующего элемента И, входящего в состав элемента 66 на другой вход которого приходит единица с соответствующего,разряда регистра 65 узла 40,- в результате чего этот импульс появляется на выходе 54 узла 40, а затем на выходе 35 блока 20 циклов. С выхода 35 импульс поступает на управляющий вход мультиплексоров 36 и 37 и коммутиа„2 + а,2 +,

Я-

0 5 о

Q г

5

5

где q - разрядность константы шага, то в регистр 61 узла 39 управления циклом константа записьшается в виде

ам а-2о

а,- 2 + а,2 +,...,, 2 ,

где а;е O,l .

Сущность алгоритма подготовки адресов по дво.ично-разрядной инверсии заключается в организации переноса из старших разрядов в младшие при суммировании текущего адреса, запи санного в регистр 8 адреса, и константы шага адреса. Для этого в устройство адресации введены два двух- входовых мультиплексора 36 и 37. На входы мультиплексора 36 подсоединен выход регистра 8 адреса, причем, на один из входов мультиплексора выход . регистра 8 адреса заводится в следующем порядке следования двоичных весов разрядов адреса: 2°, 2..,,2 , где q - разрядность адресного слова, назовем этот порядок прямым или естественным, а на другой вход мультиплексора содержимое регистра 8 заносится в порядке, обратном первому, т.е. -2 , ..., 2 2°, назовем его инверсным порядком. Выход сумматора - 10 подключен к мультиплексору 37 по точно такой же схеме.

Подготовка адреса по двоично- разрядному алгоритму отличается от описанного режима выборки -элементов из М-мерных массивов данных только тем, что в цикле подготовки двоично-разрядного адреса этот цикл отмечен единицей в соответствующем номеру цикла разряде регистра 65 узла 40 управления. Счетный импульс с выхода элемента И 58 узла 39 поступает иа вход соответствующего элемента И, входящего в состав элемента 66, на другой вход которого приходит единица с соответствующего,разряда регистра 65 узла 40,- в результате чего этот импульс появляется на выходе 54 узла 40, а затем на выходе 35 блока 20 циклов. С выхода 35 импульс поступает на управляющий вход мультиплексоров 36 и 37 и коммути714187

рует на выход мультиплексора вход, на который подключен выход регистра 8 (а на мультиплексоре 37 - выход сумматора 10) в инверсном порядке. Такая схема включения необходима для вычисления адреса по формуле. .

А,

А„ К,,,,

ы

где А,, А„, KIJ - последующий адрес,

текущий адрес, константа шага соответственно.

Чтобы получить искомый адрес, не- обходимо полученную сумму А., записать в регистр 8 адреса в прямом порядке расположения весов разрядов. Это реализуется мультиплексором 37,

Формула изобретения

1. Устройство адресации, содержащее элемент ИЛИ, два элемента И, регистр адреса, сумматор, три коммутато ра, регистр индекса, счетчик, дешифратор, блок циклов, причем вход разрешения вьщачи адреса устройства подключен к первому вх.оду элемента РШИ и к управляющему входу первого коммутатора, выход которого подключен к информационному входу .регистра адреса, выход которого является информационным выходом устройства, первый информационный вход первого коммутатора подключен к выходу второго комму татора и второму информационному входу блока циклов, управляющий вход второго коммутатора является входом признака начального адреса устройства, информационный вход устройства . подключен к первым информационным входам второго и третьего коммутаторов , вход инкрементирования индекса устройства подключен к счетному входу счетчика, выход которого подключен к второму информационному входу треть его коммутатора, выход которого подключен к информационному входу регистра индекса, выход которого подключен к второму информационному входу второго коммутатора и к информационному входу счетчика, вход тактовых импульсов устройства подключен к первым входам первого и второго элементов И и синхровходу регистра индекса, выход второго элемента И подключен к пятому управляющему входу блока циклов, вход кода режима

0

0

5

0

5

0

5

0

5

128

адресации устройства подключен к вхо ду дешифратора, первый, второй, тр:.- тий выходы которого подключении соот ветственно к управляющему входу третьего коь мутатора, к второму ьхо- ду элемента ИЛИ и второму входу второго элемента И, выход элемента ШШ подключен к второму входу первого элемента И, выход которого подключен к синхровходу регистра адреса, вход адреса устройства подключен к первому информационному входу блока циклов, входы признаков записи индек- . сов, чтения индексов, записи количества индексов и установки работы устройства подключены соответственно к первому, второму, тре ьему и четвертому управляющим входам блока циклов, информационный вькод котс-- рого подключен к второму информационному входу сумматора, первый управляющий выход блока циклов подключен к выходу конца цикла работы устройства, отличающе, еся тем, что, с целью расширения функциональных возможностей за счет обеспечения двоично-разрядной инверсии, в устройство введены первьм и второй мультиплексоры, причем информационные входы первого мул ьтршлексора соединены с выходом регистра адреса, выход первого мультиплексора соединен с первым входом сумматора, выход которого соединен с информационными входами второго мультиплексора, выход которого соединен с вторым информационньм входом первого коммутатора, управляющие входы первого и второго мультиплексоров соединены с вторым управляющим выходом блока циклов.

2. Устройство по п.1, отличающееся тем, что блок циклов содержит группу из М узлов управления циклом, дешифратор, элемент И, элемент М-2И-М-ИЛИ и М разрядный регистр, причем первые входы узлов управления циклом соединены с первым входом элемента И и с первым управляющим входом блока, вторые, третьи и четвертые входы узлов управления циклом соединены с вторым, третьим и четвертым управляющими входами блока соответственно, первые информационные входы узлов управления циклом соединены с информационным входом М-разрядного регистра и-с вторым информационным входом блока, вход дешифратора является перBbiM информационным входом блока, выходы дешифратора соединены соответственно с пятыми управляющими входами узлов управления циклом и вторым входом элемента И, выход которого соединен,;с синхровходом М-разрядно- го регистра, выходы которого пораз- ; рядно соединены с соответствующими первыми входами элемента М-2И-М-ИЛИ, выход которого является вторым управ- 4яющим выходом блока, информационные 1|ыходы узлов управления циклом обра- 4уют информационньА выход блока, вто- ые входы элемента М-2И-М-ИЛИ соеди- йены с первыми управляющими выходами соответствующих узлов управления циклом, шестой вход М-го узла управления циклом является пятыг управляющим входом блокаi второй управляющий выход каждого предыдущего узла управления циклом соединен с шестым управляющим входом следующего узла управления циклом, второй управляющий выход каждого предыдущего узла управления циклом соединен с шестым управляющим входом следующего узла управления циклом, второй управляющий выход первого узла управления циклом является первьм управляющим выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления операцией записи | 1981 |

|

SU1003091A1 |

| Устройство для деления чисел без восстановления остатка | 1989 |

|

SU1605228A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| Устройство для выполнения команд реализации систем многоместных логических функций | 1981 |

|

SU999051A1 |

| Процессор | 1977 |

|

SU691858A1 |

| Устройство для формирования адреса | 1985 |

|

SU1297045A1 |

| Имитатор для тестирования компонентов моноканальной локальной вычислительной сети | 1987 |

|

SU1446621A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Устройство для обмена данными в многопроцессорной вычислительной системе | 1983 |

|

SU1136143A1 |

Изобретение относится к вычислительной технике и предназначено для формирования исполнительных адресов обращения к ОЗУ ЭВМ. С целью расширения его функциональных возможностей за счет обеспечения двоично-разрядной инверсии адресов (необходимой при реализации алгоритмов БПФ) в устройство, содержащее ре- , гистр 8 адреса, регистр 7 индекса, сумматор 10, счетчик 15, дешифратор 17, блок 20 циклов, введены два мультиплексора 36, 37, а в блок 20-узел управления двоично-разрядной инверсией, состоящий из М-разрядного регистра, элемент М-2И-М-ИЛИ и элемент И. 1 з.п.ф-лы,, 4 ил.

фиг,2

55

57

at n nt

„ -

J//

62

yjf/t gnpaSASHUff циклом

Л Jl

rJfL

HI

к т

SI

(50

Cff

48

-АД

| Устройство для формирования адреса данных | 1982 |

|

SU1068939A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство адресации | 1985 |

|

SU1267416A1 |

Авторы

Даты

1988-08-23—Публикация

1987-01-19—Подача