(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1980 |

|

SU942141A2 |

| Запоминающее устройство | 1980 |

|

SU920832A1 |

| Многоканальный фотометр | 1987 |

|

SU1492224A1 |

| Запоминающее устройство с переменным форматом данных | 1981 |

|

SU987678A1 |

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| Устройство для декодирования двоичных блочных кодов, согласованных с многопозиционными сигналами | 1987 |

|

SU1587644A1 |

| Оперативное запоминающее устройство для растрового дисплейного терминала | 1988 |

|

SU1564692A1 |

| Ассоциативный параллельный процессор | 1981 |

|

SU1166128A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1833918A1 |

| Устройство для возведения бинарной матрицы в квадрат | 2020 |

|

RU2744239C1 |

1

Изобретение относится к вычислительной технике и может быть использовано при построении устройств хранения дискретной информации.

Известно запоминающее устройство (ЗУ) содержащее матрицу блоков памяти, регистр адреса, выходной регистр и логические элементы 1.

Недостатком этого ЗУ является невысокое быстродействие.

Наиболее близким техническим рещением к предлагае.мо.му является запоминающее устройство, содержащее матрицу п X п блоков памяти, где п - разрядность слова, адресные входы которых соединены с выходами старщих разрядов регистра адреса, входы выбора блоков памяти i-й, где 1 , строки матрицы подключены к i-y выходу дещифратора, входы которого соединены с выходами младших разрядов регистра адреса, информационные входы блоков памяти j-ro, где 1 j столбца матрицы подключены к j-y выходу входного регистра, а информационные выходы - к j-й группе входов основного блока элементов ИЛИ, выходы которого соединены со входами выходного регистра 2.

Недостатком известного устройства является невозможность считывания и записи в нем даннцх, представляющих собой группу одноименных разрядов нескольких чисел.

Цель изобретения - расширение области применения известного ЗУ путем одновременного считывания или записи одноименных разрядов нескольких слов.

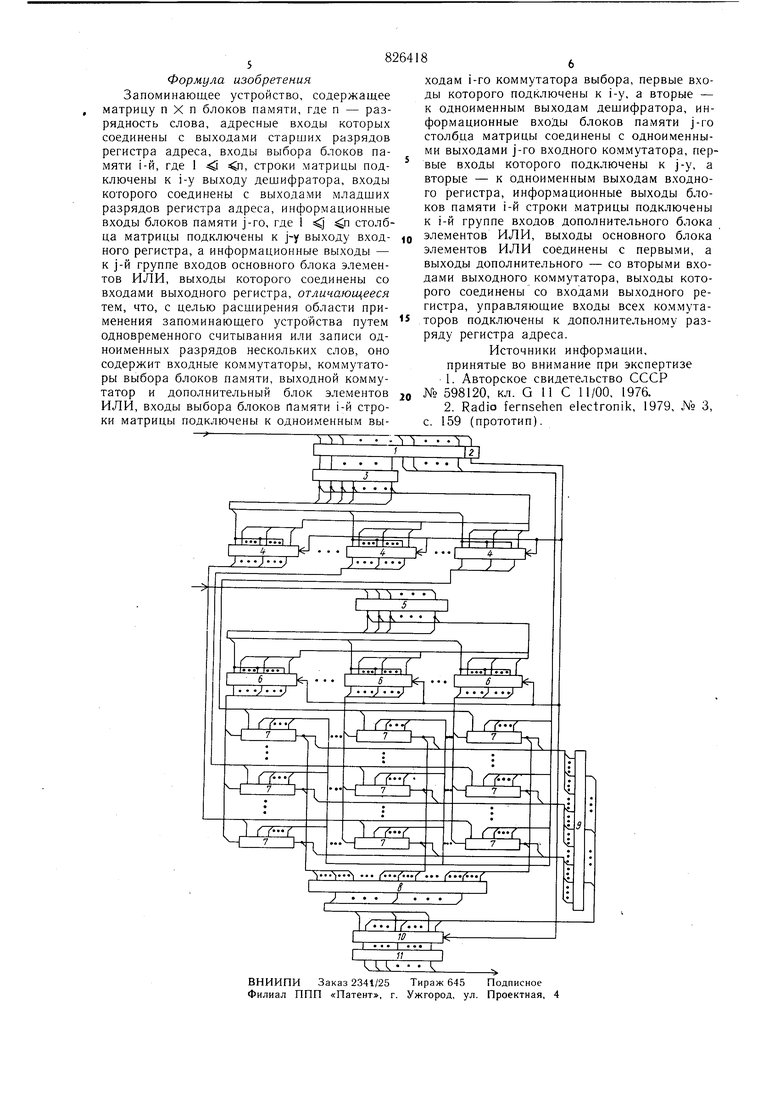

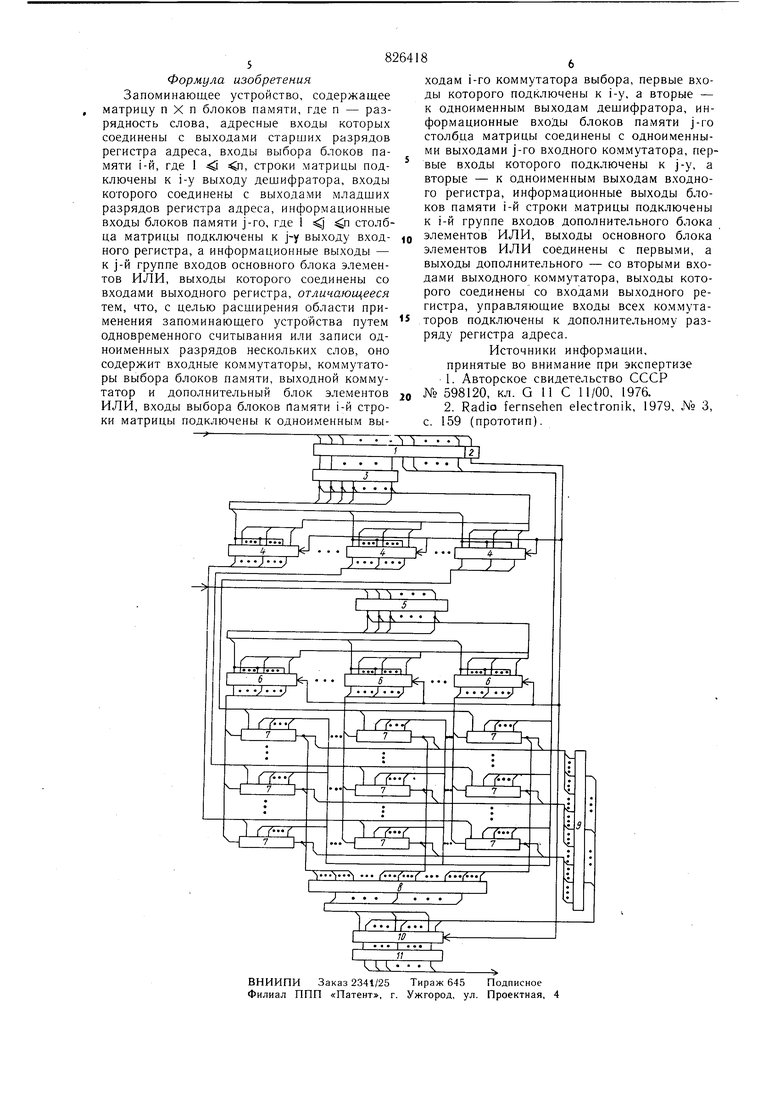

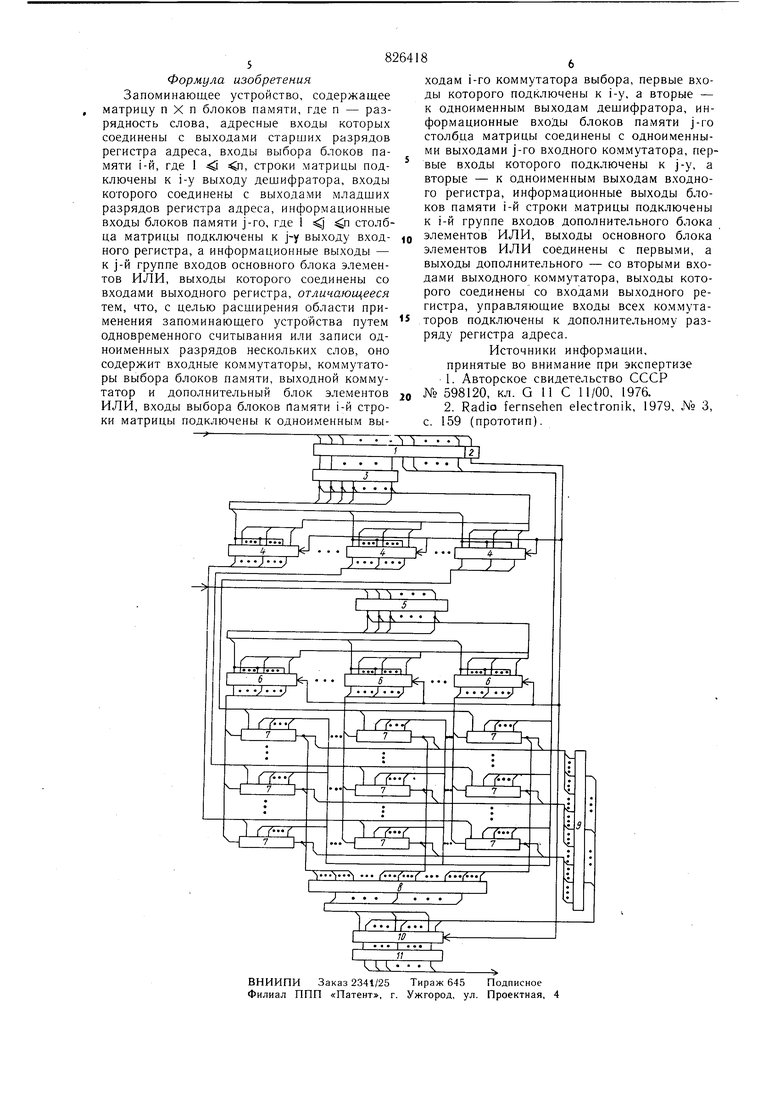

Поставленная цель достигается тем, что оно содержит входные коммутаторы, коммутаторы выбора блоков памяти, выходной коммутатор и дополнительный блок элементов ИЛИ, входы выбора блоков памяти i-й строки матрицы подключены к одноименным выходам i-ro коммутатора выбора, первые входы которого подключены к i-y, а вторые- к одноименным выходам дещифратора, информационные входы блоков памяти j-ro столбца матрицы соединены с одноименными выходами j-ro входного коммутатора, первые входы которого подключены к j-y, а вторые - к одноименным выходам входного регистра, информационные выходы блоков памяти i-й строки матрицы подключены к 1-й группе входов дополнительного блока элементов ИЛИ, выходы основного блока элементов ИЛИ соединены с первыми, а выХОДЫ дополнительного - со вторыми входами выходного коммутатора, выходы которого соединены со входами выходного регистра, управляющие входы всех коммутаторов подключены к дополнительному разряду регистра адреса. На чертеже приведена блок-схема предлагаемого ЗУ. ЗУ содержит регистр 1 адреса с дополнительным разрядом регистра 2 адреса, дешифратор 3, коммутаторы 4 выбора, входной регистр 5, входные коммутаторы 6, матрицу 7 блоков памяти, основной блок 8 элементов ИЛИ, дополнительный блок 9 элементов ИЛИ, выходной коммутатор 10 и выходной регистр 11. Выходной коммутатор 10, входные коммутаторы 6 и коммутаторы 4 выбора - коммутаторы с двумя п-разрядными информационными и одним управляющим входом. При поступлении сигнала логического нуля на управляющий вход коммутатора на его выход поступает информация с первого, а при поступлении сигнала логической единицы - со второго входа. Основной 8 и дополнительный 9 блоки элементов ИЛИ содержит по п п-входовых элементов ИЛИ. Устройство функционирует следующим образом. ЗУ может работать в пяти режимах: хранения информации, считывания п-разрядных чисел, записи п-разрядных чисел, считывания данных, представляющих собой группу одноименных разрядов п чисел, записи данных, представляющих собой группу одноименных разрядов п чисел. 1.Хранение информации. Считывание и запись информации не производится. 2.Считывание п-разрядных чисел. 2.1.В регистр 1 адреса заносится адрес числа, одновременно дополнительный разряд регистра 2 адреса устанавливается в состояние «О (на управляющие входы всех коммутаторов поступает сигнал логического нуля). При этом через дешифратор 3 и коммутаторы 4 выбора на входы выбора блоков 7 памяти i-й строки матрицы (номер строки задается младшими разрядами регистра I адреса) поступает сигнал логической единицы, на входы выбора остальных блоков 7 памяти матрицы поступает сигнал логического нуля. Адресные сигналы старших разрядов регистра 1 адреса поступают на адресные входы всех блоков 7 памяти. Таким образом, оказывается выбранной одна ячейка блоков памяти i-й строки матрицы. 2.2.Производится считывание. Сигнал считываемого числа с информационных выходов блоков 7 памяти i-й строки через основной блок 8 элементов ИЛИ и выходной коммутатор 10 поступает на входы выходного регистра II (число из выбранной ячейки памяти записывается в выходной регистр) 3.Запись h-разрядного числа. 3.1.Так же, как и в п. 2.1 производится выбор ячейки па.мяти, в которую необходимо записать число. 3.2.Производится запись. Сигналы записываемого числа с выходов входного регистра 5 через первые входы входных коммутаторов 6 поступают на информационные входы всех блоков 7 памяти и устанавливают запоминающие элементы выбранной ячейки в необходимые состояния. 4.Считывание данных, представляющих собой группу одноименных разрядов п чисел. 4.1.В регистр 1 адреса заносится адрес числа, одновременно дополнительный разряд регистра 2 адреса устанавливается в состояние «1 (на управляющие входы всех коммутаторов поступает сигнал логической единицы). При этом через дешифратор 3 и коммутаторы 4 выбора на входы выбора блоков 7 памяти j-ro столбца матрицы (номер столбца задается младшими разрядами регистра 1 адреса) поступает сигнал логической единицы, на входы выбора остальных блоков 7 памяти матрицы поступает сигнал логического нуля. Адресные сигналы старших разрядов регистра 1 адреса поступают на адресные входы всех блоков 7 па.мяти. Таким образом, оказывается выбранным на бор запоминающих элементов, соответствующий группе J-X разрядов п чисел в блоках памяти j-ro столбца матрицы. 4.2.Производится считывание. Сигналы считываемой группы разрядов с инфор.мационных выходов блоков 7 памяти j-ro столбца через дополнительный блок 9 элементов ИЛИ и выходной коммутатор 10 поступают на входы выходного регистра 11 (группа одноименных разрядов п чисел из выбранного набора запоминающих элементов записывается в выходной регистр). 5.Запись данных, представляющих собой группу одноименных разрядов п чисел. 5.1.Так же, как и в п. 4.11 производится выбор набора запоминающих элементов, в которые необходимо записать группу одноименных разрядов п чисел. 5.2.Производится запись. Сигналы записываемых разрядов с выходов входного регистра 5 через вторые входы коммутаторов 6 поступают на информационные входы всех блоков 7 памяти и устанавливают запоминающие элементы выбранного набора в необходи.мые состояния. Таким образом, в предлагаемом ЗУ воз.можны не только обычные считывание и запись чисел, но считывание и запись данных, представляющих собой группы однои.менных разрядов нескольких чисел, что расширяет область при.менения ЗУ, которое может быть использовано в дисплеях, устройствах обработки информации, информационно-поисковых и других системах. Формула изобретения Запоминающее устройство, содержащее матрицу п X п блоков памяти, где п -- разрядность слова, адресные входы которых соединены с выходами старших разрядов регистра адреса, входы выбора блоков памяти i-й, где 1 : п, строки матрицы подключены к i-y выходу дещифратора, входы которого соединены с выходами младших разрядов регистра адреса, информационные входы блоков памяти j-ro, где 1 4п столб ца матрицы подключены к j-y выходу входного регистра, а информационные выходы - к j-й группе входов основного блока элементов ИЛИ, выходы которого соединены со входами выходного регистра, отличающееся тем, что, с целью расширения области применения запоминающего устройства путем одновременного считывания или записи одноименных разрядов нескольких слов, оно содержит входные коммутаторы, коммутаторы выбора блоков памяти, выходной коммутатор и дополнительный блок элементов ИЛИ, входы выбора блоков Памяти i-й строки матрицы подключены к одноименным выходам i-ro коммутатора выбора, первые входы которого подключены к i-y, а вторые - к одноименным выходам дешифратора, информационные входы блоков памяти j-ro столбца матрицы соединены с одноименными выходами j-ro входного коммутатора, первые входы которого подключены к j-y, а вторые - к одноименным выходам входного регистра, информационные выходы блоков памяти i-й строки матрицы подключены к i-й группе входов дополнительного блока элементов ИЛИ, выходы основного блока элементов ИЛИ соединены с первыми, а выходы дополнительного - со вторыми входами выходного коммутатора, выходы которого соединены со входами выходного регистра, управляющие входы всех коммутаторов подключены к дополнительному разряду регистра адреса. Источники информации, принятые во внимание при экспертизе 1 Авторское свидетельство СССР № 598120, кл. G П С 11/00, 1976. 2. Radio fernsehen electronik, 1979, № 3, с. 159 (прототип).

Авторы

Даты

1981-04-30—Публикация

1979-08-17—Подача