I

Изобретение относится к вычислительной технике, .в частности к запоминающим устройствам (ЗУ), выполненным нз полупроводниковых элементах.

Изв-scTHo устройство, содержащее накопитель, адресный блок и блок формирования данных,подключенные к блоку управления, счетчик, регистры и блок сравнения TlJ.

Недостатком данного устройства является невозможность проверки исправности электронного обрамления Наиболее близким техническим ре1аением к изобретению является запоминающее устройство, содержащее бло памяти, соответствующие входы которого соединены с выходами дешифратора-адреса и регистра ввода, а выходы - со входами регистра вывода, выходы которого соединены со входами блока контроля, выход блока контроля подключен ко входу генератора тактовых импульсов, выход которого

подключен ко входу счетчика адреса, выходы счетчика адреса соединены с соответствуняцими входами дешифратора адреса. После предварительной записи тестон логического О или логической 1 производится считывание информации с ряда запоминающих ячеек и ее контроль на схемах совпадения JJ2..

Однако такая структура ЗУ не позволяет определить неисправность электронного -обрамления запоминающих злементов - дешифраторов адреса, что может привести к неправильному функционированию ЗУ в целом. В то же время для проверки ЗУ требуются специальные схемы совпадения, отвечающие данным логическим уровням, считываемым с ряда запоминающих элементов, что усложняет устройство в целом и снижает его надежность.

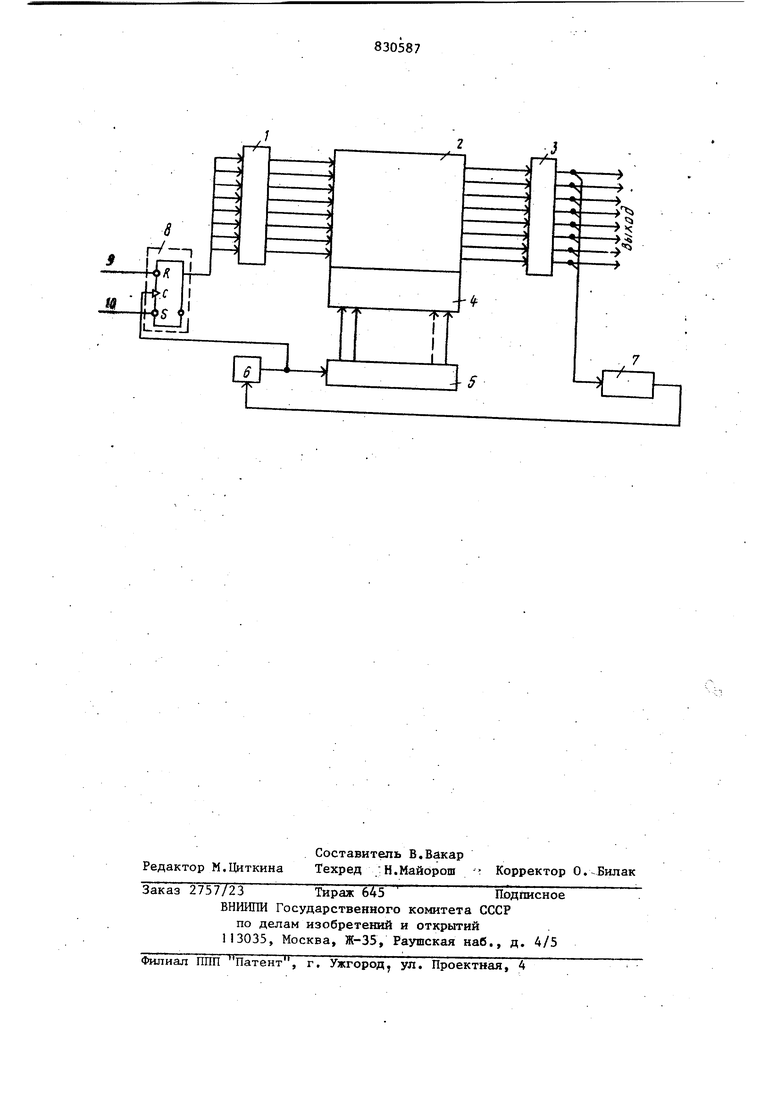

Цель изобретения - повышение надежности устройства. Поставленная цель достигается тем, что в устройство введены блок формирования тестовых кодов, вход которого соединен с выходом генератора тактовых импульсов, а выход со входом регистра ввода. При этом блок формирования тесто вых кодов вьпюлнен на триггере Т, На чертеже представлена структур ная схема предлагаемого устройства. Устройство содержит регистр I ввода, блок. 2 памяти, регистр 3 вывода, дешифратор 4 адреса, счетчик 5 адреса, генератор 6 тактовых импульсов, блок 7 контроля, блок формироваьчтя тестовых кодов, выполненр;Ый Tia Т-триггере 8, ьтана 9 уста новки ., щииа 10 установки О. Устройство работает следуюсдам образ о NT, В режиме контроля на шины 9 и 10 ycTanoBiaf 1 ,i О поступают в прот вофкзс логические сигналы, Б зависимости от комбинации фаз на шиьгах 9 и 10 на вы-ходе Т-триггера 8 устана вликается сигнал логической или логлчес}сого , который при работе 1-еиератора 6 тактовых импульсов записывается в блок 2 памяти. При одновременном поступлении сиг налов логической Г на шины 9 и 10 разрешается работа Т-триггера 8 по сче ному/ входу е. В этом случае при работе генератора, в блок 2 памяти поочередно, байта ш записываются сигналылогической 1 и логического О. Проверка исправности блока памяти осуп ествляется путем считывания контрольных тестов при помощи блока 7 контроля на четное число одноуровневых символов в байте. При обнаружении ошибки сигнал с выхода блока 7 контроля блокирует работу генератора тактовых импульсов. Предлагаемое запоминающее устройство имеет преимущества перед из4вестным в том, что исключаются схемы совпадения, определяю цие соответствие считываемых сигналов уровням логического О или логической J, осуществляется возможность контроля встроенных в блок памяти дешифраторов адресов. При этом проверка блока памяти производится при помощи стандартного устройства контроля по модулю два. Формула изобретения 1.Запоминающее устройство с самоконтролем, содержащее блок памяти, соответствующие входы которого соединены с выходами дешифратора адреса и регистра ввода, а выходы - со входами регистра вывода, выходы которого соединены со входами блока контроля, выход блока контроля подключен ко входу генератора тактовых импульсов , выход которого подключен ко входу счетчика адреса, выходы счетчика адреса соединены с соответствующими входами дешифрптора адреса, отличающ е е с я тем, что, с цел1 повышения надежности устройства, оно содержит блок формирования тестовых кодов, вход которого соединен с выходом гейератора тактовых импульсов , а выход - со входом регистра ввода. 2.Устройство по п. 1, отличающееся тем ,что блок формирования тестовых кодов выполнен на триггере Т. - . Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 601762, кл. G 11 С 29/00, 1976. 2.Патент США № 4055754, кл. 235-302, опублик. 1977 (прототип) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1981 |

|

SU1010651A1 |

| Запоминающее устройство с блокировкой неисправных элементов памяти | 1981 |

|

SU1010652A1 |

| Устройство для контроля и диагностики логических узлов | 1980 |

|

SU960825A1 |

| Устройство тестового контроля цифровых блоков | 1985 |

|

SU1315982A1 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Устройство для сопряжения абонентов с ЭВМ | 1986 |

|

SU1410041A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Устройство для контроля логических узлов | 1983 |

|

SU1129616A1 |

| Микропроцессорная система с контролем | 1984 |

|

SU1242976A1 |

| Устройство для контроля памяти | 1983 |

|

SU1129656A1 |

Авторы

Даты

1981-05-15—Публикация

1979-07-09—Подача