(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ

БЛОКОВ

ния набора выходных сигналов, формируемых на выходах контролируемой схемы в предыдущем такте, в качестве входного набора - в последующем такте контроля.

Недостатком известного устройства является большой объем оборудования из-за относительно большого объема запоминаю-, щих блоков для хранения эталонных входных и выходных наборов.

Цель изобретения - сокращение объема памяти устройства.

Поставленная цель достигается тем, что в устройство для контроля логических блоков, содержащее блок сравнения, первый вход и выход которого соединены соответственно с первым выходом и входом блока управления, второй выход которого соединен с входом блока хранения эталонных выходных наборов, выход которого-соединен со вторым входом блока сравнения, третий выход блока управления соединен со входом блока хранения эталонных входных наборов, введен двоичный сумматор, первый вход которого соединен с четвертым выходом блока управления, второй вход-.с выходом блока хранения эталонных входных наборов, а выход - с третьим входом блока сравнения.

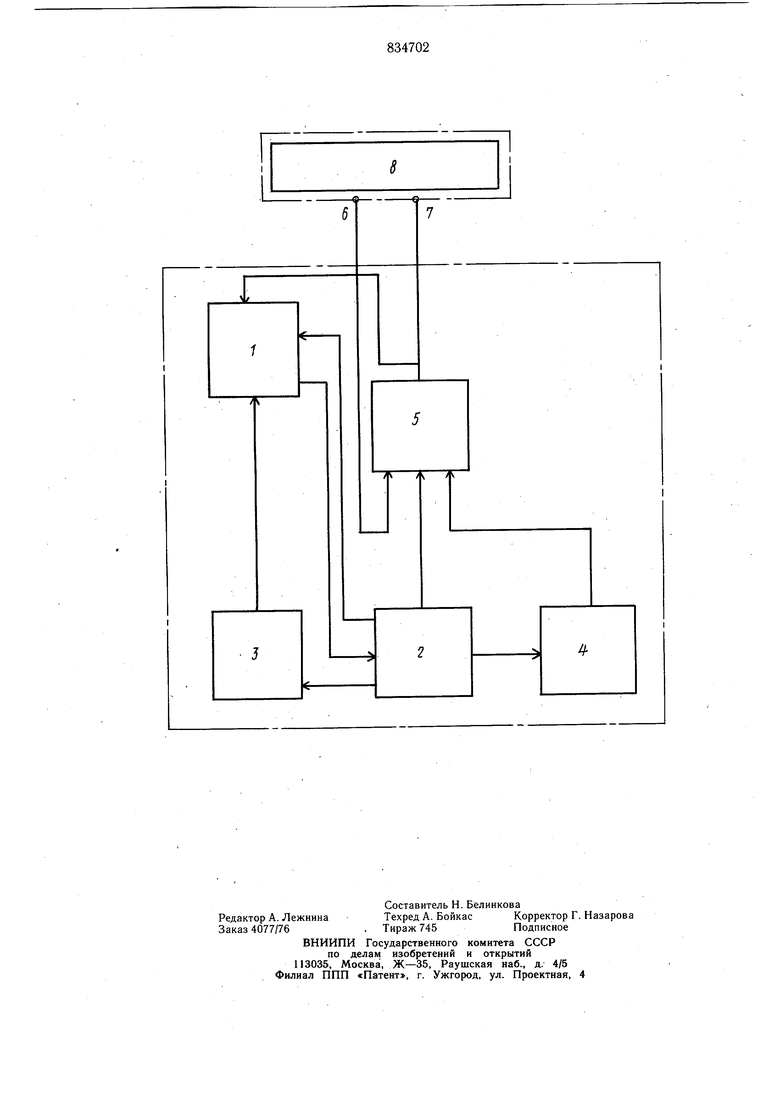

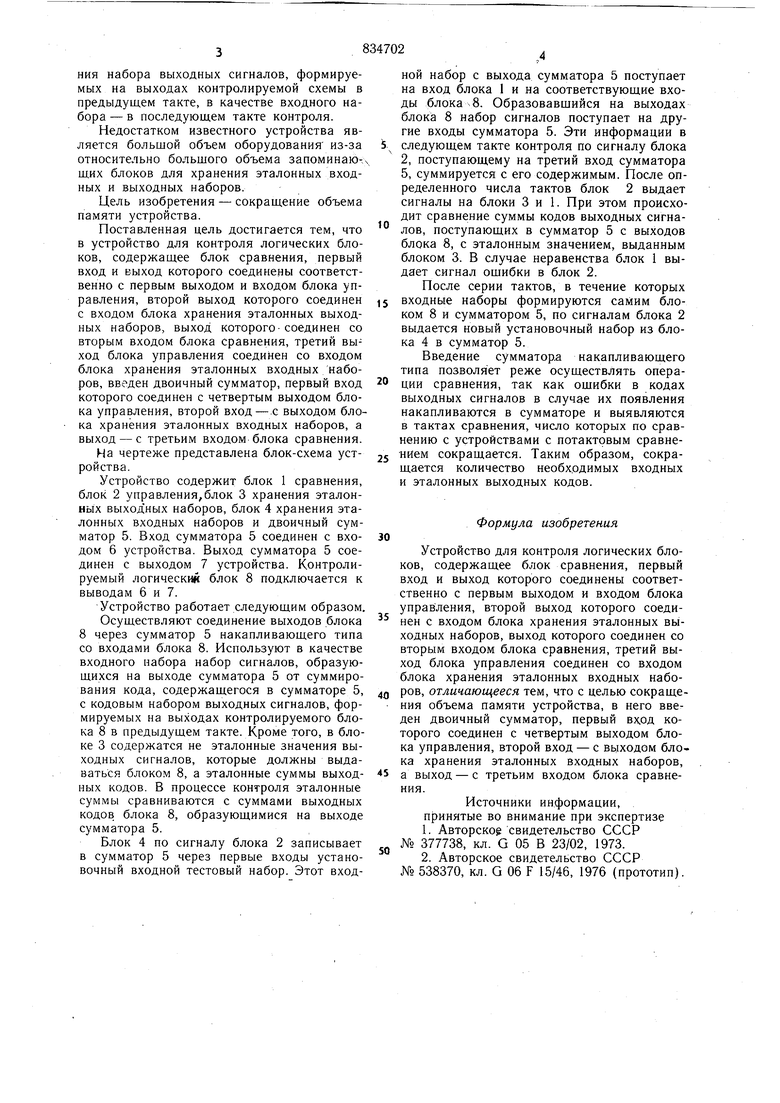

На чертеже представлена блок-схема устройства.

Устройство содержит блок 1 сравнения, блок 2 управления,блок 3 хранения эталонных выходных наборов, блок 4 хранения эталонных входных наборов и двоичный сумматор 5. Вход сумматора 5 соединен с входом 6 устройства. Выход сумматора 5 соединен с выходом 7 устройства. Контролируемый логический блок 8 подключается к выводам 6 и 7.

Устройство работает следующим образом.

Осуществляют соединение выходов блока 8 через сумматор 5 накапливающего типа со входами блока 8. Используют в качестве входного набора набор сигналов, образующихся на выходе сумматора 5 от суммирования кода, содержащегося в сумматоре 5, с кодовым набором выходных сигналов, формируемых на выходах контролируемого блока 8 в предыдущем такте. Кроме того, в блоке 3 содержатся не эталонные значения выходных сигналов, которые должны выдаваться блоком 8, а эталонные суммы выходных кодов. В процессе контроля эталонные суммы сравниваются с суммами выходных кодов блока 8, образующимися на выходе сумматора 5.

Блок 4 по сигналу блока 2 записывает в сумматор 5 через первые входы установочный входной тестовый набор. Этот входНОЙ набор с выхода сумматора 5 поступает на вход блока 1 и на соответствующие входы блока 8. Образовавщийся на выходах блока 8 набор сигналов поступает на другие входы сумматора 5. Эти информации в следующем такте контроля по сигналу блока 2, поступающему на третий вход сумматора 5, суммируется с его содержимым. После определенного числа тактов блок 2 выдает сигналы на блоки 3 и 1. При этом происходит сравнение суммы кодов выходных сигналов, поступающих в сумматор 5 с выходов блока 8, с эталонным значением, выданным блоком 3. В случае неравенства блок 1 выдает сигнал ощибки в блок 2.

После серии тактов, в течение которых входные наборы формируются самим блоком 8 и сумматором 5, по сигналам блока 2 выдается новый установочный набор из блока 4 в сумматор 5.

Введение сумматора накапливающего типа позволяет реже осуществлять операции сравнения, так как ощибки в кодах выходных сигналов в случае их появления накапливаются в сумматоре и выявляются в тактах сравнения, число которых по сравнению с устройствами с потактрвым сравнением сокращается. Таким образом, сокращается количество необходимых входных и эталонных выходных кодов.

Формула изобретения

Устройство для контроля логических блоков, содержащее блок сравнения, первый вход и выход которого соединены соответственно с первым выходом и входом блока управления, второй выход которого соединен с входом блока хранения эталонных выходных наборов, выход которого соединен со вторым входом блока сравнения, третий выход блока управления соединен со входом блока хранения эталонных входных наборов, отличающееся тем, что с целью сокращения объема памяти устройства, в него введен двоичный сумматор, первый вход которого соединен с четвертым выходом блока управления, второй вход - с выходом блока хранения эталонных входных наборов, а выход - с третьим входом блока сравнения.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР № 377738, кл. G 05 В 23/02, 1973.

2.Авторское свидетельство СССР

№ 538370, кл. G 06 F 15/46, 1976 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических блоков | 1975 |

|

SU538370A1 |

| Устройство для контроля цифровых блоков | 1982 |

|

SU1037261A1 |

| АВТОМАТИЗИРОВАННОЕ УСТРОЙСТВО КОНТРОЛЯ И ДИАГНОСТИРОВАНИЯ РАДИОЭЛЕКТРОННЫХ ИЗДЕЛИЙ | 1998 |

|

RU2174699C2 |

| Устройство для контроля логических блоков | 1978 |

|

SU763901A1 |

| Устройство для контроля логических узлов | 1981 |

|

SU968816A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство аналого-цифрового преобразования | 1986 |

|

SU1343551A1 |

| Запоминающее устройство с само-КОНТРОлЕМ | 1979 |

|

SU836682A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

Авторы

Даты

1981-05-30—Публикация

1978-10-06—Подача