(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С САМОКОНТРОЛЕМ

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1978 |

|

SU763977A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1094071A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1185400A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1100638A1 |

| Ассоциативное запоминающее устройство с самоконтролем | 1980 |

|

SU858105A1 |

| Устройство для восстановления информацииВ блОКАХ пАМяТи | 1978 |

|

SU849297A1 |

| Оперативное запоминающее устройст-BO C САМОКОНТРОлЕМ | 1979 |

|

SU794671A1 |

| Ассоциативное запоминающее устройство | 1975 |

|

SU555438A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1249592A1 |

| Запоминающее устройство с самоконтролем | 1987 |

|

SU1501171A1 |

Изобретение относится к области за поминающих устройств.

Известны запоминающие устройства (ЗУ), использующие принцип суммирования информации для контроля правильности ее считывания 2 .

Одно из известных устройств требует прерывания внешнего обращения на время проведения контроля массива при упорядоченной адресации всего контролируемого массива ЗУ f I .

В этом устройстве не учитывается характер внешних обршдений, предшествующих циклу контроля массива информации, что требует проведения независимого шгкла контроля, соответствующего прерывания работы внешних устройств и снижает производительность контроля.

Из известных устройств наиболее близким техническим решением к изобретению является ЗУ с самоконтролем, содержащее первый накопитель, первый сумматор, первые входы которых подключены . к щине записи, а вторые зходы - к щине

запись-считывание , выход первого накопителя соединен с третьим входом первого сумматора, четвертый вход которого соединен с первым выходом блоке управления, а пятый вход - с первым входом блока управления и шиной сброса, третий вход первого накопителя соединен с адресной , четвертый - с шиной обращения, второй накопитель, первые к вторые входы которого соединены соотвегственно с третьим и четвертым входами первого накопителя, третий и четвертый входы соответственно соединены со вторым и третьим выходами блоКа управления, второй сумматор, первый вход которого соединен с выходом второго накопителя, второй вход - с выходом nqpeoro сумматора, третий - с выходом первого накопителя, счетчик, вход которого соединен с выходом блока управления, а выход - с третьим его входом 2.

Такая структура устройства позволяет b ряде случае (при обращ«1ии ко всему ассиву с произвольной адресацией в про- цессе работы устройства) завершить цикл контроля. В этом устройстве, в случае, если хотя бы к одному адресу из проверяемого массива не было обращения, требуется проводить отдельный цикл контроля всего массива. Это .снижает быстродействие устройства.в процессе контроля. Цепь изобретения - повышение быстродействия устройства. Поставленная цель достигается тем, что в ЗУ с самоконтролем, содержащее адресный накопитель, сумматоры и блок управления, причем один из управляющих и информационный входы адресного накопителя подключены соответственно к первому и второму входам первого сумматора выход адресного- накопителя соединен с

третьим входом первого сумматора и с первым входом второго сумматора, второй вход которюго соединен с выходом первого сумматора, первый вход блока управления подключен к выходу второго сумматора, одни из выходов блока управления соединены с установочными входами сумматоров, введены ассоциативный накопитель, и элементы И. Входы ассоци&тивного накопителя подключены соответственно к выходам элементов И и адресным входам адресного накопителя и другим выходам блока управления, а выходы соответственно ко вторым входам второго сумматора и блока управления и первым входам элементов И, вторые входы которых соединены с другим управляющим входом адресного накопителя, а третьи входы являются адресными входами устройства.

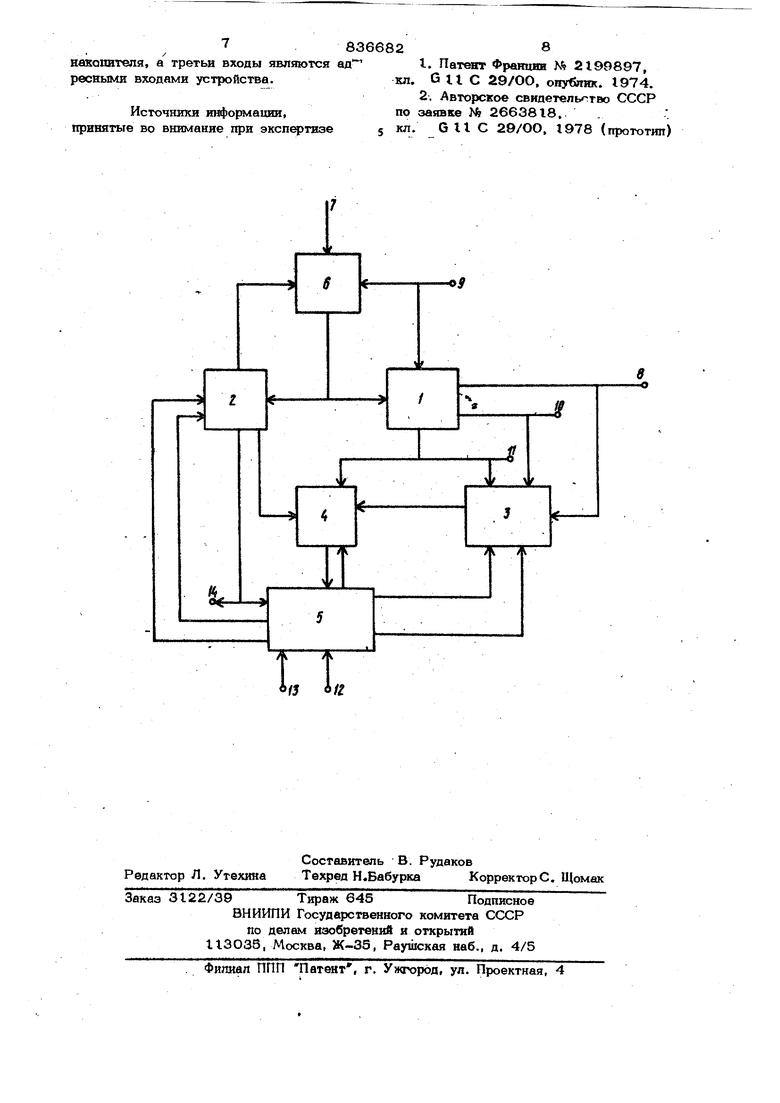

На чертеже приведена структурная :: схема предложенного устройства ,

Устройство содержит адресный накопитель I, ассоциативный накопитель 2, первый сумматор 3, второй сумматор 4, блок управления 5, элементы И 6, адресные шины 7, являющиеся адресными входами устройства, шину признака запись считывание 8, шину обращения 9, число,вую входную шину Ю, числовую выходную шину II, шину начальной установки 12, шину сигнала ошибки 13 и шину сигнала конца контроля 14.

Выходы накопителя I и сумматора 4 подключены соответственно к первым входам сумматора 4 и блока 5. Входы накопителя 2 подключены соответственно к выходам элементов И 6 и адресным входам накопителя I и к одним из выходов блока В, а выходы соответственно - ко вторым входам сумматора 4 и блока

ченных в процессе считывания шфзрмашш накопителей 1,2. Блок управления 5 обес-

печивает синхронизацию работы устройства.

Устройство работает следующим образом ,

Предварительно, перед началом работы производится заполнение накопителей I

и 2 кодами О, для чего на адресную внешнюю шину 7 подаются последовательно коды адресов, на шину обраще- ния 9 - сигнал обращения к ЗУ, а на числовую входную шину Ю и на числовой

вход накопителя 2 - от блока управления 5 код О.

Затем сигналом по шине начальной установки 12 через блок управления 5 сумматоры 3 и 4 приводятся в начальное состояние соответствующее начальному нулевому заполнению накопителя I . В каждом такте накопитель t, в зависимости от признака операции на шине признака записи-считывания 8, и шина

обращения 9 работает в режиме только считывания или- считывания - записи информации, а на копитель 2 - в режиме считывания - записи - поиска информации в каждом такте, причем характер поиска

и записи (поиск О или I, запись О или 1) определяется блоком 5,

В первом цикле контроля в накопитель 2 записывается код 1, и производится поиск кода О. Адрес ячейки, в которой хранится код О, вырабатывается накопителем 2 на выходе, связанном с элементами И 6. Адрес ячейки, в которой записывается код 1, формируется на выходах элементов И 6.

При наличии внешнего обращения ha выходе элементов И 6 устанавливается код адрес а шины 7, а при отсутствии обращеи первым входам элементов И 6, вторые входы которых соединены с одним из управляющих входов накопителя 1, а третьи входы являются адресными входами устройства. Накопитель I обеспечивает запись, считывание и хранение информации. Накопитель 2 допускает ассоциативный поиск, адресную запись и считывание информации: элемейты И 6 пропускают код внешнего адреса шины при наличии обращения к ЗУ по шине 9 или код адреса ячейки ассоциативного накопителя 2, полученный в результате поиска при отсутствии обращения; сумматоры 4 и 3 образуют значения основной и разностной значений контрольных сумм, полуния - код адреса ячейки, подготовленно накопителем 2 в предыдущем такте. При записи в накопитель I производится вычисление разности записываемо и считываемой из ячейки информации помощью сумматора 3, который накапли вает значение разности, Все ячейки, адреса которых поступал на адресные входы накопителей I и 2, отмечаются записью I в накопитель Информация, считьтаёмая из накопите ля I на числовую выходную шину II, поступает в сумматор 4 в том случае, если к рассматриваемой ячейке производится первое обращение в рассматривае мом цикле контроля. Признаком этого является код О, считываемый из накопителя 2 на его выход, связанный с входом сумматора 4 В первом цикле контроля код О яв ляется разрешением для проведения сум мирования в сумматоре 4. В каждом такте в накопителе 2 производится поиск ячеек, хранящих код О Адреса таких ячеек формируются схемами выборки многозначного ответа накопителя 2 в конце каждого такта. Если в последующем такте отсутствует внешнее обращение, информация накопителя I считывается по адресу, обра зованному накопителем 2, на вход сумматора 4 для проведения операции суммирования. Отсутствие в накопителе ячеек, хранящих код О, означает окончание первого цикла контроля, что отмечается появлениетл сигнала на шине сигнала конца контроля 14, связанной с блоком управления 5, который анализирует состояние сумматора 4. При правильном считывании информации состояние сумма тора 4 должно быть нулевым, так как накопитель I предварительно заполнялся кодами О. В случае нулевого состояния суммато ра 4 блок управления 5 выдает сигнал ошибки на шину 13 сигнала ошибки. При нулевом состоянии сумматора 4 происходит передача содержимого сумматора 3 в сумматор 4 для проведения следующего второго цикла суммирования. Установка сумматора 4 прбизводится содержимым сумматора 3 таким образом чтобы при правильном - считывании информации его состояние в конце шпсла суммирования было нулевым. Во втором цикле суммирования признаком первого обращения к ячейке на- копителя I является код 1 на числовом выходе накопителя 2 . Блок управления 5 настраивает сумматор 4 для проведения операции суммирования при наличии разрешения в виде I на входе сумматора 4, а накопитель 2 опрашивается на наличие кода I в его ячейках. Устройство работает аналогично работе в первом цикле контроля. Таким образом, использование ассоциативного накопителя для избирательного формирования адресов ячеек не прошедших контроль при внешних обращениях к ЗУ, обеспечивает повышения час.тоты контроля в процессе функционирования ЗУ, а также позволяет сократить прерывания обращения внешних устройств к ЗУ для проведения операции контрольного суммирования информации при ограничении на минимально допустимую частоту контроля. Формула изобретения Запоминающее устройство с самоконтролем, содержащее адресный накопитель, сумматоры и блок управления, причем один из управляющих и информационный входы адресного накопителя подключены соответственно к первому и второму входам первого сумматора, выход адресного накопителя соединен с третьим входом первого сумматора и с входом второго сумматора, второй вход ко торого соединен с выходом первого сумматора, первый вход блока управления подключён к выходу второго сумматора j в одни из выходов блока управления соединены с установочными входами сумматоров, отличающеес я тем, что, с целью повышения быстродействия устрюйства, оно содержит ассоциативный накопитель и элементы И, причем входы ассоциативного накопителя подключены соответственно к выходам элементов И и адресным входам адресного накопителя и другим выходам блока управления, а выходы-соответственно ко вторым входам второго сумматора и блока управления и первым входб1М элементов И, вторые входы которых соединены с кругам управляющим входом адресного

78366828

накопвтепя, а третьи входы являются . Патент Фратши М 2199897,

ресными входами устройства.

Источники информации, принятые во внимание при экспертизе

п

43 fl

кл. G II С 29/ОО, опубта. 1974. 2. Авторское свидетелытво СССР по заявке № 2663818. 5 кл. Gil С 29/ОО, 1978 (прототип)

Авторы

Даты

1981-06-07—Публикация

1979-07-03—Подача