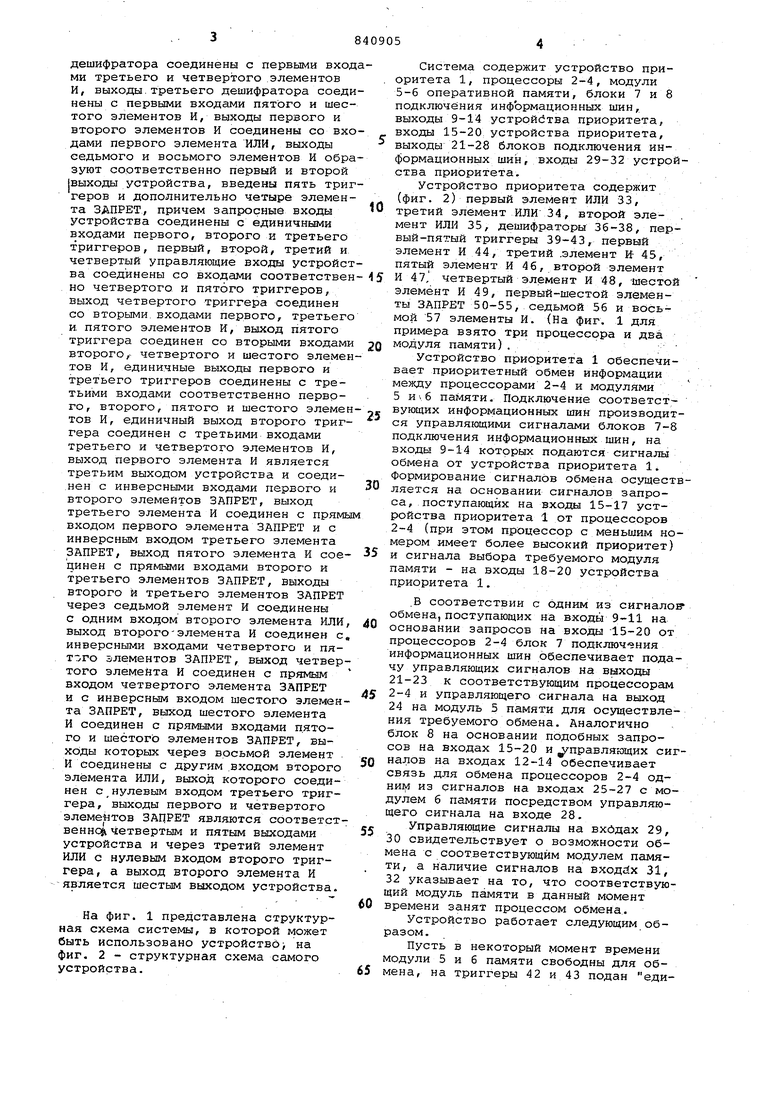

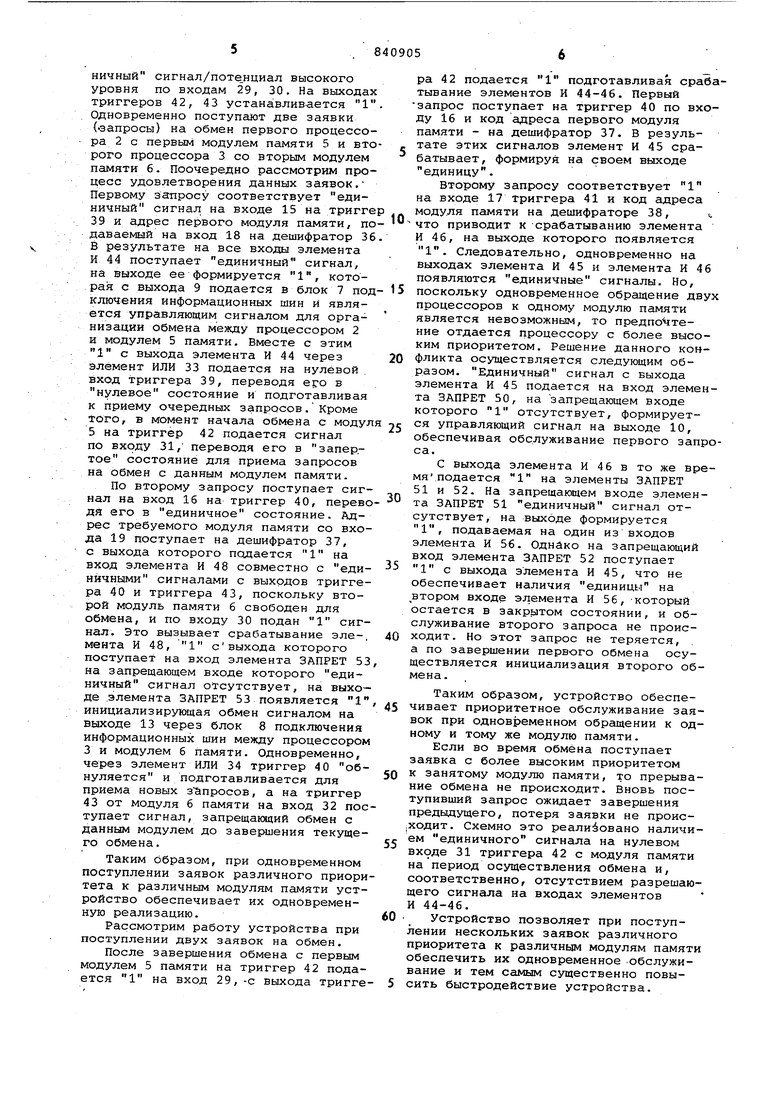

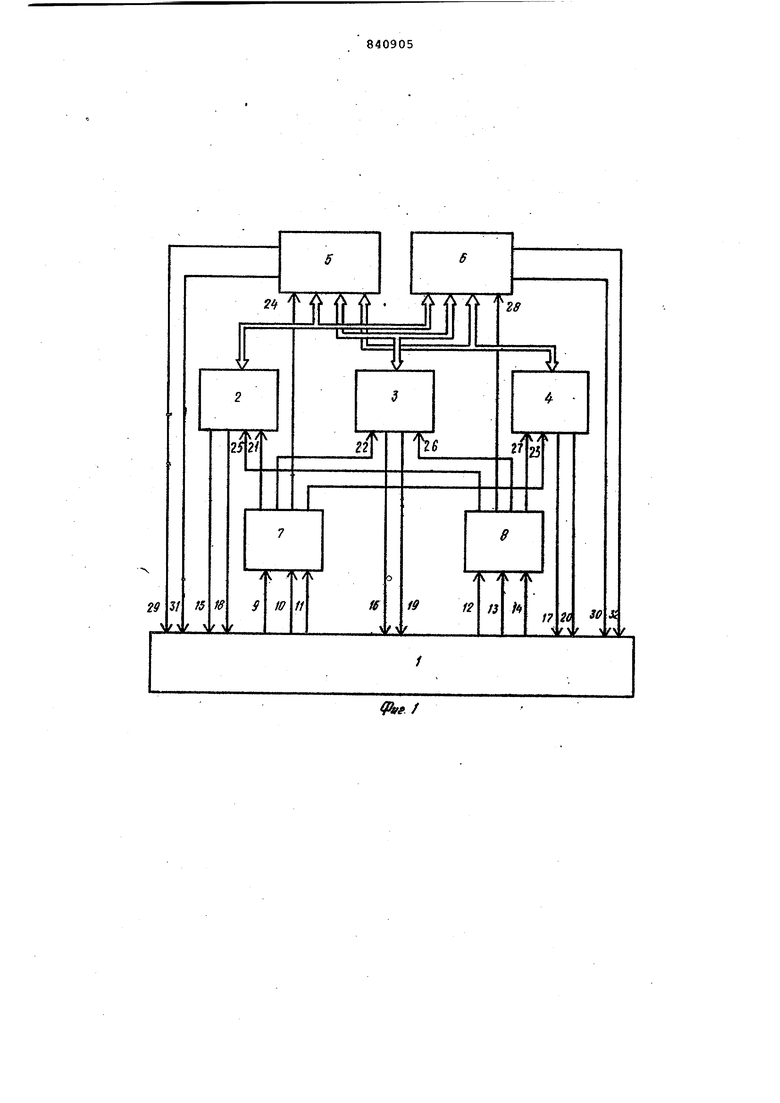

Устройство относится к вычислитель ной технике и предназначено для использования в качестве коммутатора модульной (секционированной) памяти мультипроцессорных вычислительных систем. В роли процессоров могут выступать также и каналы, которые в сов ременных вычислительных системах пред ставляют собой периферийные процессоры. Известно устройство приоритета, позволяющее присвоить запросам приоритеты с некоторого Rf-ro по нулевой в порядке убывания. Выборка приорите та осуществляется, начиная с запроса который имеет наивысший приоритет и заканчивается нулевым запросом, имеющим низший приоритет. Запрос выс шего порядка, принятый в последнюю очередь, может обменяться приоритето с другим низшим запросом, в результате чего запрос низшего порядка получает временный приоритет над запросом высшего порядка, принятым в последнюю очередь l3. Однако недостатком устройства является последовательное обслуживание запросов, что замедляет общее вр мя обслуживания. Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство приоритета, содержащее дешифраторы, элементы И, ИЛИ, НЕ, ЗАПРЕТ и позволяющее обеспечивать приоритетное обслуживание запросов на обмен с блоком памяти как внутри одной группы запросов, так.и между различными группами запросов f2 . Однако и это устройство не обеспечивает быстрого обмена при одновременном поступлении нескольких запросов различного приоритета к различным блокам памяти, так как обслуживание запроса более высокого приоритета не позволяет одновременно осуществлять обработку запроса.более низкого приоритета к свободному блоку памяти. Цель изобретения - повышение быстродействия. Поставленная цель достигается тем, что, в устройство приоритета, содержащее три дешифратора, восемь элементов И, три элемента ИЛИ и два элемента ЗАПРЕТ, причем входы дешифраторов являются кодовыми входами устройства, выходы первого дешифратора соединены с первыми входами первого и второго элементов И, выходы второго дешифратора соединены с первыми вход ми третьего и четвертого элементов И, выходы.третьего дешифратора соед нены с первыми входами пятого и шес того элементов И, выходы первого и второго элементов И соединены со вхо дами первого элемента ИЛИ, выходы седьмого и восьмого элементов И обр зуют соответственно первый и второй {выходы устройства, введены пять три геров и дополнительно четыре элемен та ЗАПРЕТ, причем запросные входы устройства соединены с единичными входами первого, второго и третьего триггеров, первый, второй, третий и четвертый управляющие входы устройс ва соединены со входами соответстве но четвертого и пятого триггеров, выход четвертого триггера соединен со вторыми, входами первого, третьег и. пятого элементов И, выход пятого триггера соединен со вторыми входам второго,- четвертого и шестого элеме тов И, единичные выходы первого и третьего триггеров соединены с третьими входами соответственно перврго, второго, пятого и шестого элеме тов И, единичный выход второго триг гера соединен с третьими входами третьего и четвертого элементов И, выход первого элемента И является третьим выходом устройства и соеди.нен с инверсными входами первого и второго элементов ЗАПРЕТ, выход третьего элемента И соединен с прям входом первого элемента ЗАПРЕТ и с инверсным входом третьего элемента ЗАПРЕТ, выход пятого элемента И сое динен с прямыми входами второго и третьего элементов ЗАПРЕТ, выходы второго и третьего элементов ЗАПРЕТ через седьмой элемент И соединены с одним входом второго элемента ИЛИ выход второгоЭлемента И соединен с инверсными входами четвертого и пятого элементов ЗАПРЕТ, выход четвер того элемейта И соединен с прясмым входом четвертого элемента ЗАПРЕТ и с инверснЕлм входом шестого элемен та ЗАПРЕТ, выход шестого элемента И соединен с прямыми входами пятого и шестого элементов ЗАПРЕТ, выхс1ды которых через восьмой элемент И соединены с другим .входом второго элемента ИЛИ, выход которого соединен с нулевым входом третьего триггера, выходы первого и четвертого элементов ЗАПРЕТ являются соответст веннсй четвертым и пятым выходами устройства и через третий элемент ИЛИ с нулевым входом второго триггера, а выход второго элемента И является шестым выходом устройства. На фиг. 1 представлена структурная схема системы, в которой может быть использовано устройство на фиг. 2 - структурная схема самого устройства. Система содержит устройство приоритета 1, процессоры 2-4, модули 5-6 оперативной памяти, блоки 7 и 8 подключения информационных шин, выходы 9-14 устройбтва приоритета, входы 15-20 устройства приоритета, выходы 21-28 блоков подключения информационных шин, входы 29-32 устройства приоритета. , . . Устройство приоритета содержит (фиг. 2) первый элемент ИЛИ 33, третий элемент ИЛИ 34, второй элемент ИЛИ 35, дешифраторы 36-38, первый-пятый триггеры 39-43, первый элемент И 44, третий .элемент И- 45, пятый элемент И 46, второй элемент И 47, четвертый элемент И 48, -шестой элемент И 49, первый-шестой элементы ЗАПРЕТ 50-55, седьмой 56 и восьмой 57 элементы И. (На фиг. 1 для примера взято три процессора и два модуля памяти). . Устройство приоритета 1 обеспечивает приоритетный обмен информации между процессорами 2-4 и модулями 5 памяти. Подключение соответствующих информационных шин производится управляющими сигналами блоков 7-8 подключения информационных шин, на входы 9-14 которых подаются сигналы обмена от устройства приоритета 1. Формирование сигналов обмена осуществляется на основании сигналов запроса, поступающих на входы 15-17 устройства приоритета 1 от процессоров 2-4 (при этом процессор с меньшим номером имеет более высокий приоритет) и сигнала выбора требуемого модуля памяти - на входы 18-20 устройства приоритета 1. .В соответствии с одним из сигналов обмена, поступающих на входа 9-11 на основании запросов на входы 15-20 от процессоров 2-4 блок 7 подключения информационных шин обеспечивает подачу управляющих сигналов на выходы 21-23 к соответствующим процессорам 2-4 и управляющего сигнала на выход 24 на модуль 5 памяти для осуществления требуемого обмена. Аналогично блок 8 на основании подобных запросов на входах 15-20 и управляющих сигналов на входах 12-14 обеспечивает связь для обмена процессоров 2-4 одним из сигналов на входах 25-27 с модулем 6 памяти посредством управляющего сигнала на входе 28. Управляющие сигналы на вхбдах 29, 30 свидетельствует о возможности обмена с соответствующим модулем памяти, а наличие сигналов на входах 31, 32 указывает на то, что соответствующий модуль памяти в данный момент времени занят процессом обмена.. Устройство работает следующим образом. Пусть в некоторый момент времени модули 5 и 6 памяти свободны для обмена, на триггеры 42 и 43 подан единичный сигнал/поте.нциал высокого уровня по входам 29, 30. На выходах триггеров 42, 43 устанавливается 1 Одновременно поступают две заявки (запросы) на обмен первого процессора 2 с первым модулем памяти 5 и второго процессора 3 со вторым модулем памяти 6. поочередно рассмотрим процесс удовлетворения данных заявок, Первому запросу соответствует единичный сигнал на входе 15 на тригге 39 и адрес первого модуля памяти, подаваемый на вход 18 на дешифратор 36 В результате на все входы элемента И 44 поступает единичный сигнал, на выходе ее формируется 1, которая с выхода 9 подается в блок 7 подключения информационных шин и является управляющим сигналом для организации обмена между процессором 2 и модулем 5 памяти. Вместе с этим 1 с выхода элемента И 44 через элемент ИЛИ 33 подается на нулевой вход триггера 39, переводя еро в нулевое состояние и подготавливая к приему очередных запросов, Кроме того, в момент начала обмена с модул 5 на триггер 42 подается сигнал по входу 31, переводя его в запертое состояние для приема запросов на обмен с данным модулем памяти.

По второму запросу поступает сигнал на вход 16 на триггер 40, переводя его в единичное состояние. Адрес требуемого модуля памяти со входа 19 поступает на дешифратор 37, с выхода которого псшается 1 на вход элемента И 48 совместно с единичными сигналами с выходов триггера 40 и триггера 43, поскольку второй модуль памяти 6 свободен для обмена, и по входу 30 подан 1 сигнал. Это вызывает срабатывание эле-, мента И 48, 1 свыхода которого поступает на вход элемента ЗАПРЕТ 53 на запрещающем входе которого единичный сигнал отсутствует, на выходе элемента ЗАПРЕТ 53 появляется 1 инициализирующая обмен сигналом на выходе 13 через блок 8 подключения информационных шин между процессором 3 и модулем б памяти. Одновременно, через элемент ИЛИ 34 триггер 40 обнуляется и подготавливается для приема новых запросов, а на триггер 43 от модуля 6 памяти на вход 32 поступает сигнал, запрещающий обмен с данным модулем до завершения текущего обмена.

Таким образом, при одновременном поступлении заявок различного приоритета к различным модулям памяти устройство обеспечивает их одновременную реализацию.

Рассмотрим работу устройства при поступлении двух заявок на обмен,

После завершения обмена с первым модулем 5 памяти на триггер 42 подается 1 на вход 29, -с выхода триггера 42 подается 1 подготавливая срабатывание элементов И 44-46. Первый

запрос поступает на триггер 40 по входу 16 и код адреса первого модуля памяти - на дешифратор 37. В результате этих сигналов элемент И 45 срабатывает, формируя на своем выходе единицу.

Второму запросу соответствует 1 на входе 17 триггера 41 и код адреса модуля памяти на дешифраторе 38, i.

что приводит к срабатыванию элемента И 46, на выходе которого появляется 1, Следовательно, одновременно на выходах элемента И 45 и элемента И 46 появляются единичные сигналы. Но, поскольку одновременное обращение двух процессоров к одному модулю памяти является невозможным, то предпо 1тение отдается процессору с более высоким приоритетом. Решение данного конфликта осуществляется следующим образом, Единичный сигнал с выхода элемента И 45 подается на вход элемента ЗАПРЕТ 50, на запрещающем входе которого 1 отсутствует, формируется управляющий сигнал на выходе 10, обеспечивая обслуживание первого запроса,

С выхода элемента И 46 в то же время подается 1 на элементы ЗАПРЕТ 51 и 52. На запрещающем входе элемента ЗАПРЕТ 51 единичный сигнал отсутствует, на выходе формируется 1, подаваемая на один из входов элемента И 56, Однако на запрещающий вход элемента ЗАПРЕТ 52 поступает 1 с выхода элемента И 45, что не обеспечивает наличия единицы на втором входе элемента И 56, -который остается в закрытом состоянии, и обслуживание второго запроса не происходит. Но этот запрос не теряется, а по завершении первого обмена осуществляется инициализация второго обмена.

Таким образом, устройство обеспечивает приоритетное обслуживание заявок при одновременном обраицении к одному и тому же модулю памяти,

Если во время обмена поступает заявка с более высоким приоритетом к занятому модулю памяти, то прерывание обмена не происходит. Вновь поступивший запрос ожидает завершения предыдущего, потеря заявки не проис.ходит. Схемно это реали: овано наличием единичного сигнала на нулевом

5 входе 31 триггера 42 с модуля памяти на период осуществления обмена и, соответственно, отсутствием разрешающего сигнала на входах элементов И 44-46.

0

Устройство позволяет при поступлении нескольких заявок различного приоритета к различньзм модулям памяти обеспечить их одновременное .обслуживание и тем самым существенно повысить быстродействие устройства.

Формула изобретения

Устройство приоритета, содержащее дешифраторы, элементы И, элементы ИЛ и элементы ЗАПРЕТ, причем входы дешифраторов являются кодовыми входами устройств, выходы первого дешифратора соединены с первыми входами первого и второго элементов И, выходы второго дешифратора соединены с пер|выми входами третьего и четвертого элементов И, выходы третьего дешифратора соединены .с первыми входами пятого и шестого элементов И, выходы первого и второго элементов И соединены со входами первого элемента ИЛИ, выходы седьмого и восьмого элементов И образуют соответственно первый и второй выходы устройства, о тличающееся тем, что, с целью повышения быстродействия, оно содержит пять.триггеров и дополнительно четыре элемента ЗАПРЕТ, причем запросные входы устройства соединены с единичными входами первого, второго и третьего триггеров, первый второй, третий, четвертый управляющие входы устройства соединены со входами соответственно четвертого и пятого триггеров, выход четвертого триггера соединен со вторыми входами первого, третьего и пятого элементов И, выход пятого триггера соединен со вторыми входами второго, четвертого и шестого элементов И, едининые выходы первого и третьего триггеров соединены с третьими входами соответственно первого, второго, пятого и шестого элементов И, единичный выход второго триггера соединен с третьими входами третьего и четвертого элементов И, выход первого элемента И является третьим выходом устроства и соединен с инверсными входами первого и второго элементов ЗАПРЕТ, выход третьего элемента И соединен с пря.мым входом первого элемента ЗАПРЕТ и с инверсным входом третьего элемента ЗАПРЕТ, выход пятого элемента И соединен с прямыми входами второго и третьего элементов ЗАПРЕТ, выходы второго и третьего элементов ЗАПРЕТ через седьмой элемент И соединены с одним входом второго элемента ИЛИ, выход второго элемента И соединен с инверсными входами четвертого и пятого элементов ЗАПРЕТ, выход четвертого элемента И соединен с прямым входом четвертого элемента ЗАПРЕТ и с инверсным входом шестого элемента ЗАПРЕТ, выход шестого элемента И соединен с прямыми входами пятого и шестого элементов ЗАПРЕТ, выходы которых через восьмой элемент И соединены с другим входом второго элемента ИЛИ, выход которого -соединен с нулевым входом третьего триггера, выходы первого и четвертого элементов ЗАПРЕТ являются соответственно .четвертым и пятым выходами устройства и- через третий элемент ИЛИ с нулевым входом второго триггера, а выход второго элемента И является шестым выходом устройства.

Источники информации, принятые во внимание при экспертизе

1.Патент Франции № 2301872, кл. G Об F 9/18, 1976.

2.Авторское свидетельство СССР № 458828, кл. G 06 F 9/18, 1975 (прототип).

1р1/г.2

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для обмена данными между модулями вычислительной системы | 1987 |

|

SU1444796A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Многоканальное устройство для приоритетного подключения источников информации к общей магистрали | 1989 |

|

SU1612303A1 |

| Устройство для обмена информацией между объектом контроля и электронной вычислительной машиной | 1983 |

|

SU1156078A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1476466A1 |

| Многоканальное устройство для обмена данными между модулями вычислительной системы | 1985 |

|

SU1256037A1 |

| Устройство для обращения двух процессоров к общему блоку памяти | 1990 |

|

SU1784986A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство приоритета | 1982 |

|

SU1108450A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1753474A1 |

Авторы

Даты

1981-06-23—Публикация

1979-09-04—Подача