(54) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ИСПРАВЛЕНИЕМ

ОШИБОК

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1161994A1 |

| УСТРОЙСТВО ДЛЯ ЗАПИСИ-ВОСПРОИЗВЕДЕНИЯ МНОГОКАНАЛЬНОЙ ЦИФРОВОЙ ИНФОРМАЦИИ | 1995 |

|

RU2107953C1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Устройство для исправления ошибокВ блОКЕ пАМяТи | 1979 |

|

SU842976A1 |

| Запоминающее устройство с автономным контролем | 1982 |

|

SU1043743A1 |

| Запоминающее устройство с исправлением ошибок | 1986 |

|

SU1363303A1 |

| Запоминающее устройство с контролем и коррекцией ошибок | 1983 |

|

SU1117715A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1374284A1 |

| Запоминающее устройство с самоконтролем | 1985 |

|

SU1302326A1 |

1

Изобретение относится к запоминающим устройствам.

Известно запоминающее устройство с исправлением ошибок краткости к, использующее метод (2к4-1)-кратного резервирования с голосованием по больщинству и состоящее из 2к+1 запоминающих блоков, одноименные выходы которых подаются на входы мажоритарных элементов «к+1 из 2к+1, исправляющих к ошибок 1.

. Недостатком этого устройства является избыточное количество оборудования.

Наиболее близким по технической сущности к изобретению является запоминающее устройство, содержащее накопительные модули, -регистр адреса, состоящий из регистра номера модуля и регистра номера ячейки, выходы которого подключены ко входам регистров адреса накопительных модулей, регистр слова, выходы которого подсоединены к информационным входам накопительных модулей, дешифратор нойера модуля, выходы которого через блок коммутации модулей подключены к управляющим входам накопительных модулей, элементы ИЛИ, входы которых подключены к выходам регистров слов накопительных модулей, блок

коррекции, выходы которого подключены к входам выходного регистра, а входы - к выходам элементов ИЛИ, и блок управления 2.

Недостатками этого устройства являются большие аппаратурные затраты, приводящие к увеличению стоимости устройства, и увеличение времени выборки при обнаружении ошибки.

Цель изобретения - упрощение устройства.

Поставленная цель достигается тем, что в запоминающее устройство с исправлением ощибок, содержащее накопители, входнрй регистр числа, регистр адреса, дешифратор, элемент ИЛИ, блок коррекции, выходной регистр числа и блок управления, причем одни из выходов регистра адреса и входного регистра числа подключены соответственно к адресным, и одним из информационных входов накопителей, управляющие входы и информационные выходы которых соединены соответственно с выходами дешифратора-и входами элемента ИЛИ, выход которого подключен ко входу блока коррекции, одни из выходов которого соединены с одним из входов выходного регистра числа.

управляющие входы накопителей подключены к одному из выходов блока управления, введены формирователь контрольных CHfналов и группы сумматоров, элементов И и ИЛИ, причем входы формирователя контрольных сигналов подключены к одним из выходов входного регистра числа, а выходы к другим информационным входам накопителей и первым входам сумматоров первой группы, вторые входы которых соединены с другими выходами входного регистра числа, а выходы - с первыми входами элементов И первой группы, выходы которых подключены к одним из входов элементов ИЛИ группы, выходы которых соединены со входами дешифратора, первые входы элементов И второй группы подключены к другим выходам регистра адреса, а выходы - к другим входам элементов ИЛИ группы и первым входам сумматоров второй группы, вторые входы которых соединены с другими выходами блока коррекции, а выходы - с другими входами выходного регистра числа, вторые входы элементов И подключены к другим выходам блока управления.

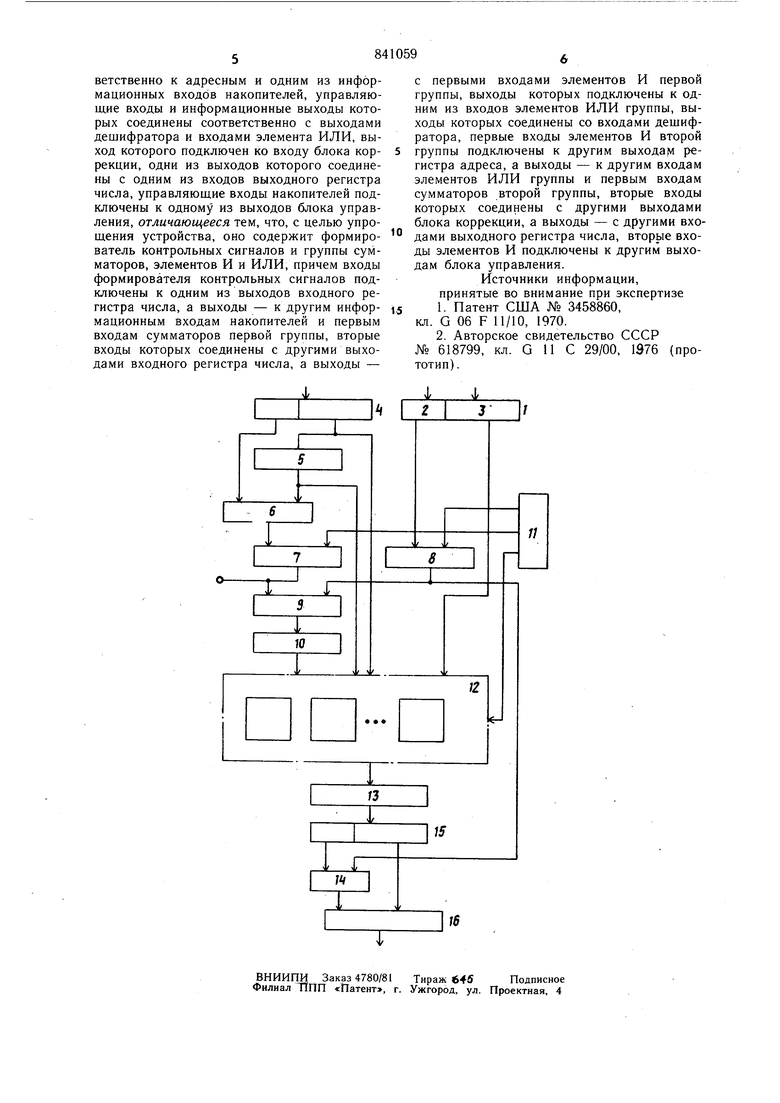

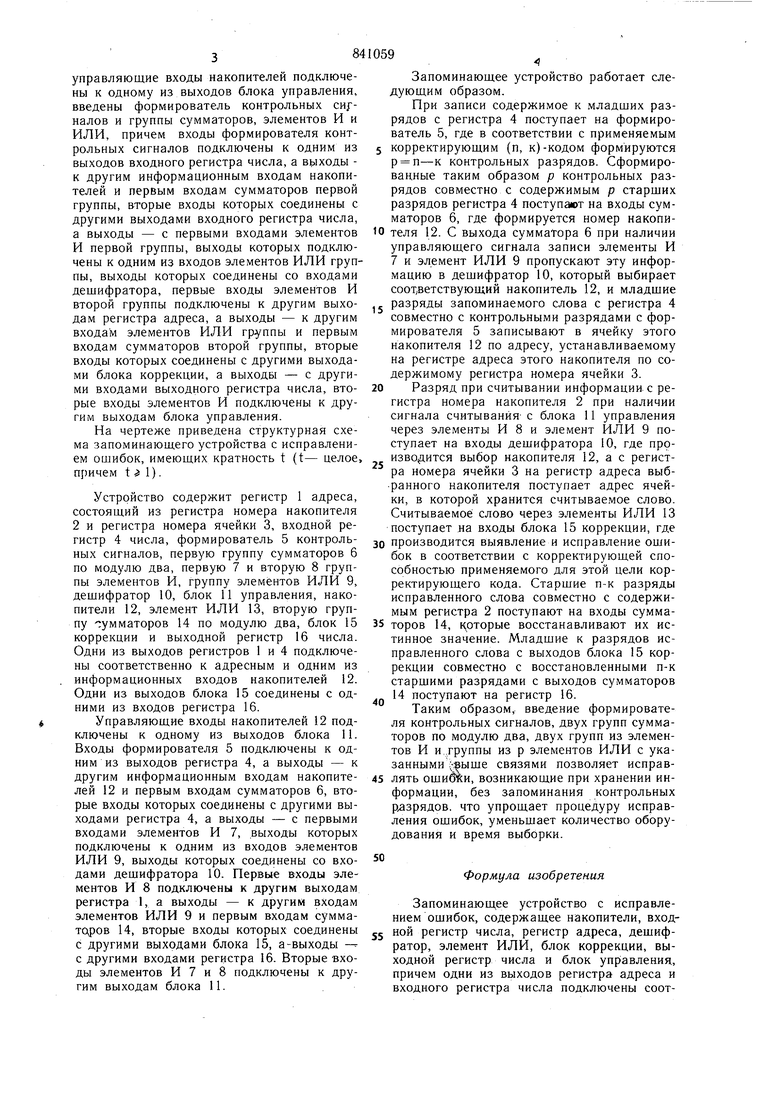

На чертеже приведена структурная схема запоминающего устройства с исправлением ошибок, имеющих кратность t (t- целое, причем t 1).

Устройство содержит регистр 1 адреса, состоящий из регистра номера накопителя 2 и регистра номера ячейки 3, входной регистр 4 числа, формирователь 5 контрольных сигналов, первую группу сумматоров 6 по модулю два, первую 7 и вторую 8 группы элементов И, группу элементов ИЛИ 9, дешифратор 10, блок 11 управления, накопители 12, элемент ИЛИ 13, вторую группу -сумматоров 14 по модулю два, блок 15 коррекции и выходной регистр 16 числа. Одни из выходов регистров 1 и 4 подключены соответственно к адресным и одним из информационных входов накопителей 12. Одни из выходов блока 15 соединены с одними из входов регистра 16.

Управляющие входы накопителей 12 подключены к одному из выходов блока 11. Входы формирователя 5 подключены к одним из выходов регистра 4, а выходы - к другим информационным входам накопителей 12 и первым входам сумматоров 6, вторые входы которых соединены с другими выходами регистра 4, а выходы - с первыми входами элементов И 7, выходы которых подключены к одним из входов элементов ИЛИ 9, выходы которых соединены со входами дешифратора 10. Первые входы элементов И 8 подключены к другим выходам регистра 1, а выходы - к другим входам элементов ИЛИ 9 и первым входам сумматоров 14, вторые входы которых соединены с другими выходами блока 15, а-выходы -с другими входами регистра 16. Вторые входы элементов И 7 и 8 подключены к другим выходам блока 11.

Запоминающее устройство работает следующим образом.

При записи содержимое к младших разрядов с регистра 4 поступает на формирователь 5, где в соответствии с применяемым

корректирующим (п, к)-кодом формируются р п-к контрольных разрядов. Сформированные таким образом р контрольных разрядов совместно с содержимым р старщих разрядов регистра 4 поступают на входы сумматоров 6, где формируется номер накопителя 12. С выхода сумматора 6 при наличии управляющего сигнала записи элементы И 7 и элемент ИЛИ 9 пропускают эту информацию в дешифратор 10, который выбирает соот,ветствующий накопитель 12, и младшие разряды запоминаемого слова с регистра 4 совместно с контрольными разрядами с формирователя 5 записывают в ячейку этого накопителя 12 по адресу, устанавливаемому на регистре адреса этого накопителя по содержимому регистра номера ячейки 3.

Разряд при считывании информации, с регистра номера накопителя 2 при наличии сигнала считывания- с блока И управления через элементы И 8 и элемент ИЛИ 9 поступает на входы дешифратора 10, где производится выбор накопителя 12, а с регистра номера ячейки 3 на регистр адреса выбранного накопителя поступает адрес ячейки, в которой хранится считывае.мое слово. Считываемое слово через элементы ИЛИ 13 поступает на входы блока 15 коррекции, где

0 производится выявление и исправление ошибок в соответствии с корректирующей способностью применяемого для этой цели корректирующего кода. Старшие п-к разряды исправленного слова совместно с содержимым регистра 2 поступают на входы сумматоров 14, (оторые восстанавливают их истинное значение. Младшие к разрядов исправленного слова с выходов блока 15 коррекции совместно с восстановленными п-к старшими разрядами с выходов сумматоров 14 поступают на регистр 16.

Таким образом, введение формирователя контрольных сигналов, двух групп сумматоров по модулю два, двух групп из элементов И и,труппы из р элементов ИЛИ с указанными :;выще связями позволяет исправлять , возникающие при хранении информации, без запоминания контрольных разрядов, что упрощает процедуру исправления ошибок, уменьшает количество оборудования и время выборки.

Формула изобретения

Запоминающее устройство с исправлением ощибок, содержащее накопители, входной регистр числа, регистр адреса, дешифратор, элемент ИЛИ, блок коррекции, выходной регистр числа и блок управления, причем одни из выходов регистра адреса и входного регистра числа подключены соответственно к адресным и одним из информационных входов накопителей, управляющие входы и информационные выходы которых соединены соответственно с выходами дешифратора и входами элемента ИЛИ, выход которого подключен ко входу блока коррекции, одни из выходов которого соединены с одним из входов выходного регистра числа, управляющие входы накопителей подключены к одному из выходов блока управления, отличающееся тем, что, с целью упрощения устройства, оно содержит формирователь контрольных сигналов и группы сумматоров, элементов И и ИЛИ, причем входы формирователя контрольных сигналов подключены к одним из выходов входного регистра числа, а выходы - к другим информационным входам накопителей и первым входам сумматоров первой группы, вторые входы которых соединены с другими выходами входного регистра числа, а выходы -

с первыми входами элементов И первой группы, выходы которых подключены к одним из входов элементов ИЛИ группы, выходы которых соединены со входами дeщифJ ратора, первые входы элементов И второй группы подключены к другим выходам регистра адреса, а выходы - к другим входам элементов ИЛИ группы и первым входам сумматоров второй группы, вторые входы которых соединены с другими выходами блока коррекции, а выходы - с другими входами выходного регистра числа, вторьте входы элементов И подключены к другим выходам блока управления.

Источники информации,

принятые во внимание при экспертизе

1 Патент США № 3458860, кл. G 06 F 11/10, 1970.

Авторы

Даты

1981-06-23—Публикация

1979-09-04—Подача