(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ОПЕРАТИВНОЙ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативной памяти | 1975 |

|

SU547837A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1001182A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1014041A1 |

| Устройство для контроля микропроцессорной системы | 1990 |

|

SU1741137A1 |

| Устройство для контроля блоков оперативной памяти | 1983 |

|

SU1161993A1 |

| Устройство для формирования управляющей информации при обработке данных сейсмических колебаний | 1981 |

|

SU1000766A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1003150A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для опроса информационных каналов | 1982 |

|

SU1062677A1 |

| Устройство для реализации быстрого преобразования Фурье при многоканальной обработке информации | 1983 |

|

SU1124324A1 |

1

Изобретение относится к запоминающим устройствам (ЗУ), а именно к устройствам для контроля блоков оперативной памяти.

Известно устройство для контроля оперативной памяти, в.котором изменение адреса производится не последовательным перебором, а по иному закону, например, используются «галопирующие тесты. Это делает контроль более достоверным, так как позволяет комбинировать последовательность обращения к любому адресу ЗУ с обращениями ко всем остальным адресам 1.

Однако, несмотря на больщую длительность проверки (число обращений к ЗУ составляет 2А, где А - количество адресов), распределение информации по разрядам является однородным. При этом требуются дополнительные динамические тесты для более полного контроля ЗУ.

Наиболее близким по технической сущности к изобретению является устройство, реализующее тест« динамический адресный код. Это устройство содержит блок управления, регистр числа, счетчики, счетный триггер, формирователь, элемент И, полусумматор и основные и дополнительные коммутаторы 2.

Однако в этом устройстве изменение адреса производится последовательно, так как в условиях эксплуатации обращение к адресам производится в произвольном порядке. Это снижает достоверность контроля.

Цель изобретения - повыщение достоверности контроля.

Поставленная цель достигается тем, что в устройство для контроля блоков оперативной памяти, содержащее регистр числа, блок управления, счетчики, триггер и первый коммутатор, причем входы регистра числа подключены к выходам первого коммутатора, персый выход блока управления соединен с входом первого счетчика и первым входом второго счетчика, входы третьего счетчика . подключены соответственно к выходам первого счетчика и триггера, выход которого соединен с выходом первого счетчика, второй выход блока управления и выходы регистра числа являются одними из выходов устройства, введены четвертый и пятый счетчики, второй и третий коммутаторы, сумматор и схему сравнения, причем выход первого счет чика подключен к первому входу четвертого счетчика, второму входу второго счетчика и входу пятого счетчика, выходы которого соединены с хханими из входов первого коммутатора и второгой коммутатора, другие входы которого подключены , соответственно к выходам третьего счетчика и схемы сравнения, а выходы - к одним из входов сумматора, входы схемы сравнения соединены соответственно с выходами второго счетчика и четвертого счетчика, второй вход которого подключен к первому выходу блока управления, входы третьего коммутатора подключены соответственно к третьему выходу блока управления и выходам второго и четвертого счетчиков; а выходы - к другим входам сумматора, выходы которого соединены с другими входами первого коммутатора, выходы третьего коммутатора являются другими выходами устройства.

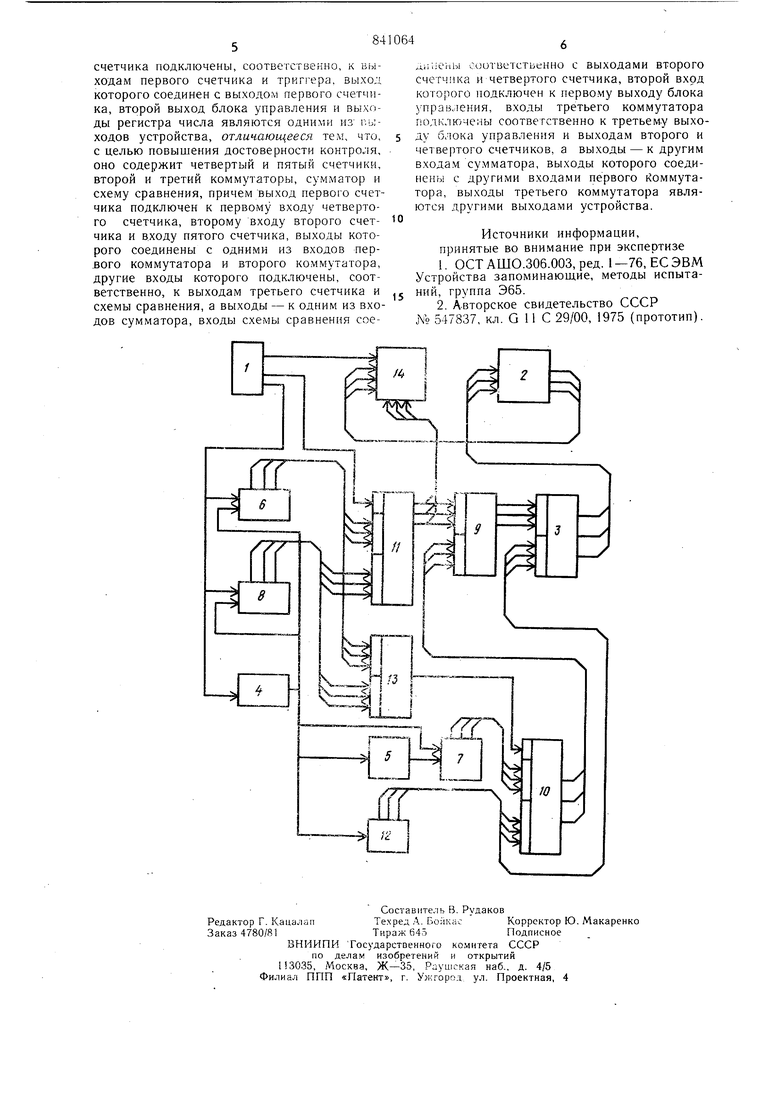

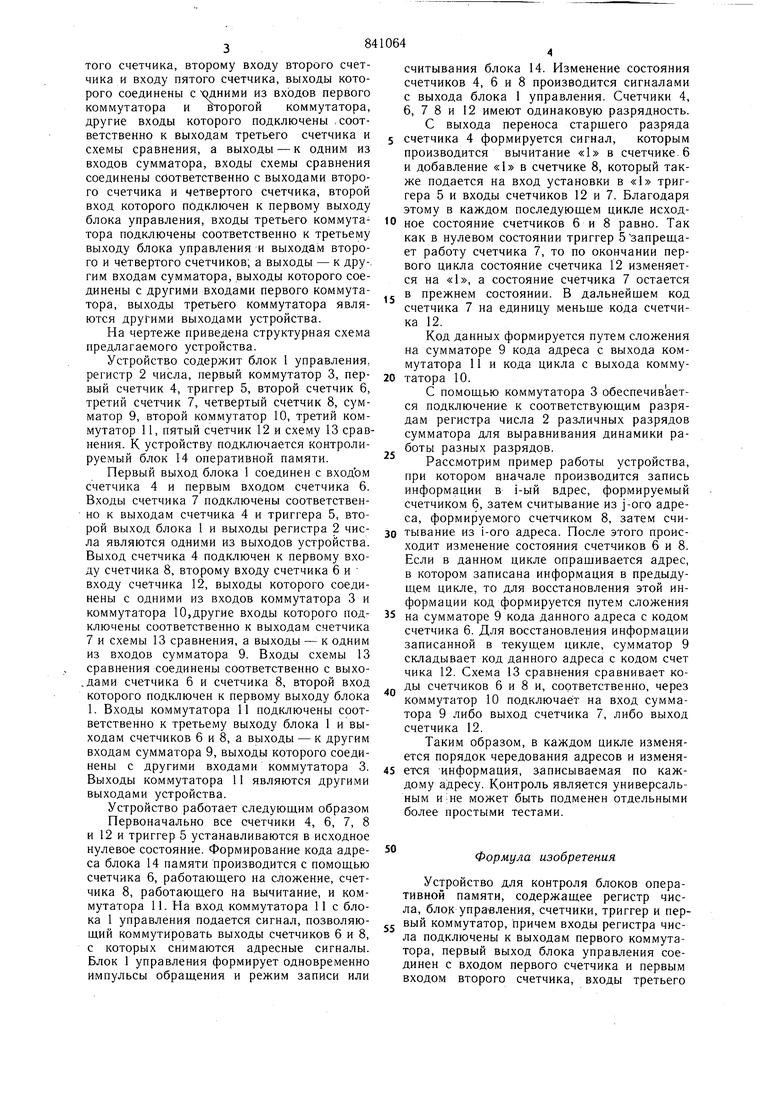

На чертеже приведена структурная схема предлагаемого устройства.

Устройство содержит блок 1 управления, регистр 2 числа, первый коммутатор 3, первый счетчик 4, триггер 5, второй счетчик 6, третий счетчик 7, четвертый счетчик 8, сумматор 9, второй коммутатор 10, третий коммутатор 11, пятый счетчик 12 и схему 13 сравнения. К устройству подключается контролируемый блок 14 оперативной памяти.

Первый выход блока 1 соединен с входЪм счетчика 4 и первым входом счетчика 6. Входы счетчика 7 подключены соответственно к выходам счетчика 4 и триггера 5, второй выход блока 1 и выходы регистра 2 числа являются одними из выходов устройства. Выход счетчика 4 подключен к первому входу счетчика 8, второму входу счетчика 6 и входу счетчика 12, выходы которого соединены с одними из входов коммутатора 3 и коммутатора 10,другие входы которого подключены соответственно к выходам счетчика 7 и схемы 13 сравнения, а выходы - к одним из входов сумматора 9. Входы схемы 13 сравнения соединены соответственно с выхо,дами счетчика 6 и счетчика 8, второй вход которого подключен к первому выходу блока 1. Входы коммутатора И подключены соответственно к третьему выходу блока 1 и выходам счетчиков 6 и 8, а выходы - к другим входам сумматора 9, выходы которого соединены с другими входами коммутатора 3. Выходы коммутатора 11 являются другими выходами устройства.

Устройство работает следующим образом

Первоначально все счетчики 4, б, 7, 8 и 12 и триггер 5 устанавливаются в исходное нулевое состояние. Формирование кода адреса блока 14 памяти производится с помощью счетчика 6, работающего на сложение, счетчика 8, работающего на вычитание, и коммутатора 11. На вход коммутатора 11 с блока 1 управления подается сигнал, позволяющий коммутировать выходы счетчиков 6 и 8, с которых снимаются адресные сигналы. Блок 1 управления формирует одновременно импульсы обращения и режим записи или

считывания блока 14. Изменение состояния счетчиков 4, 6 и 8 производится сигналами с выхода блока 1 управления. Счетчики 4, 6, 7 8 и 12 имеют одинаковую разрядность. С выхода переноса старщего разряда

счетчика 4 формируется сигнал, которым производится вычитание «1 в счетчике. 6 и добавление «1 в счетчике 8, который также подается на вход установки в «1 триггера 5 и входы счетчиков 12 и 7. Благодаря этому в каждом последующем цикле исходное состояние счетчиков б и 8 равно. Так как в нулевом состоянии триггер 5запрещает работу счетчика 7, то по окончании первого цикла состояние счетчика 12 изменяется на «1, а состояние счетчика 7 остается в прежнем состоянии. В дальнейшем код счетчика 7 на единицу меньще кода счетчика 12.

Код данных формируется путем сложения на сумматоре 9 кода адреса с выхода коммутатора 11 и кода цикла с выхода коммутатора 10.

С помощью коммутатора 3 обеспечивается подключение к соответствующим разрядам регистра числа 2 различных разрядов сумматора для выравнивания динамики работы разных разрядов.

Рассмотрим пример работы устройства, при котором вначале производится запись информации в i-ый вдрес, формируемый счетчиком 6, затем считывание из j-oro адреса, формируемого счетчиком 8, затем считывание из i-oro адреса. После этого происходит изменение состояния счетчиков б и 8. Если в данном цикле опращивается адрес, в котором записана информация в предыдущем цикле, то для восстановления этой информации код формируется путем сложения

5 на сумматоре 9 кода данного адреса с кодом счетчика 6. Для восстановления информации записанной в текущем цикле, сумматор 9 складывает код данного адреса с кодом счет чика 12. Схема 13 сравнения сравнивает коды счетчиков б и 8 и, соответственно, через коммутатор 10 подключает на вход сумматора 9 либо выход счетчика 7, либо выход счетчика 12.

Таким образом, в каждом цикле изменяется порядок чередования адресов и изменя5 етх;я -информация, записываемая по каждому адресу. Контроль является универсальным и:не может быть подменен отдельными более простыми тестами.

Формула изобретения

Устройство для контроля блоков оперативной памяти, содержащее регистр числа, блок управления, счетчики, триггер и первый коммутатор, причем входы регистра числа подключены к выходам первого коммутатора, первый выход блока управления соединен с входом первого счетчика и первым входом второго счетчика, входы третьего

Авторы

Даты

1981-06-23—Публикация

1979-10-26—Подача