(54)УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ОПЕРАТИВКОЙ ПАМЯТИ

ходамВторого счетчика, вход которого соединен с выходом счетного триггера,

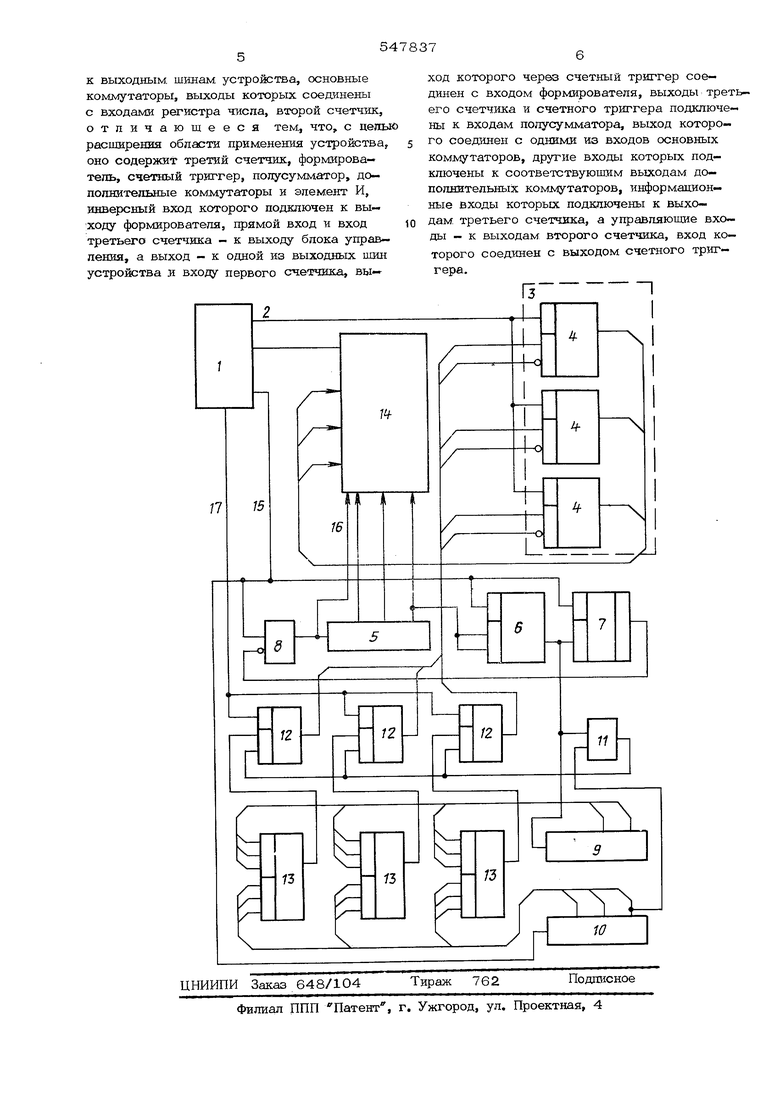

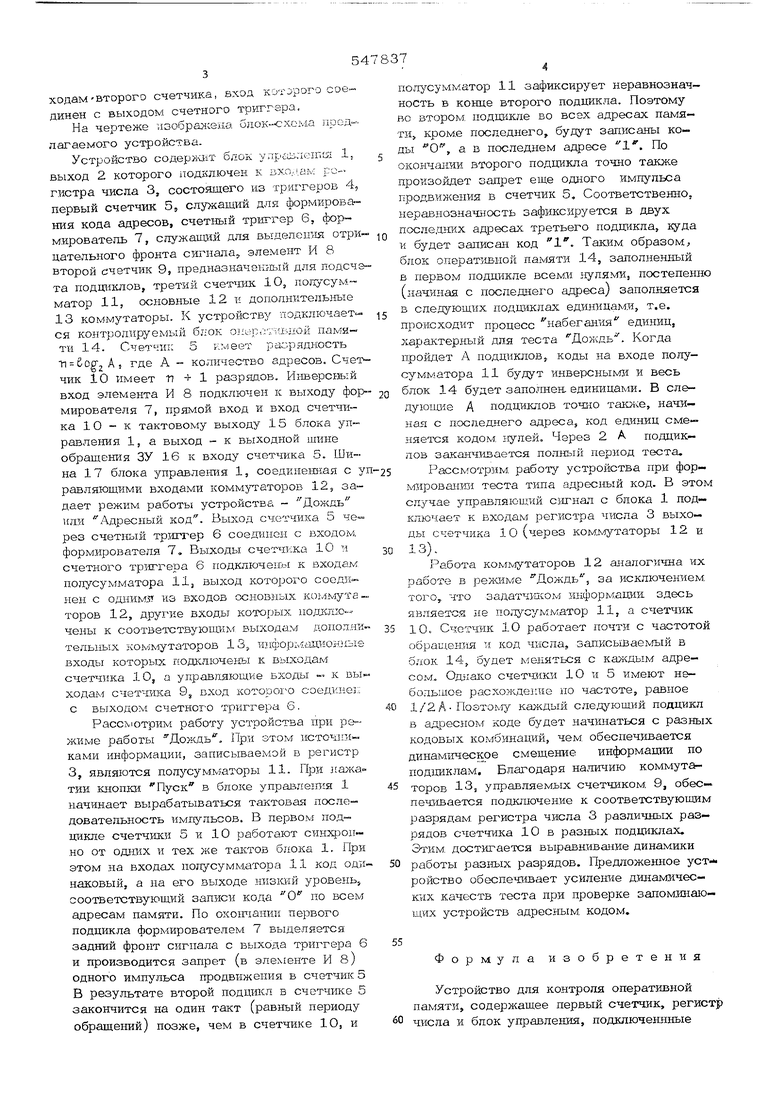

На чертеже изобралюка блок-схема iiocuлагаемого устройства.

Устройство содерйснт бяок yrjjjiai.ieintsi 1. выход 2 которого подключен к Bxo-j.aiv: согистра числа 3, состоящего из триггеров 4, первый счетчик 5s служащий для формирования кода адресов, счетный триггер 6, формирователь 7, служащий для выделения отрицательного фронта сигнала, элемент И 8 второй счетчик 9, предназначенный для подсчета подциклов, третий счетчик 10, полусумматор 11, основные 12 и дополнктелЫ1ые 13 коммутаторы. К устройству подключает ся контролируемый блок олйп,: :;;f.bj.toE нами- ти 14. Счетчик 5 имеет раорядность H og2 А. где А - количество адресов. Счетчик 10 имеет Т) -ь 1 разряд.ов. Инверсьзый вход элемента И 8 подключен к выходу формирователя 7, нрямой вход и вход счетчика 1 О - к тактовому выходу 15 блока управления 1, а выход - к выходной ШИНЕ обращения ЗУ 16 к входу счетчика 5. Шина 17 блока управления 1, соединенная с уравляющими входами коммутаторов 12, задает режим работы устройства - Дождь или Адресный код. Выход счетчика 5 че™ рез счетный триггер 6 соединен с входом, формирователя 7, Выходы счетчика 10 и счетного триггера 6 подключены к входам полусумматора 11, выход которого соеди-нен с ОДНИМ5 из входов основных ко1лмута торов 12, другие входы которых чены к соответствующим выходам дополни тельных комк-гутаторов 13 информ.-жион;чые входы которых подключены к выходам счетчика 10, а управляющие входы - к выходам счетчика 9 вход которо о соединег; с выходом счетного триггера 6.

Рассмотрим работу устройства при ре-жиме работы Дождь, При этом источниками информации, записываемой в регистр 3, являются полусумматоры 11. При нажатии кнопки Пуск в блоке управления 1 начинает вырабатываться тактовая после довательность импульсов. В первом подцикле счетчики 5 и 10 работают синхронно от одних и тех же тактов блока 1. При этом на входах полусумматора 11 код одинаковый, а на его выходе низкий ypoBeHbj соответствующий записи кода О по всем адресам памяти. По oi-coiriamra первого подцикла формирователем 7 выделяется задний фронт сигнала с выхода триггера 6 и производится запрет (в элементе И 8) одного импульса продвижения в счетчик 5 В результате второй ноддикл в счетчике 5 закончится на один такт (равный периоду обращений) позже, чем в счетчике 1О, и

пол сумматор 11 зафиксирует неравнозначность в конце второго подцикла. Поэтому во втором, нодидкле во всех адресах памяти, кром,е последнего, будут записаны коды , а в последнем адресе I. По окончшши второго подцикла точно также произойдет запрет еже одного импульса продвижения в счетчик 5„ Соответственно, неравнозначность зафиксируется в двух ПЭследних адресах третьего подцикла, куда и будет записан код 1. Таким образом блок оперативной памяти 14, заполненный в первом подникле всеми нулями, постепенно (начиная с последнего адреса) заполняется

в следующих подциклах единицами, т.е. происходит процесс набегания единиц, характерный для теста Доулдь. Когда пройдет А подциклов, коды на входе полусумматора 11 будут инверсными и весь

3 блок 14 будет заполнен, единицами. В следующие А подциклов точно такнсе, начиная с ПОследнего адреса5 код единиц сменяется кодом, нулей. Через 2 А подцик- лов заканчивается полный период теста, 5Рассмотрим, работу устройства при фор-

мировалии теста типа адресный код. В этом случае управляющий ci-пгнат с блока 1 подключает к входам регистра числа 3 выходы счетчика Ю через коммутаторы 12 и

0 13).

Работа коммутаторов 12 аналогична их работе в режиме Дождь, за исключением, тогОу что задатчшюм информ,ации здесь является не полусумм,атор 11, а счетчик

5 10. Счеогчик 10 работает почти с частотой обращения и код числа, записываемый в блок 14j будет меняться с каждым адресом,. Однако счетчики 10 и 5 имеют небольшое расхождение по частоте, равное

0 1/2 А-Поэтому каждый сле,цующий подцикл в адресном коде будет начинаться с разных кодовых комбинаций, чем, обеснечивается динамическое смещение информации по нодциклам. Благодаря наличию коммута 5 торов 13, управляемых счетчиком 9, обес- печ1шается подключение к соответствующим разрядам, регистра числа 3 различных разрядов счетчика 10 в разных подциклах. Этим, достигается выравнивание динамики

50 работы разных разрядов. Предложенное устройство обеспечивает усиление динамических качеств теста при проверке запоминающих устройств адресным кодом.

Формула изобретения

Устройство для контроля оперативной памяти, содержащее первый счетчик, регистр числа и блок управления, подключеннные

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля оперативной памяти | 1980 |

|

SU955208A1 |

| Устройство для контроля блоков оперативной памяти | 1983 |

|

SU1161993A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1022225A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1001182A1 |

| Устройство для контроля оперативной памяти | 1982 |

|

SU1024990A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1014041A1 |

| Устройство для контроля блоков оперативной памяти | 1980 |

|

SU924758A1 |

| Устройство для контроля блоковОпЕРАТиВНОй пАМяТи | 1979 |

|

SU841064A1 |

| Устройство для контроля памяти | 1981 |

|

SU1001180A1 |

| Устройство для контроля блоков памяти | 1986 |

|

SU1444896A1 |

Авторы

Даты

1977-02-25—Публикация

1975-11-20—Подача