(54) АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

| название | год | авторы | номер документа |

|---|---|---|---|

| АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1995 |

|

RU2106009C1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1720160A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| ИНТЕГРИРУЮЩИЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ | 1991 |

|

RU2012130C1 |

| Цифроаналоговый измеритель средней частоты | 1991 |

|

SU1775678A1 |

| Аналого-цифровой преобразователь сАВТОМАТичЕСКОй КОРРЕКциЕй Нуля | 1979 |

|

SU805490A1 |

| Двухканальный аналого-цифровой преобразователь | 1983 |

|

SU1106010A1 |

| Устройство для определения условного математического ожидания | 1981 |

|

SU1003097A1 |

| Аналого-цифровой преобразователь | 1982 |

|

SU1102033A1 |

1

Устройство относится к вычислительной и измерительной технике.

Известны аналого-цифровые преобразователи поразрядного уравновешивания, содержащие цифроаналоговый преобразователь, реверсивный счетчи элемент сравнения и логические элементы. Аналого-цифровые преобразователи в зависимости от знака ошибки, формируемой элементом сравнения сохраняют или отключают данный разряд l..

Однако наличие генератора импульсов, счетчика и логических элементов уменьшает надежность преобразования быстродействие, усложняет такое устройство.

Наиболее близким к предлагаемому по технической сущности является аналого-цифровой преобразователь, содержащий, элемент сравне«ия, первый вход которого соединен с выходом преобразователя цифра-аналог, подключенного к выходам разрядов, а выход элемента сравнения подключен к первому входу первого элемента совпадения каждого разряда, выход которого соединен с входом установки в ноль триггера запоминания соответствующего разряда, первый вход втррого элемента совпадения каждого разряда соединен с выходом блока задержки 2 .

Однако наличие генератора импульсов усложняет известный преобразователь, увеличивает габариты. При этом сам генератор тактируюии5Г импульсов, особенно на частоты порядка 15-20 МГц, являясь достаточно сложным устройством, служит источником наводок на аналоговые цепи, что требует дополнительного усложнения преобразователя для устранения этих наводок. Соединения триггера запоминания каждого разряда со всеми предшествующими схемами совпадения усложняет преобразователь, уменьшает (йастродействие, создает значительную нагрузку на триггера. Кроме , налише дополнительной шины Сброс приводит к дополнительному усложнению логических цепей управления, так как установка в ноль триггеров задействована.

Цель изобретения - увеличение быстродействия.

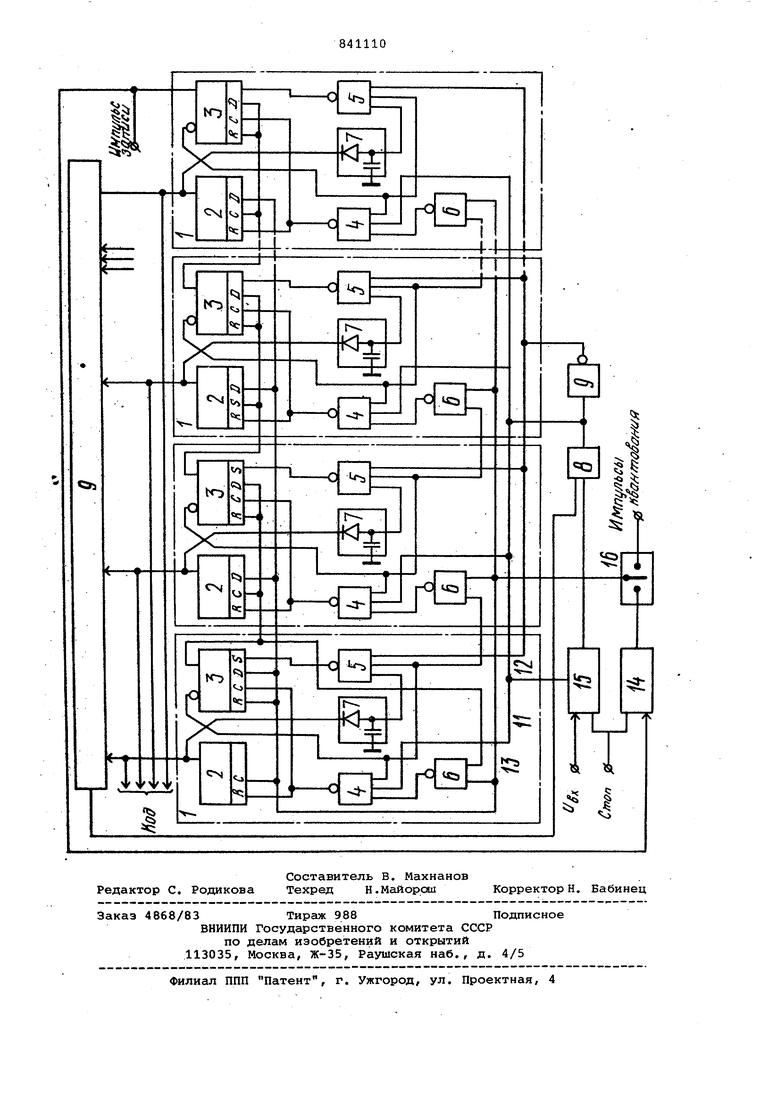

Поставленная цель достигается тем, что в аналого-цифровой преобразователь, содержащий элемент сравнения, первый вход которого соединен с выходом пр еобразователя цифра-ана лог, подключенного к выходам разрядов, выход элемента сравнения подключен к первому входу, первого элемента совпадения каждого разряда, выход которого соединен с входом установки в ноль триггера запоминания соответствующего разряда, первы вход второго элемента совпадения каждого разряда соединен с выходом блока задержки, введены блок возвра та, ключ, переключатель и в каждый разряд триггер управления и третий элемент совпадения, выход которого соединен с вторым входом первого элемента совпадения данного разряда третий вход которого подключен к нулевому выходу триггера управления и второму входу второго элемента совпадения данного разряда и первом вхрду третьего элемента совпадения следующего разряда, кроме младшего разряда, вторые входы третьих элеме тов совпадения всех разрядов, счетный вход триггера запоминания, вход установки в ноль триггера управления младшего разряда и йнформационные входы триггеров запоминания остальных разрядов соединены с выхо дом переключателя, первый вход кото рого подключен к шине Импульсы квантования, второй - к выходу бЛО ка возврата, первый вход которого соединен с единичным выходом тригге ра управления старшего разряда и шиной Импульс записи, второй вход с шиной Стоп и первым входом ключ второй вход которого соединен со входной шиной, а выход подключен к второму входу элемента сравнения, выход которого через инвертор соеди нен с третьим входом второго элемента совпсщения каждого разряда, выход которого подключен ко входу установки в единицу триггера управления соответствующего разряда, единичный выход которого, кроме ста шего разряда, подключен к счетному входу триггера запоминания и ко входу установки в ноль и информационному входу триггера управления следующего .разряда, а в младшем раз ряде также к первому входу третьего элемента совпадения, единичный выхо триггера запоминания соединен со входом блока задержки, управляющий вход ключа соединен с выходом элемента сравнения, а счетный вход три гера управления каждого разряда подключен к выходу первого элемента совпадения. На чертеже представлена блок-схе аналого-цифрового преобразователя. Предлагаемый аналого-цифровой преобразователь содержит разряды преобразователя 1, триггер 2 запоми нания, триггер 3 управления, первый элемент 4 совпадения, второй элеме 5 совпадения, третий элемент б совп дения, блок 7 задержки, элемент 8 сравнения, инвертор 9, преобразователь 10 цифра-аналог, шина 11 вычитания, шина 12 сложения, шина 13 сбросазапуска, блок 14 возврата, ключ 15, переключатель 16. Предлагаемый преобразователь работает как в режиме внешней синхронизации , так и в автоколебательном режиме . В автоколебательном режиме выход блока 14 возврата через ключ 15 соединяется с шиной сброса-запуска. При эт.ом преобразователь сам является генератором импульсов квантования, частота которого определяется задержкой применяемых микросхем. В режиме внешней синхронизации, когда на клемме Импульса квантования присутствует нулевой потенциал, а команда Стоп отсоединяет входной сигнал от элемента сравнения 8, триггеры управления всех разрядов устанавливаются в О, на выходе третьих элементов совпадения появляется высокий потенциал, В случае, если триггер запоминания какого-либо разряда находится в 1, то на неинверсном входе элемента сравнения появляется напряжение от включённого разряда преобразователя цифра-аналог, на выходе элемента сравнения, а следовательно, на шине вычитания появляется высокий потенциал. При этом на выходе первых элементов совпадения, присутствует низкий потенциал, который заставляет возвратиться в ноль триггер запоминания. При отключении команды Стоп и с приходом переднего фронта импульса квантования включается триггер запоминания, а следовательно, и напряжения старшего разряда. При включении разряда возможны два случая, когда входной сигнал больше сигнала с преобразователя цифра-анагол и когда входной сигнал меньше сигнала с праоЪразователя. В первом случае на шине вычитания 11 появляется высокий потенциал, а на выходе первого элемента совпадения - низкий, который отрицательным фронтом возвращает триггер запоминания данного разряда в исходное положение. При этом на шине вычитания оказывается низкий потенциал, на выходе первого элемента совпгщения появляется высокий потенциал, который перебрасывает в 1 триггер управления своего разряда. Во втором случае на выходе инвертора 9, а следовательно, и на шине 12 сложения присутствует высокий потенциал. Через время, определяемое параметрами блока задержки, на выходе второго элемента совпадет ния появляется низкий потенциал, который перебрасывает триггер управления данного разряда в 1. Нулевой выход триггера управления запрещает работу первого и второго элементов совпадения своего разряда и разрешает работу первого и второго элемента совпадения следующего разряда Единичный выход триггера управления Положительным фронтом перебрасывает триггер запоминания следующего разряда, цикл повторяется. Единичный выход триггера управления последнего разряда выдает импульс записи найденного цифрового кода. С окончанием импульса квантов ния триггеры возвращаются в исходно положение, и схема готока в следующему преобразованию. При работе устройства в автоколе тельном режиме по переднему фронту триггера управления последнего разряда запускается блок 14 возврата, через определенное время снимающий высокий потенциал с шины 13, на кот рую через время возврата снова пост пает с блока возврата импульс квантования. повторяется. Формула изобретения Аналого-цифровой преобразователь содержащий элемент сравнения, первы вход которого соединен с выходом преобразователя цифра-аналог,подклю ченного к выходам разрядов, выход элемента сравнения подключен к перво му входу первого элемента совпадения каждого разряда, выход которого соединен с входом установки в ноль триг гера запоминания соответствующего разряда, первый вход второго элемент совпадения каждого разряда соединен с выходом блока задержки, о т л и ч ю щ и и с я тем, что, с целью увеличения быстродействия, в него введены блок возврата, ключ, переключатель и в каждый разряд триггер управ ления и третий элемент совпадения, выход которого соединен с вторым входом первого элемента совпадения данного разряда, третий вход которог подключен к нулевому выходу триггера управления и второму входу второго элемента совпадения данного разряда и первому входу третьего элемента совпадения следующего разряда, кроме младшего разряда, вторые входы третьих элементов совпадения всех разрядов,счетный вход триггера запсниннания, вход установки в ноль триггера управления младшего разряда и информационные входы триггеров запоминания остальных разрядов соединены с выходом переключателя, первый вход которого подключен к шине Импульсы кванте- вания,второй - к выходу блока воз- . врата, первый вход которого соединен с единичным выходом триггера управления старшего разряда и шиной Импульс записи, второй вход - с шиной Стоп и первым входом ключа, второй вход которого соединен со входной шиной, а выход подключен к второму .входу элемента сравнения, выход которого через инвертор соединен с третьим входом второго элемента совпадення каждого разряда, выход которого подключен ко входу установки в единицу триггера управления соответствующего разряда, единичный выход которого, кроме старшего разряда, подключен к счетному входу триггера запоминания и ко входу установки в ноль и информационному входу триггера управления следующего разряда, а в младшем разряде также к первому входу третьего элемента совпадения, единичный выход триггера запоминания соединен со входом блока задержки, управляющий вход ключа соединен с выходом элемента сравнения, а счетный вход триггера управления каждого разряда подключен к выходу первого элемента совпадения. Источники .информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР 447825, кл. Н 03 К 13/17, 1973. 2.Авторское свидетельство СССР №235416, кл. Н 03 К 13/17, 1967 (прототип).

Авторы

Даты

1981-06-23—Публикация

1979-08-08—Подача