1

Изобретение относится к микроэлектронике, в частности к разработкам интегральных схем на МДП-транзисторах.

Известно, что для улучшения ряда параметров (уменьшение емкости диффузионных шин, стабилизация величины порогового напряжения и др) интегральных устройств на МДП-транзисторах необходимо обеспечить смещение потенциала подложки относительно истоковой (общей) шины устройства

Недостаток известных устройств в том, что требуется специальный канал питания для смещения подложки, что усложняет устройство.

Известно устройство автоматического смещения подложки, которое включает накопительный конденсатор между МДП-транзистором и инвертором, образованным управляющим и нагрузочным транзисторами и является источником импульсов. Во время действия импульсов конденсатор заряжается, а после прекращения импульса он разряжается на емкость подложки относительно общей шины Г .

Недостатком известного устройства является низкое напряжение смещения годложки.

Максимальное напря жение смещения подложки, которое может быть достигнуто в этом устройстве, меньше напряжения питания примерно на величину двух пороговых напряжений транзистора. Это связано с тем, что при заряде конденсатора имеется падение напряжения на транзисторе, которое не меньше порогового напряжения (так как зат0вор транзистора подключен к его стоку). При разряде конденсатор должен перезарядить емкость затвора этого транзистора, напряжение на котором равно пороговому напряжению. Так как 5 пороговое напряжение составляет примерно 0,7-1,0 В , то известное устройство при низковольтном питании (5 в) не может обеспечить величину напряжения смещения подложки более

0 2,0-2,5 В.

в ряде случаев такая величина напряжения смещения может оказаться недостаточной. Например, может быть 25 необходимо дальнейшее снижение емкостей диффузионных шин, или компенсация технологического разброса параметров транзисторов и т.д.

Цель изобретения - увеличение напряжения смещения подложки.

Поставленная цель достигается тем, что в устройство автоматического смещения подложки,содержащее накопительный конденсатор,один вывод которого подключен к выходной шине и к стоку и затвору транзистора заряда,исток кото рого подключен к общей шине,а второй вывод - к стоку транзистора разряда затвор которого подключен ко входной шине, а исток - к общей шине, введен каскад с емкостной положительной обратной связью, затвор управляющего транзистора которого подключен ко входной шине, и элемент связи, подключенный между стоком транзистора разряда и затвором нагрузочного транзистора каскада с емкостной положительной обратной связью.

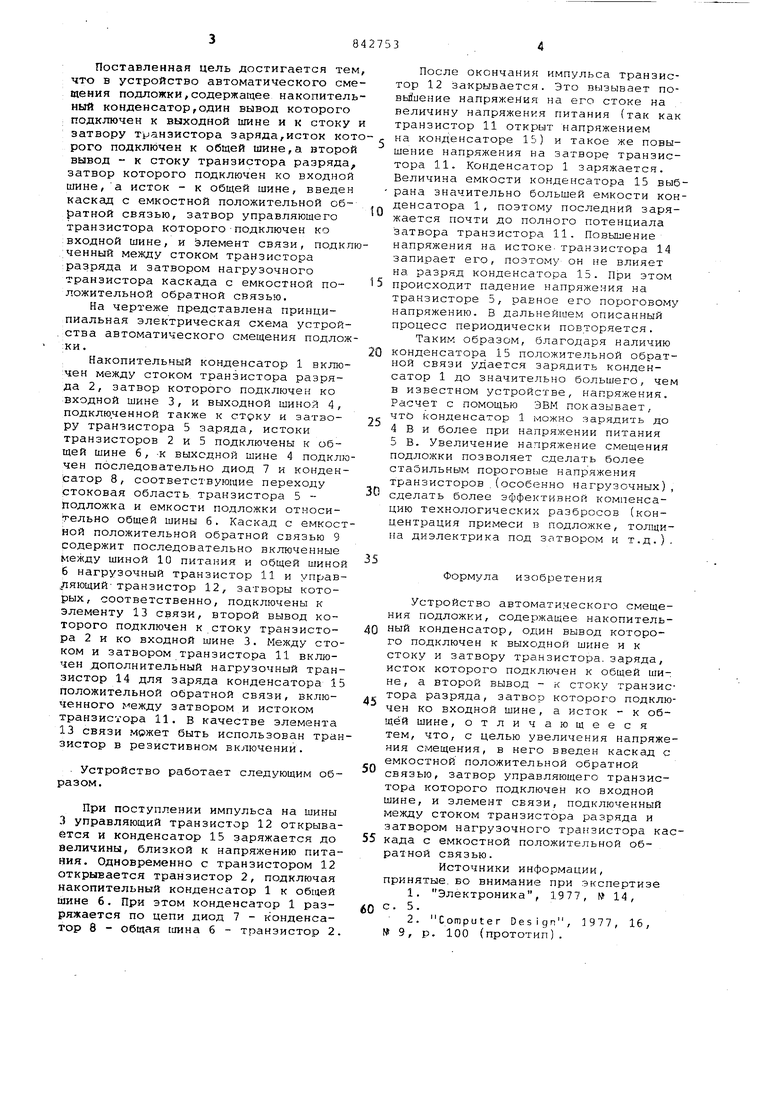

На чертеже представлена принципиальная электрическая схема устройства автоматического смещения подложки.

Накопительный конденсатор 1 включен между стоком транзистора разряда 2, затвор которого подключен ко входной шине 3, и выходной шиной 4, подключенной также к стрку и затвору транзистора 5 заряда, истоки транзисторов 2 и 5 подключены к общей шине 6, -к выходной шине 4 подключен последовательно диод 7 и конденсатор 8, соответствующие переходу стоковая область транзистора 5 подложка и емкости подложки относительно общей шины 6. Каскад с емкостной положительной обратной связью 9 содержит последовательно включенные ме5кду шиной 10 питания и общей шиной б нагрузочный транзистор 11 и управ1яющий-транзистор 12, затворы которых, соответственно, подключены к элементу 13 связи, второй вывод которого подключен к.стоку транзистора 2 и ко входной шине 3. Между стоком и затвором транзистора 11 включен дополнительный нагрузочный транзистор 14 для заряда конденсатора 15 положительной обратной связи, включенного между затвором и истоком транзистора 11. В качестве элемента 13 связи может быть использован транзистор в резйстивном включений.

. Устройство работает следующим образом.

При поступлении импульса на шины 3 управляющий транзистор 12 открывается и конденсатор 15 заряжается до величины, близкой к напряжению питания. Одновременно с транзистором 12 открывается транзистор 2, подключая накопительный конденсатор 1 к общей шине 6. При этом конденсатор 1 разряжается по цепи диод 7 - конденсатор 8 - общая шина б - транзистор 2.

После окончания импульса транзистор 12 закрывается. Это вызывает поВЕ йиение напряжения на его стоке на . величину напряжения питания (так как транзистор 11 открыт напряжением на конденсаторе 15) и такое же повышение напряжения на затворе транзистора 11. Конденсатор 1 заряжается. Величина емкости конденсатора 15 выбрана значительно большей емкости конденсатора 1, поэтому последний заряжается почти до полного потенциала затвора транзистора 11. Повышение напряжения на истоке- транзистора 14 запирает его, поэтому он не влияет на разряд конденсатора 15. При этом происходит падение напряжения на транзисторе 5, равное его пороговому напряжению. В дальнейшем описанный процесс периодически повторяется.

Таким образом, благодаря наличию конденсатора 15 положительной обратной связи удается зарядить конденсатор 1 до значительно большего, чем в известном устройстве, напряжения. Расчет с помощью ЭВМ показывает, что конденсатор 1 можно зарядить до

4В и более при напряжении питания

5В. Увеличение напряжение смещения подложки позволяет сделать более стабильным пороговые напряжения транзисторов .(особенно нагрузочных), сделать более эффективной компенсацию технологических разбросов (концентрация примеси в подложке, толщина диэлектрика под затвором и т.д.).

Формула изобретения

Устройство автоматического смещения подложки, содержащее накопительный конденсатор, один вывод которого подключен к выходной шине и к стоку и затвору транзистора, заряда, исток которого подключен к общей шиг не, а второй вывод - к стоку транзистора разряда, затвор которого подключен ко входной шине, а исток - к общей шине, отличающееся тем, что, с целью увеличения напряжения смещения, в него введен каскад с емкостной положительной обратной связью, затвор управляющего транзистора которого подключен ко входной шине, и элемент связи, подключенный между стоком транзистора разряда и затвором нагрузочного транзистора какада с емкостной положительной обратной связью.

Источники информации, принятые, во внимание при экспертизе

1. Электроника, 1977, № 14, с. 5.

2. Computer Design, 1977, 16, № 9, p. 100 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сигналов выборки адресов | 1981 |

|

SU1003141A1 |

| Устройство автоматического смещения | 1981 |

|

SU995673A1 |

| Адресный усилитель | 1982 |

|

SU1062786A1 |

| Выходное буферное устройство | 1980 |

|

SU908230A1 |

| Формирователь напряжения смещения подложки для интегральных схем | 1986 |

|

SU1322374A1 |

| Устройство задержки импульсов | 1977 |

|

SU680163A1 |

| Выходное устройство | 1978 |

|

SU771874A1 |

| ФОТОПРИЕМНЫЙ ИНТЕГРАЛЬНЫЙ ЭЛЕМЕНТ ПАМЯТИ | 1993 |

|

RU2043665C1 |

| Управляемый инвертор на мдп-транзисторах | 1976 |

|

SU641655A1 |

| Устройство автоматического смещения подложки интегральной схемы | 1982 |

|

SU1022270A1 |

Авторы

Даты

1981-06-30—Публикация

1979-01-24—Подача