Изобретение относится к обучающим устройствам и может быть использовано для отработки навыков микропрограммирования ,

Цель изобретения - расширение дидактических возможностей устройства за счет реализации ускоренного умножения введением операндов, над которыми производятся действия, непосредственно в состав микрокоманд.

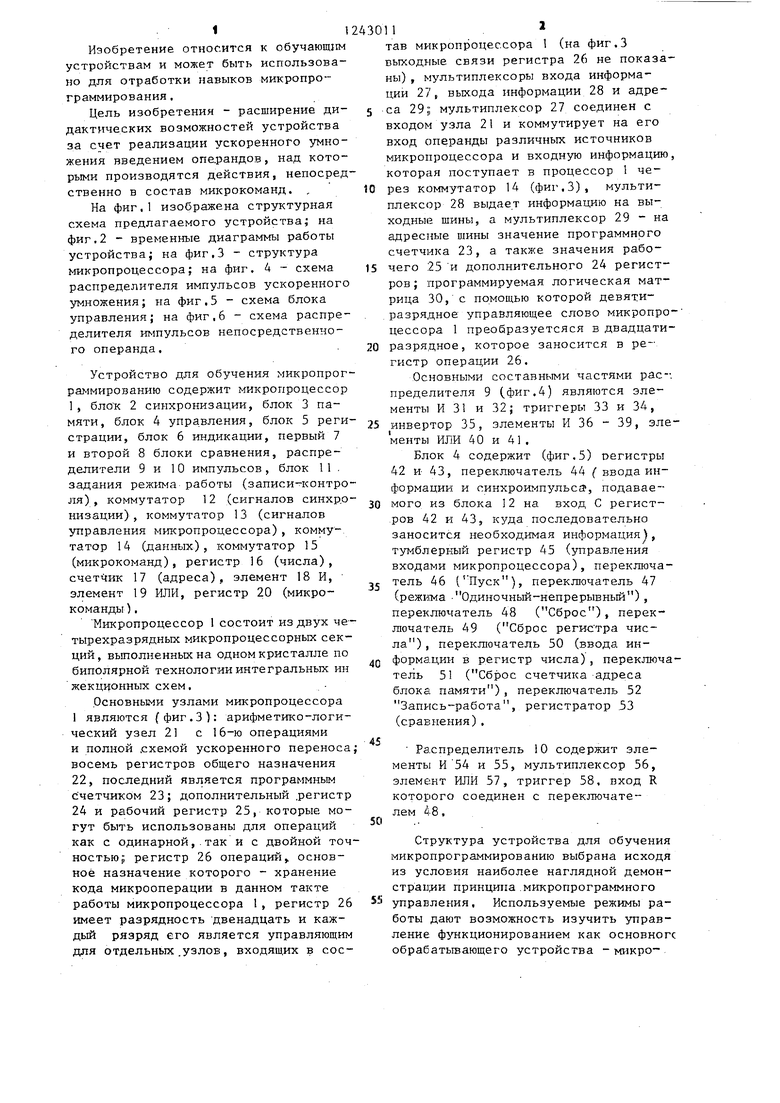

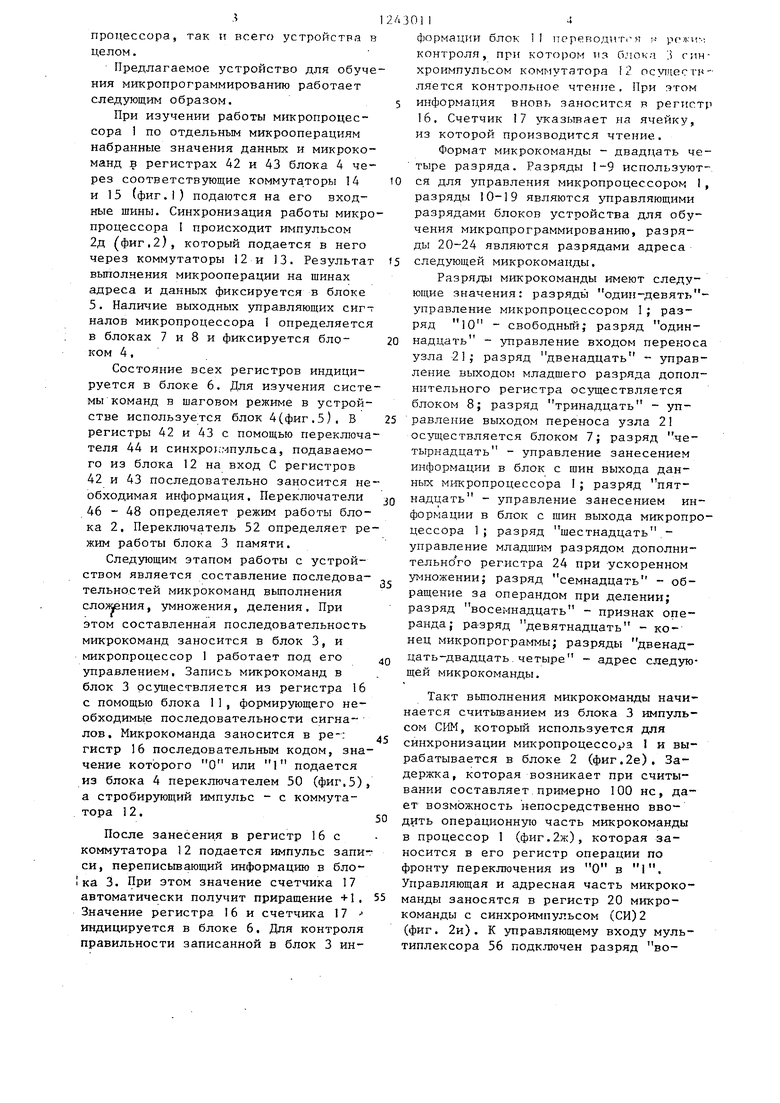

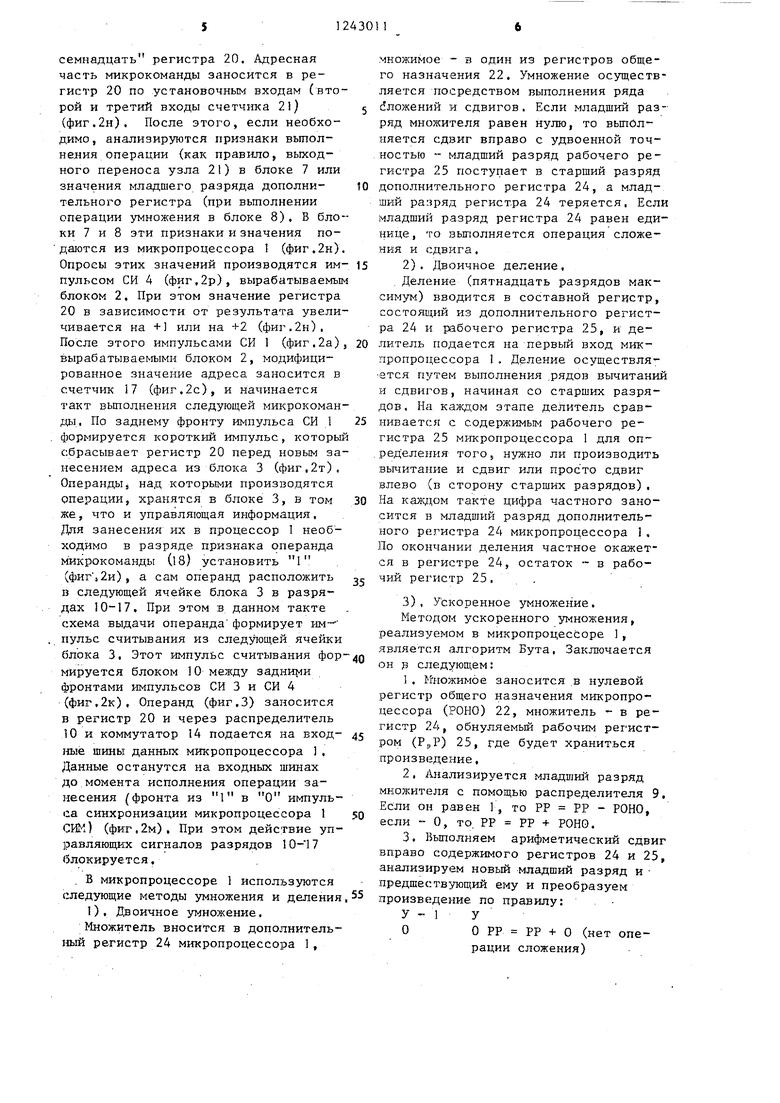

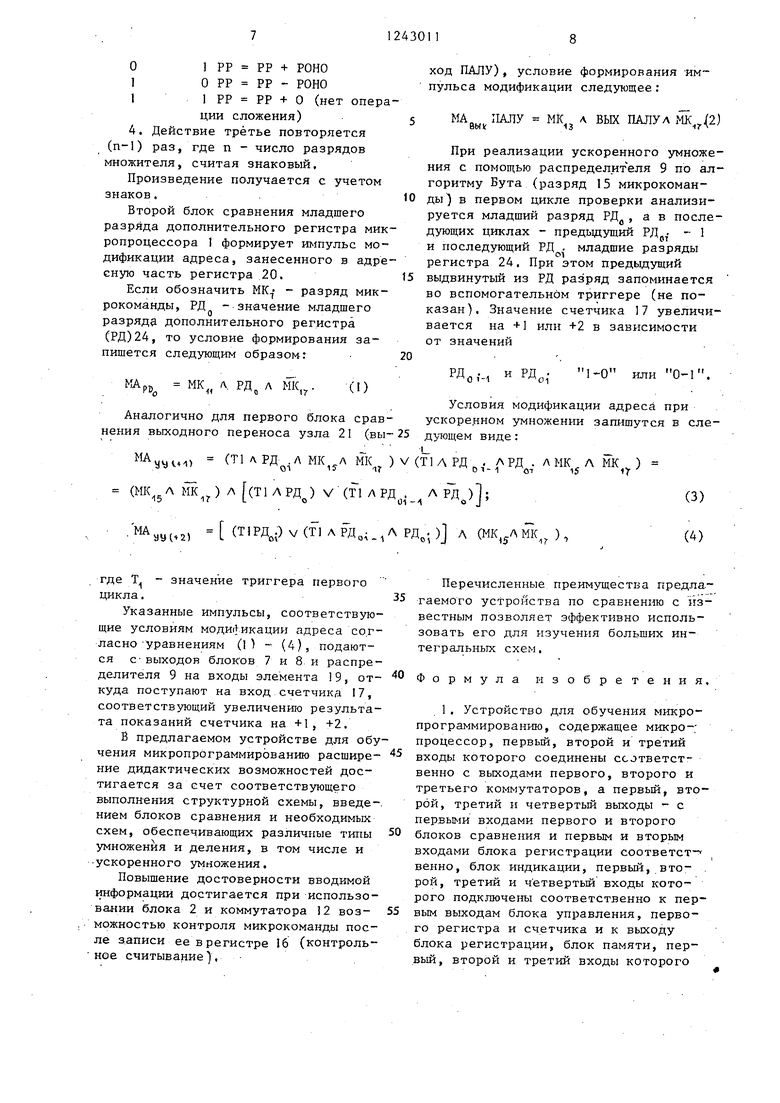

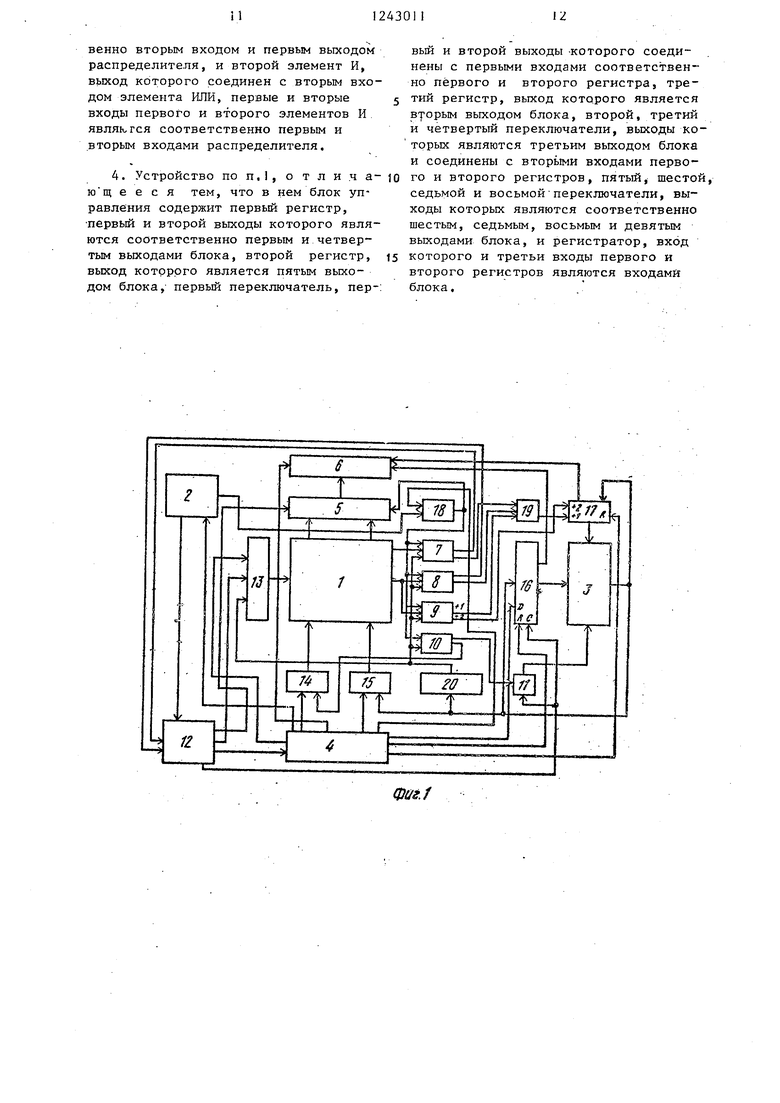

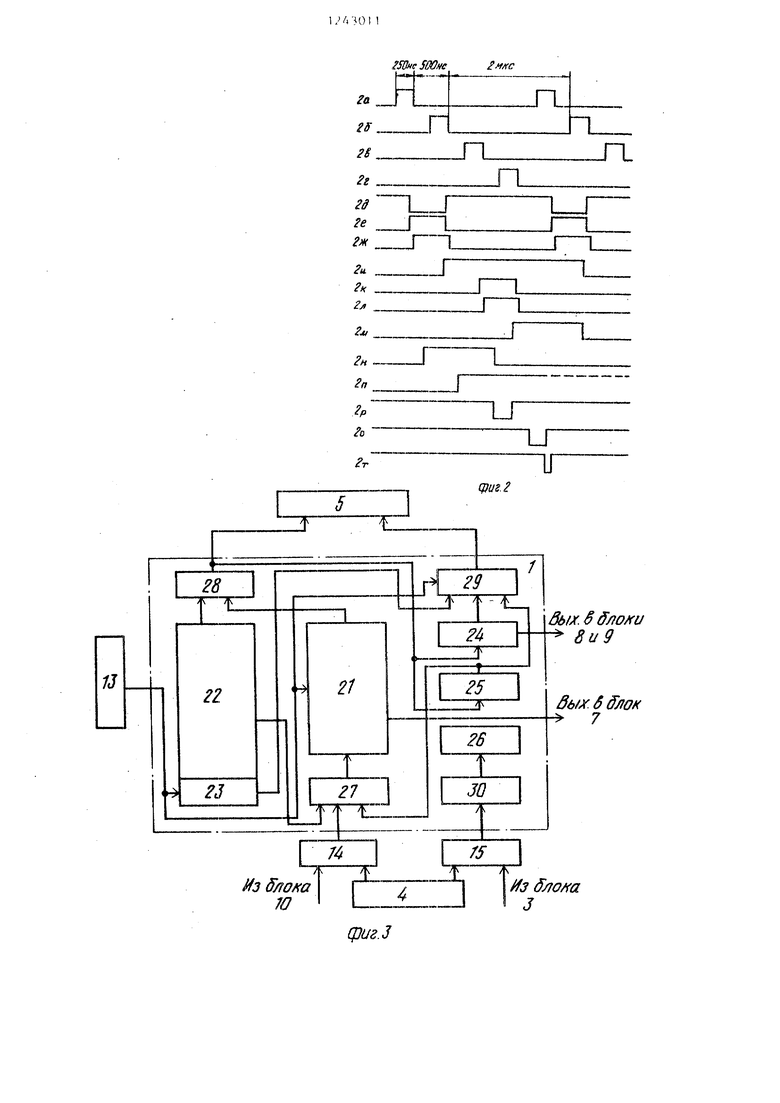

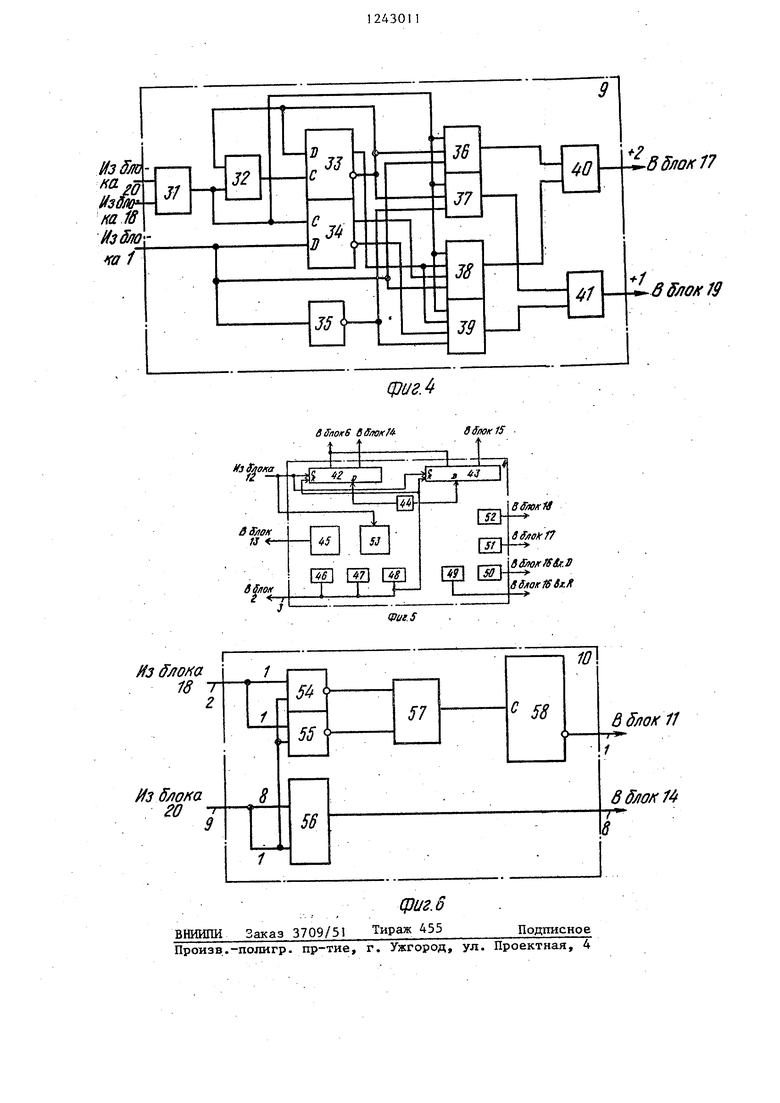

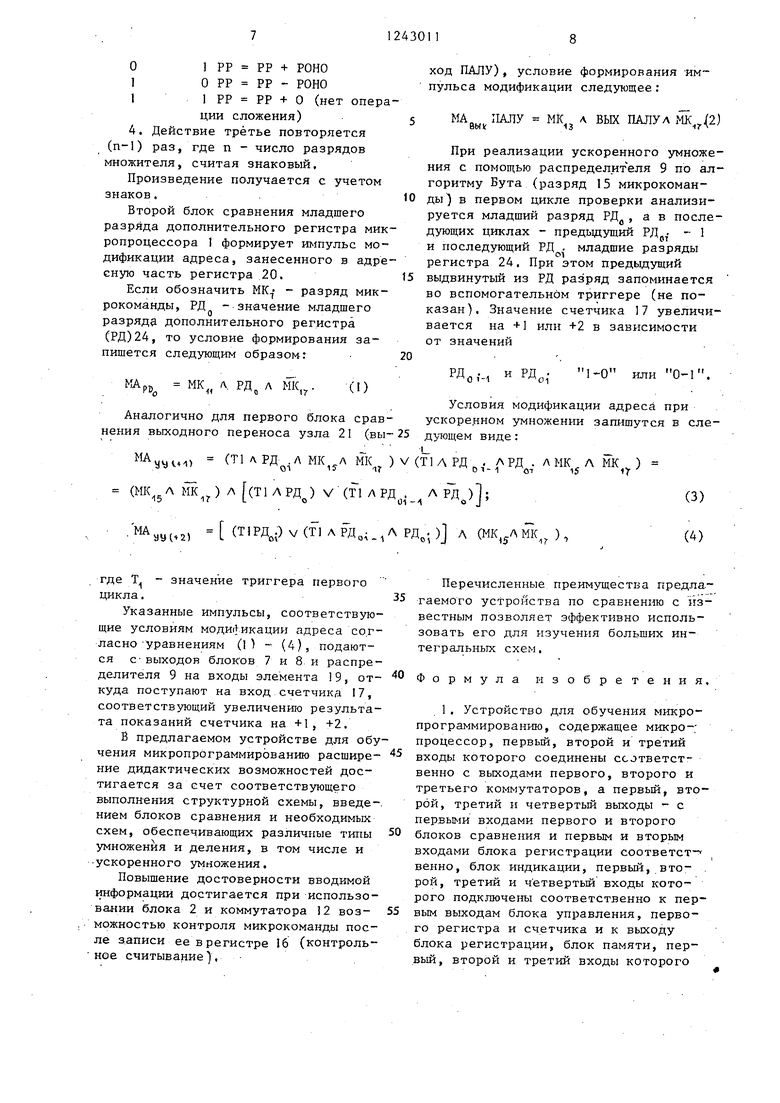

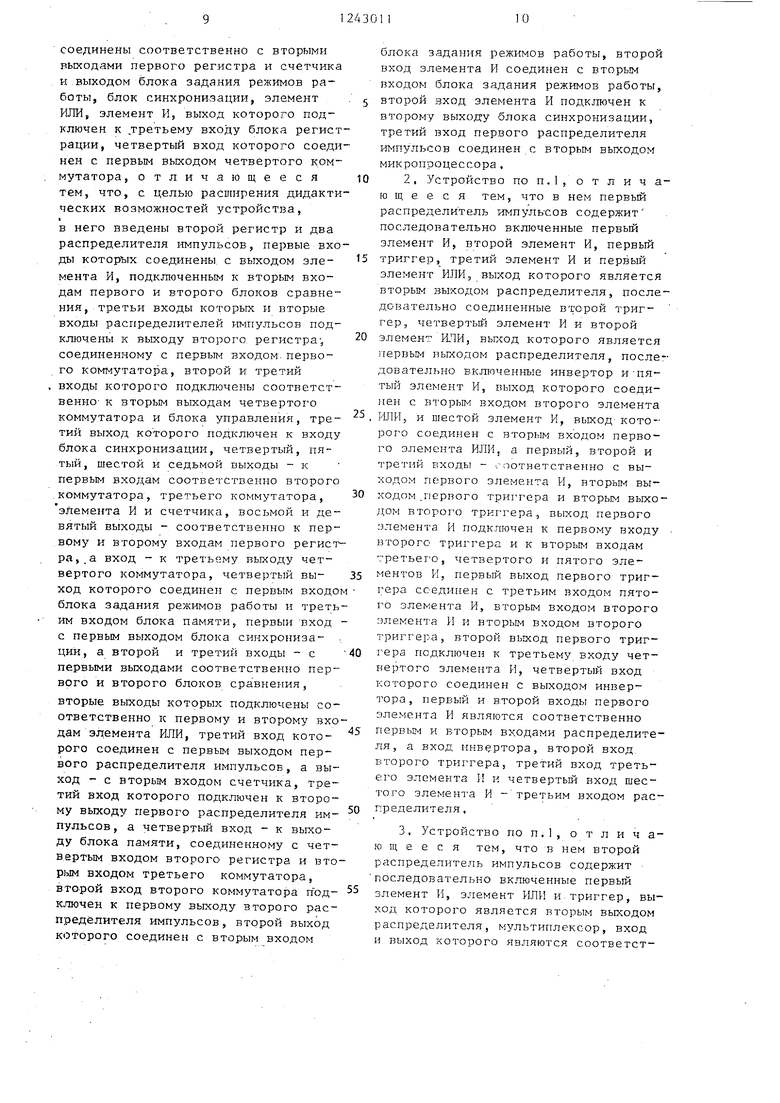

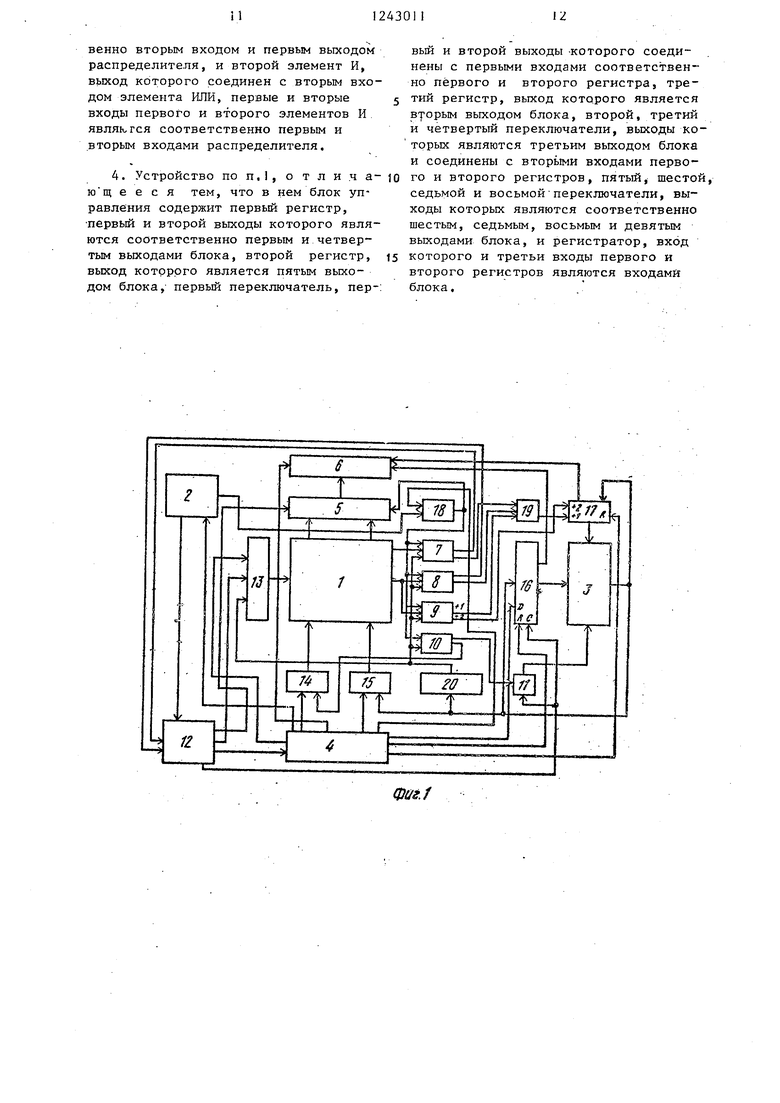

На фиг,1 изображена структурная схема предлагаемого устройства; на фиг.2 - временные диаграммы работы устройства; на фиг.З - структура микропроцессора; на фиг. А - схема распределителя импульсов ускоренного умножения; на фиг.5 - схема блока управления; на фиг,6 - схема распределителя импульсов непосредственного операнда.

Устройство для обучения микропрограммированию содержит микропроцессор 1 , бло к 2 синхронизации, блок 3 памяти, блок 4 управления, блок 5 регистрации, блок 6 индикации, первый 7 и второй 8 блоки сравнения, распределители 9 и 10 импульсов, блок 11 . задания режима работы (записи-контроля) , коммутатор 12 (сигналов синхр.о низации), коммутатор 13 (сигналов управления микропроцессора), комму-, татор 14 (данных), коммутатор 15 (микрокоманд), регистр 16 (числа), счетчик 17 (адреса), элемент 18 И, элемент 19 ИЛИ, регистр 20 (микрокоманды ).

Микропроцессор 1 состоит из двух четырехразрядных микропроцессорных секций, выполненных на од ном кристалле по биполяршой технологии интегральных ин жекционных схем.

Основными узлами микропроцессора 1 являются (фиг.З): арифметико-логический узел 21 с 16-ю операциями и полной .схемой ускоренного переноса восемь регистров общего назначения 22, последний является программным Счетчиком 23; дополнительный .регистр 24 и рабочий регистр 25, которые могут быть использованы для операций как с одинарной,.так и с двойной точностью; регистр 26 операций основное назначение которого - хранение кода микрооперации в данном такте работы микропроцессора 1, регистр 26 имеет разрядность двенадцать и каждый рязряд его является управляющим для отдельных .узлов, входящих в состав микропроцессора 1 (на фиг.З выходные связи регистра 26 не показаны) , мультиплексоры входа информации 275 выхода информации 28 и адреса 29;; мультиплексор 27 соединен с входом узла 21 и коммутирует на его вход операнды различных источников микропроцессора и входную информацию, которая поступает в процессор I через коммутатор 14 (фиг.З), мультиплексор 28 выдает информацию на выходные шины, а мультиплексор 29 - на адресные шины значение программного счетчика 23, а также значения рабочего 25 и дополнительного 24 регистров ; программируемая логическая матрица 30, с помощью которой девяти- . разря.п,ное управляющее слово микропро- цессора 1 преобразуетсяся в двадцатиразрядное, которое заносится в регистр операции 26.

Основными составными частями распределителя 9 (фиг.4) являются элементы И 31 и 32; триггеры 33 и 34,

инвертор 35, элементы И 36 - 39, элементы ИЛИ 40 и 41.

Блок 4 содержит (фиг.5) регистры 42 и 43, переключатель 44 С ввода информации и синхроимпульсз, подаваемого из блока 2 на вход С регистров 42 и 43, куда последовательно заносится необходимая информация, тумблерный регистр 45 (управления входами микропроцессора), переключатель 46 ( Пуск), переключатель 47 (режима - Одиночный-непрерывньш), переключатель 48 (Сброс), переключатель 49 (Сброс регис тра числа) , переключатель 50 (ввода информации в регистр числа), переключатель 51 (Сброс счетчика адреса блока памяти), переключатель 52 Запись-работа, регистратор 53 (сравнения).

Ра.спределитель 10 содержит элементы И 54 и 55, мультиплексор 56, элемент ИЛИ 57, триггер 58. вход R которого соединен с переключателем 48. ..

Структура устройства для обучения микропрограммированию выбрана исходя из УСЛОЕ1ИЯ наиболее наглядной демон- страи ии принципа .микропрограммного управления. Используемые режимы работы дают возможность изучить управление фз-тскционированием как основногс обрабатьгоающего устройства -микрол

процессора, так и всего устройства в целом.

Предлагаемое устройство для обучения микропрограммированию работает следующим образом.

При изучении работы микропроцессора по отдельным микрооперациям набранные значения данных и микрокоманд в регистрах 42 и 43 блока 4 через соответствутощие коммута.торы 14 и 15 (фиг.1) подаются на его входные шины. Синхронизация работы микропроцессора I происходит импульсом 2д (фиг,2), который подается в него через коммутаторы 12 и 13. Результат выполнения микрооперации на шинах адреса и данных фиксируется в блоке 5. Наличие выходных управляющих сигт налов микропроцессора 1 определяется в блоках 7 и 8 и фиксируется блоком 4,

Состояние всех регистров индицируется в блоке 6. Для изучения системы команд в шаговом режиме в устройстве используется блок 4(фиг.5), В регистры 42 и 43 с помощью переключателя 44 и синхроь мпульса, подаваемого из блока 12 на вход С регистров 42 и 43 последовательно заносится необходимая информация. Переключатели 46 - 48 определяет режим работы блока 2, Переключатель 52 определяет режим работы блока 3 памяти.

Следующим этапом работы с устройством является составление последовательностей микрокоманд вьтолнения слолдвния, умножения, деления. При этом составленная последовательность микрокоманд заносится в блок 3, и микропроцессор 1 работает под его управлением. Запись микрокоманд в блок 3 осуществляется из регистра 16 с помощью блока 11, формирующего необходимые последовательности сигналов. Микрокоманда заносится в ре-: гистр 16 последовательным кодом, значение которого О или 1 подается из блока 4 переключателем 50 (фиг.5) а стробирующий импульс - с коммутатора 1 2.

После занесения в регистр 16 с коммутатора 12 подается импульс записи, переписьюающий информацию в блошка 3. При этом значение счетчика 17 автоматически получит приращение +1. Значение регистра 16 и счетчика 17 индицируется в блоке 6. Для контроля правильности записанной в блок 3 ин2Д301I4

формации блок II переводит.-я ь- рсл-и-.: контроля, при котором из О.п.ок.ч . синхроимпульсом коммутатора 2 осутесгн- ляется контрольное чтение. При этом 5 информация вновь заносится в регистр 16. Счетчик 17 называет на ячейку, из которой производится чтение.

Формат микрокоманды - двадцать че- тыре разряда. Разряды 1-9 используют-, 10 ся для управления микропроцессором I, разряды 10-19 являются управляющими разрядами блоков устройства для обучения микропрограммированию, разряды 20-24 являются разрядами адреса (5 следующей микрокоманды.

Разряд, микрокоманды имеют следующие значения: разряды один-девять - управление микропроцессором I; разряд 10 - свободньш; разряд один- 20 надцать - управление входом переноса узла -21; разряд двенадцать - управление выходом младшего разряда дополнительного регистра осзтдествляется

блоком 8; разряд тринадцать - уп- равление выходом переноса узла 2I

осуществляется блоком 7; разряд четырнадцать - управление занесением информации в блок с шин выхода данных микропроцессора 1; разряд пят- надцать - управление занесением информации в блок с шин выхода мржропро- цессора 1; разряд шестнадцать.- управление младшим разрядом дополни- тельнб го регистра 24 при ускоренном умножении; разряд семнадцать - обращение за операндом при делении; разряд восемнадцать - признак операнда,- разряд девятнадцать - конец микропрограммы; разряды двенад- дать-двадцать,четыре - адрес следующей микрокоманды.

Такт вьтолнения микрокоманды начинается считьгоанием из блока 3 импульсом СШ, который используется для

синхронизации микропроцессора I и вырабатывается в блоке 2 (фиг.2е). Задержка, которая возникает при считывании составляет примерно 100 не, дает возможность непосредственно вво-

дить операционную часть микрокоманды в процессор 1 (фиг.2ж), которая заносится в его регистр операции по фронту переключения из О в 1. Управляющая и адресная часть микрокоманды заносятся в регистр 20 микрокоманды с синхроимпульсом (СИ)2 (фиг. 2и). К управляющему входу мультиплексора 56 подключен разряд воемнадцать регистра 20. Адресная асть микрокоманды заносится в реистр 20 по установочным входам (втоой и третий входы счетчика 21) 5 (фиг.2н). После этого, если необхоимо, анализируются признаки вьтол- ения операции (как правило, выходого переноса узла 21) в блоке 7 или значения младшего разряда дополни- 10 тельного регистра (при выполнении операции умножения в блоке 8), В блои 7 и 8 эти признаки и значения по- а:отся из микропроцессора 1 (фиг,2н). Опросы этих значений производятся им- 15 пульсом СИ 4 (фиг,2р), вырабатываемым блоком 2, При этом значение регистра 20 в зависимости от результата увеличивается на +1 или на +2 (фиг.2н). После этого импульсами СИ 1 (фиг,2а)5 20 Bbipa6aTUBaeNn3iMH блоком 2, модифицированное значение адреса заносится в счетчик 17 (фиг.2с), и начинается такт выполнения следующей микрокоман- дьь По заднему фронту импульса СИ 1 25 формируется короткий импульс, который сбрасывает регистр 20 перед новым занесением адреса из блока 3 (фиг,2т). Операнды, над которыми производятся операции, хранятся в блоке 3, в том 30 же, что и управляющая информация, Для занесения их в процессор 1 необходимо в разряде признака операнда микрокоманды О8) установить I (фиг а2и), а сам операнд расположить в следующей ячейке блока 3 в разрядах 10-17, При этом в. данном такте схема выдачи операнда формирует им- пульс считывания из следующей ячейки блока 3, Этот импульс считывания мируется блоком 10 между заднщ и . фронтами импульсов СИ 3 и СИ 4 (фиг,2к). Операнд (фиг.З) заносится в регистр 20 и через распределитель 10 и коммутатор 14 подается на вход- 45 ные шины данных микропроцессора 1, Данные останутся на входных шинах до.момента исполнения операции занесения (фронта из 1 в О импульса синхронизации микропроцессора I 50 сим) (фиг,2м), При этом действие уп- 1равляющих сигналов разрядов 10-17 блокируется,

. В микропроцессоре 1 используются следующие методы умножения и деления,55 I), Лэоичное з ножение. Множитель вносится в дополнительный регистр 24 микропроцессора 1,

множимое - в один из регистров общего назначения 22. Умножение осуществляется посредством выполнения ряда сложений и сдвигов. Если младший разряд множителя равен нулю, то вьтОл- няется сдвиг вправо с удвоенной точностью -- младший разряд рабочего регистра 25 поступает в старший разряд дополнительного регистра 24, а младший разряд регистра 24 теряется. Есл младший разряд регистра 24 равен единице, то вьтолняется операция сложения и сдвига.

2). Двоичное деление.

Деление (пятнадцать разрядов максимум) вводится в составной регистр, состоящий из дополнительного регистра 24 и рабочего регистра 25, и делитель подается на первый вход мик- пропроцессора 1. Деление осуществля- ется путем выполнения .рядов вычитани и сдвигов, начиная со старших разрядов. На каждом этапе делитель сравнивается с содержимым рабочего регистра 25 микропроцессора 1 для определения того, нужно ли производить вычитание и сдвиг или прос то сдвиг влево (в сторону старших разрядов), На каждом такте цифра частного заносится в младший разряд дополнительного регистра 24 микропроцессора 1, По окончании деления частное окажется в регистре 24, остаток - в рабочий регистр 25..

3), Ускоренное умножение.

Методом ускоренного умножения, реализуемом в микропроцессоре 1, является алгоритм Бута. Заключается он э следующем:

1 . {ножимбе заносится .в нулевой регистр общего назначения микропроцессора (РОНО) 22, множитель - в регистр 24, обнуляемый рабочим рег ист- ром (Р,,Р) 25, где будет храниться произведение,

2. лализируется младшиз разряд мкожитсгля с помощью распределителя 9 Если он равен 1, то РР РР - РОНО, если - О, то. РР РР + РОНО.

3.Выполняем арифметический сдви вправо содержимого регистров 24 и 25 анализируем новый младший разряд и предшеств:/ющий ему и преобразуем произведение по правилу:

У - 1 У

О О РР РР + О (нет операции сложения)

01 РР РР + РОНО

1О РР РР - РОНО

1 1 РР РР + О (нет операции сложения)

4. Действие третье повторяется (п-1) раз, где п - число разрядов множителя, считая знаковый.

Произведение получается с учетом знаков.

Второй блок сравнения младшего разряда дополнительного регистра микропроцессора 1 формирует импульс модификации адреса, занесенного в адресную часть регистра 20.

Если обозначить МК - разряд микрокоманды, РД - значение младшего разряду дополнительного регистра (РД)24, то условие формирования запишется следующим образом:

МА

П

МК,, л. РД л МК„.

17

Аналогично для первого блока сравнения выходного переноса узла 21 (выМА

УУ

,,,) (Т1 л РД.Л МК,Л МК ) V (Т А РД ,. ЛРД. л МК л МК )

( МК) л (Т1ЛРД V (T1 АРД.,.ЛРД);

МА

УУ(2)

(ИРД.) V (Т1 ЛРД„.Л РД. ) л (МК,ЛМК ),

где Т - значение триггера первого цикла.

Указанные импульсы, соответствующие условиям модификации адреса согласно уравнениям (I) - (4), подаются с-выходов блоков 7 и 8 и распределителя 9 на входы элемента 19, от- куда поступают на вход счетчика I7, соответствующий увеличению результата показаний счетчика на +1, +2.

В предлагаемом устройстве для обучения микропрограммированию расшире- ние дидактических возможностей достигается за счет соответствующего выполнения структурной схемы, введением блоков сравнения и необходимых схем, обеспечивающих различные типы умножения и деления, в том числе и ускоренного умножения.

Повышение достоверности вводимой информации достигается при использовании блока 2 и коммутатора 12 воз- можностью контроля микрокоманды после записи ее в регистре 16 (контрольное считывание).

ход ПАЛУ), условие формирования импульса модификации следующее:

fA

ЙЫ

Г1А.ПУ МК л ВЫХ ПАЛУ л МК (2)

13

При реализации ускоренного умножения с помощью распределит еля 9 по алгоритму Бута (разряд 15 микроксман- 10 ды) в первом цикле проверки анализируется младший разряд РД, а в последующих циклах - предьщущий РД,. - 1 и последующий РД . младшие разряды регистра 24. При этом предьщущий t5 выдвинутый из РД разряд запоминается во вспомогательном триггере (не показан). Значение счетчика 17 увеличивается на + или +2 в зависимости от значений 20

РДд,.., и РД,. 1-0 или 0-1.

Условия модификации адреса при ускоре.нном умножении запишутся в сле- 25 дующем виде:

(3)

(4)

Перечисленные преимущества предлагаемого устройства по сравнен1Ж) с известным позволяет эффективно использовать его для изучения больших интегральных схем.

Формула изобретения.

. Устройство для обучения микропрограммированию, содержащее микро-; процессор, первый, второй и третий входы которого соединены соответственно с выходами первого, второго и третьего коммутаторов, а первый, второй, третий и четвертый выходы - с первыми входами первого и второго блоков сравнения и первым и вторым входами блока регистрации соответст- венно, блок индикации, первый, вто- . рой, третий и четвертый входы которого подключены соответственно к первым выходам блока управления, первого регистра и счетчика и к выходу блока регистрации, блок памяти, первый, второй и третий входы которого

соединены соответственно с вторыми выходами первого регистра и счетчика и .выходом блока задания работы, блок синхронизации, элемент ИЛИ, элемент И, выход которого подключен к третьему входу блока регистрации, четвертый вход которого соеди ней с первым выходом четвертого коммутатора, отличающееся тем, что, с целью расширения дидактических возможностей устройства,

в него введены второй регистр и два распределителя импульсов, первые входы которТзтх соединены, с выходом элемента И, подключенным к вторым входам первого и второго блоков сравнения, третьи входы которых и вторые входы распределителей импульсов подключены к выходу второго регистра; соединенному с первым входом.первого коммутатора, второй и третий входы которого подключены соответственно- к вторым выходам четвертого коммутатора и блока управления, третий выход которого подключен к входу блока синхронизации, четвертый, пятый, шестой и седьмой выходы - к первым входам соответственно второго .коммутатора, третьего коммутатора, элемента И и счетчика, восьмой и девятый выходы - соответственно к первому и второму входам первого регистра,,а вход - к третьему выходу четвертого коммутатора, четвертый выход которого соединен с первым входо блока задания режимов работы и третьим входом блока памяти, первый вход с первым вь ходом блока синхронизации, а второй и третий входы - с первыми выходами соответственно первого и второго блоков сравнения,

вторые выходы которых подключены соответственно к первому и второму входам элемента ИЛИ, третий вход которого соединен с первым выходом первого распределителя импульсов:, а выход - с вторым входом счетчика, третий вход которого подключен к второму выходу первого распределителя импульсов, а четвертый вход - к выходу блока памяти, соединенному с четвертым входом второго регистра и вто рым входом третьего коммутатора, второй вход второго коммутатора п од- к.шочен к первому выхо.ду второго распределителя импульсов, второй выход которого соединен с вторым входом

0

5

0

5

0

5

0

5

0

5

блока задания режимов работы, второй вход элемента И соединен с вторым входом блока задания режимов работы, второй вход элемента И подключен к второму выходу блока синхронизации, третий вход первого распределителя импульсов соединен с вторым выходом микроп1эоцессора ,

2,Устройство по п.15 о т л и ч а- ю щ е е с я тем, что в нем первый распределитель импуль сов содержит последовательно включенные первый элемент И, второй элемент И, первый триггер, третий элемент И и первый элемент ИЛИ, выход которого является вторым выходом распределителя, последовательно соединенные второй триггер, четвертый элемент И и второй элемент ИЛИ, вькод которого является первым вьиодом распределителя, последовательно включенные инвертор и-пятый эл(;мент И, выход которого соединен с вторьп-4 входом второго элемента ШШ, и шестой элемент И, выход- которого соединен с вторым входом первого элемента ИЛИ, а первый, второй и третий входы - ;-оотнетственно с выходом первого элемента И, вторым выходом .первого триггер а и вторым выходом второго триггера, выход первого элемента И подк.пючен к первому входу второго триггера и к вторым входам третьег О, четвертого и пятого элементов И, первый выход первого триггера соединен с третьим входом пятого элемента И, вторым входом второго элемен7 а И и вторым входом второго триггера, второй выход первого триггера подключен к третьему входу четвертого элемента И, четвертый вход которого соединен с выходом инвертора, первый и второй входы первого элемента И являются соответственно первым и вторым входами распределителя, а вход инвертора, второй вход, второго триггера, третий вход третьего элемента И и четвертый вход шестого элемента И - третьим входом распределителя.

3.Устройство по п.1, о т л и ч а- К1 щ е е с я тем, что в нем второ.й распределитель импульсов содержит

последовательно включенные первый элемент И, элемент ИЛИ и.триггер, выход которого является вторым выходом распределителя, мультиплексор, вход и выход которого являются соответственно вторым входом и первым выходом распределителя, и второй элемент И, вькод которого соединен с вторым входом элемента ИЛИ, первые и вторые входы первого и второго элементов И являьгся соответственно первым и вторым входами распределителя.

4. Устройство по п, 1 , о т л и .4 а ю щ е е с я тем, что в нем блок управления содержит первый регистр, первый и второй выходы которого явля ются соответственно первым и четвертым выходами блока, второй регистр, выход которого является пятым выходом блока, первьш переключатель, пер

10

15

вый и второй выходы -которого соеди- . нены с первыми входами соответственно первого и второго регистра, третий регистр, выход которого является вторым выходом блока, второй, третий и четвертый переключатели, выходы ко- тррых являются третьим выходом блока и соединены с вторь1ми входами первого и второго регистров, пятый, шестой, седьмой и восьмой переключатели, выходы которых являются соответственно шестым, седьмым, восьмым и девятым выходами блока, и регистратор, вход которого и третьи входы первого и второго регистров являются входами блока,.

гъ

п

.J

J

и

и

L«

(а 7О

rtu

Сриг.З

€

D

((/./

вых.в ло/fu 8и9

Sb/x.SffflOK - 7

/У

//J

J

вУпохб 6Smf(/6м

eStiOKiS

Тр I rf

-В блок 17

Bff/iOffW

(игА

eStiOKiS

U

SiS/iOK

а

И Вт W

S /fotf 11 IT

е 7

J

W 50

ВЗлокИ

Sff/to/fff -

(.1

-

SffAOf StX

Фиг.З

Из ( 18 7

54 {

55

1

58

д$лок11

т 1

Из блока

го

8

56

сриг.б

ВНИИПИ Заказ 3709/51 Тираж 455Подписное

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

в блок 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1987 |

|

SU1456949A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Арифметическо-логическое устройство для обработки десятичных данных | 1984 |

|

SU1244660A1 |

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Арифметическое устройство по модулю | 1985 |

|

SU1285468A1 |

| МИКРОПРОЦЕССОР ВВОДА-ВЫВОДА ИНФОРМАЦИИ | 1992 |

|

RU2042182C1 |

| Вычислительное устройство | 1986 |

|

SU1327118A1 |

| Микро-ЭВМ | 1982 |

|

SU1124316A1 |

| Устройство для умножения | 1987 |

|

SU1495785A1 |

| Устройство управления микропроцессором | 1983 |

|

SU1156072A1 |

Изобретение относится к учебно- лАбораторному оборудованию. Целью изобретения является расширение дидактических возмойсностей с повышением надежности и достоверности вводимой информации за счет возможности выполнения операции ускоренного умножения введением операндов, над которыми производятся действия, непосредственно в состав микропрограмм. Составными частями предлагаемого устройства являются микропроцессор, блок синхронизации, блок памяти, блок управления, блок регистрации, блок индикации, два блока сравнения, распределители импульсов, блок задания режима работы, коммутатор сигналов синхронизации, коммутатор сигналов управления микропроцессора, кo iмyтa- тор данных, коммутатор микрокоманд, регистр числа,счетчик адреса, И,элемент ИЛИ, регистр микрокоманды, Введен ряд связей между состав- ньми частями устройства. Раскрыта структура формирователей импульсов ускоренного умножения, местного управления и непосредственного операнда. 3 з.п. ф-лы, 6 ил. с С 1C i4 СО

| Устройство для обработки газа | 1987 |

|

SU1574251A1 |

| Прибор для механического определения проекций линий данной длины и данного направления | 1923 |

|

SU656A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

| Патент США № 4225932, кл | |||

| Способ получения мыла | 1920 |

|

SU364A1 |

Авторы

Даты

1986-07-07—Публикация

1983-12-15—Подача