(54) УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ДВУХПРОЦЕССОРНОЙ СИСТЕМЫ ОБРАБОТКИ ДАННЫХ

генератора часов каждого процессора соединен со входом блока переключения- генераторов часов первого процессора и со входом блока переключения генераторов часов второго процессора выходы блока переключения конфигураций соединены со входами блока пере1ключения генераторов синхронизации каждого процессора и со входами блока переключения генераторов часов каждого процессора, выходы блока синхронизации генераторов соединены со входами блока переключения генераторов синхронизации каждого процессора и со входами блока переключения генераторов часов каждого процессора выход блока переключения генераторов синхронизации каждого процессора соединен со входом блока формирования синхросигналов ,данного процессора, выход блока формирования синхросигналов каждого процессора соединен со входом блока часов данного процессора и с данным процессором, выход блока переключения генераторов часов каждого процессора соединен со вторым входом блока часов данного процессора, выход блока часов каждого процессора соединен с данным процессором.

При необходимости отключения питания на процессоре, генератор синхронизации и генератор часов которого являются задающими генераторс1ми системы, блок переключения конфигураций вырабатывает сигнал, определяющий новую конфигурацию генераторов , Сигнал конфигурации поступает в блоки переключения генераторов синхронизации и генераторов часов каждого процессора, где при наличии разрешающего сигнала от блока синхронизации генераторов, новая конфигурация вызывает переключение генераторов 2 .

Недостатком этой многопроцессорной систегвл является большой объем оборудования, что обусловлено необходимостью наличия схемы синхронизации, определяющей момент переключения, а также использование блока переключения генераторов синхросигналов и блока переключения генераторов часов, выполняющих сходные функции.

Цель изобретения - сокращение объема оборудования многопроцессорной системы путем Ьоздания одйого универс€1льного блока для переключе- ния генераторов часов и синхросигналов без использования схемы синхронизации момента переключения.

, Поставленная цель достигается тем, что в устройстве, содержащем блок переключения конфигураций и два блока синхронизации, кгикдый из к6то1Ж1х включает генератор часов, узел переключения генераторов, сое диненный первым входом с выходом генератора синхросигналов, а первым выходом - со входом узла формирования синхросерий, выход которого соединен с первьш входом узла пересчета и первым выходом синхронизации c.ooтвeтcтвs oщeй группы выходов устройства, а йервый выход узла пересчета является вторым выходом синхронизации той же самой группы выходов устройства, причем второй вход узла. Iпереключения генераторов одного блока Синхронизации подключен к генератору синхросигналов другого блока синхронизации, а первый и второй выходы блока переключения конфигураций соединены соответственно с третьими взводами узлов переключения генераторов первого и второго блоков синхронизайии, вторые вход{ и выход узла пересчета каждого блока синхросигналов подключены соответственно ко второму выходу и четвертому входу узла переключения генераторов того же блока синхронизации, пятым входом соединенного с третьим выходом блока переключения конфигураций, шестым и седьиолм - соответственно со вторым входом узла формирования синхросерий и выходом генератора часов того же самого блока.синхронизации, а восьмым входом - с выходом генератора часов другого блока синхронизации.

Узел переключения генераторов содержит первый злемент И, входы которого соединены соответственно с пятым, шестым и четвертым входами узла, элемент-задержки, подключенный вхо- . дом к пятому входу узла, а выходом к входам триггера подключения своего процессора, триггера подключения другого процессора и триггера ввода конфигураций и через элемент НЕ к первсвлу входу второго элемента И, вторым входом и выходом соединенного соответственно с выходом первого элемента И и вторым входом триггера ввода конфигурации, выход которого подключен к первым входам третьего-шестого элементов И, вторые входы которых соединены соответственно с первым, вторым, седьмым и восьмым входами узла, первый и второй элементы ИЛИ, В1лхрды которых являются соответственно первьм и вторым выходс1ми узла, а первые и второе входысоединены Соответственно с выходами третьего-шестого элементов И, и элe. гнтоа И-НБ, входом соединенный с третьим входом узла,.инверсным входом - со вторим входом триггера подключения своего процессора, выход KOTopoio подключен к третьим входам третьего и пятого элементов И, а . прямым выходом - со втором вводом триггера подключения, другого процессора, выход которого подключен к третьшл входам четвертого и шестого эледлентов И.

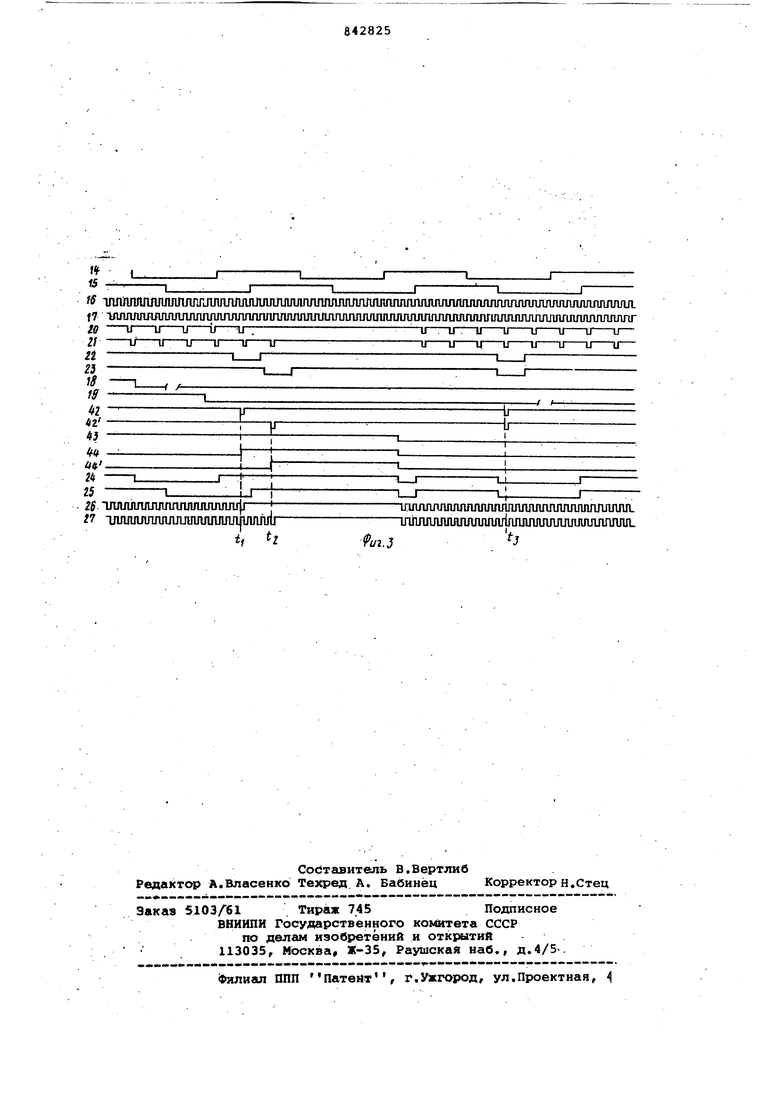

На фиг.1 приведено устройство, 5 блок-схема; на фиг.2 - функциональная схема узла переключения генераторов; на фиг.З - временная диагрс1м работы блока переключения генератор Устройство содержит (фиг.1) блоки 1 и 2 синхронизации первого и второго процессора, блок 3 управления конфигурацией, генератс ы 4 и 5 синхросигналрв блоков 1 и 2, генераторц 6 и 7 часов блоков.1 и 2, узлы 8 и 9 переключения генераторов блоков 1 и 2, узлы 10 и 11 формиррвания синхросерий блоков 1 и 2, узлы 12 и 13 пересчета блоков 1 и 2, выходные шины 14 и 15 генераторов 4 и 5 синхросигналов, выходные шины 16 17 генераторов б и 7 часов, выходная шина 18 сигнала конфигурации и первый выход блока 3, выходная шина 19 сигнала установки конфигурации и третий выход блока 3, выходные и 21 сигналов конца такта сннхронизсщии процессов ( шлходы) узлов 10 и 11, выходные шны 22 к 23 сигнала конца пересчета часов процессоров (первые выхода) узлов 12 и 13,. выходные шины 24 и 25сигналов синхрониза1 ии {первые выходы) узлов 8 н 9, выходные ши|1Ы 26и 27 сигналов пересчета часоа (втсфые выходы) узлов 8 и 9. Узлы и 9 подключения генераторов содержат (фиг,2) элетвент 2S задержки, первый элемент И 29, элемент НЕ 30V второй элемент И 31, элемент 32, триггер 33 ввода конфигурации, триггер 34 подключения генераторов своего процессора, триггер 35 подключения генераторов другого процессора, третий-гиестой элементы И 36-39, элементы ИЛИ 40 и 41, шина 4:2 сигнала разрешения ввода конфигурации, шина 43 задержанного сигнала установки конфигурации, шина 44 сигнала блокировки генераторов 44. . Сигналы 42, 44,.показанные на фиг.З, представляют собой сигналы блока переключения генераторов вто рого процессора. Указанные сигналы соответствуют сигналам 42., 44, приведен.ным на фиг.2Блок 3 может представлятьсОбой, например, кнопочный переключатель для формирования сигнала установки конфигурации и 3-х позиционньМ пврй Прсядессор ключатель с положениями 1, Процессор 2, Местное Генераторы 4, 5 синхросигналов и генераторы 6, 7 часов представляю собой стандартные кварцевые генерат . .;. - Узлы 10 и 11 представляют собой стандартные узлы с типовыми функхшо нальными возможностями, в которых из последовательностей, рыдаюкцах сигналы на шинах 24, 25, вырабатывается несколько серий, синхроимпуль сов, сдвинутых между собой на равны части такта. Сигналы окончания такта синхронизации, выдаваемые на шины 20, 21, являются последними сериями такта. Узлы 12, 13 представляют собой счетчики, пересчитывающие содержимое регистра часов длиной в 51 разряд, по частям в .течение нескольких тактов. Устройство работает следующим образом. Сигналы с блока 3 поступают на узлы 8, 9, позволяют производить переключение пар-генераторов 4, 6 и 5, 7. Выбор необходимой пары генераторов ос тцествлдется с помощью сигнала на шине 18, а момент их подключения определяется сигналом на шине 19. Переключение генераторов синхросигн1алов должно производиться после окончания машинного такта, так как в противном-случае,Возможны нарушения вычислительного процесса в системе из-за потери части машинного такта. Узшл 10, 11 выдают сигналы конца такта синхронизации на шинах 20, 21, причем в обоих узлах эти . сигна-пы не совпадают по времени. Узлы 12, 13 также вырабатывают сигНалы конца пересчета на шинах 22, 23, не совпадающие по времени (Фиг.З). Эти сигналы совместно с сигналом на шин 19 поступают в узел В на входы элемента 29, на выходе 42 которого иойвляется сигнал, Ангшогично в узле 9 формируется сигнал на выходе 42 . Максимальный временной сдвиг, между сигналами на выходах 42, 42 равен периоду пересчета часов. Сигнал на выходе 42 и единичный .уровень с элемента НЕ 30 образуют конъюнкцию на элементе И 31, которая поступает на вход триггера :33.Триггер устанавливается в нуль, запирая элементы И 36-39, в результате чего импульсы генераторов не проходят на выходы узлов 8, 9 и не поступают в устройства первого процессора (Пр.1). Аналогично во втором процессоре (Пр. 2) .происходит блокировка импульсов, выдаваемых в узлы 10-13. Таким образом, блокировка в обоих процессорах происходит в разные моменты времени, определяемые сигналами на Выходах элементов И 29 узЛов 8 и 9 {на Фиг.З это времет на t к tg,). Инициация работы системы от выбранной пары генераторов происходит ОДноврамейно в обоих процессорах, что приводит к их дальнейшей синхронной работе. Сигнал на шине 19, задержанный на время, большее такта часов с помощью элемента 28 задержки, поступает одновременно на входы t №cr&pa 33 и на входы синхронизации триггеров 34, 35 Обоих процессоров« Одновр««енность прихода этих сигналов также регулируется с помощью , элемента. 28 задержки. Переброс в единичное состояние триггера 3J совпадает G приемом новой конфигурации на триггере 34, 35, выходные сигналы которых, поступая на элетленты И 3639, разрешают прохождение сигнёшов той или другой пары генераторов через элементы или 40, 41 на выходные шины 24, 26.. Для предотвращения наличия запрещенной комбинации на входах тригг.ера 33 в момент времени t) предусматривается блокировка R-входа от сигнала на выходе 43 через элементы НЕ 30 и И 31. Таким образом, устройство обеспечивает сокращение объема оборудовани з.а счет использования универсального блока переключения генераторов без применения дополнительной схемы синхронизации Для определения момента переключения. Наряду с этим испольЭование данного ус ройства позволяет сохранить непрерывность вычислительного процесса в системе в момент переключения генераторов, не требуя перегрузки системы, что является его дополнительным преимуществом по срав нению с известным устройством. Формула изобретения . Устройство для синхронизации двух процессорной системы обработки данных, содержащее блок переключения конфигураций и два блока синхронизации, каждый из которых включает генератор часов, узел переключения генераторов, соединенный первым входом с выходом генератора синхросигналов, а первым выходрм - со входом узла формирования синхросерий, выход которого соединен с первым входом узла пересчета и первым выходом синхронизации соответствующей группы выходов устройства, а первый выход узла пересчета является вторым выходом синхронизации той же самой группы выходов устройства, причем .второй вход узла переключения генераторов одного блока синхронизации подключен к генератору синхросигналов да угого блока синхронизации а первый и второй вьоходы блока переключения конфигураций соединены соответственно с третьими входами узлов переключения генераторов перBOi-o и второго блоков синхронизации от л и ч а ю щ е е с я тем, что, с целью сокращения объема оборудования, вторые вход и выход узла пересчета каждого блока синхросигналов подключены соответственно ко второму выходу и четвертому входу узла переключения генераторов того же блока синхронизации, пятым входом соединенного с третьим выходом блока переключения конфигураций, шестым и седьмым - соответственно со вторым . выходом узла формирования синхросерий и выходом генератора часов того Же самого блока синхронизации, а восьмым входом - с выходом генератора часов другого блока синхронизации. . 2. Устройство по П.1, о т л и чающееся тем, что узел,переключения генераторов содержит первый эл1емент И, входы которого соединены, соответственно с пятым, шестым и четвертым входами узла, злемент задержки, подключенный входом к пятому входу узла, а выходом - к первым входам триггера подключения своего процессора, триггера подключения другого процессора и триггера ввода конфигураций и через элемент НЕ к первому входу второго элемента И, вторым входом и выходом соединенного соответственно с выходом первого элемента И и вторым входом триггера ввода конфигурации, выход которого подключен к первым входам, третьего-шестого элементов И, вторые входы которых соединены соответственно с первым, вторам, седьмым и восьмым входами узла, первый и второй элементы ИЛИ,выходы которых являются соответственно первым и вторым выходами узла, а первые и вторые входы соединены соответственно, с входами третьего-шестого элементов И, и элемент И-НЕ, входом соединенный с третьим входом узла, инверсным выходом - со вторым входом триггера подключения своего процессора , выход которого подключен к третьим входам третьего и пятого элементов И, а прямым выходом - со вторым входом триггера подключения другого процессора, выход которого подключен к третьим входам четвертого и шестого элементов И. Источники информации, ринятые во внимание при экспертизе , 1.Патент ПНР 81689, л. G 06 F 15/16, опублик.1976. 2.Патент США 4021784, л. 340-172,5, опублик.1977 (протоип) ,

VtoISo160n o-Ss

«}UJ

tf

I

Б

J(

ft

2J

2

ff

TJ

;ftp

Й

№

К

.I1I1I

«--.1I -T J

ff ТЛПШ1ШШЛЛПШ1ГЛШШШЛПЛШ1Ш1ПЛЛЛПППППЛШШ1Ш11ПШШШ

f 7 innnflminmiminnnnnnflnnnnnnnnnnnfljmnjuimimmnflnnnnnnnnmmnrmnf

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля двухпроцессорной системы | 1982 |

|

SU1013962A1 |

| Запоминающее устройство | 1976 |

|

SU613402A1 |

| Устройство для диагностики каналов ввода-вывода | 1977 |

|

SU669921A1 |

| Процессор с микропрограммным управлением | 1983 |

|

SU1149273A1 |

| Устройство для синхронизации вычислительной системы | 1978 |

|

SU752314A1 |

| Устройство для синхронизации вычислительной системы | 1983 |

|

SU1129597A1 |

| Устройство для синхронизации вычислительной системы | 1980 |

|

SU974364A1 |

| Генератор испытательных кодов | 1986 |

|

SU1405058A1 |

| Устройство для сопряжения модулей процессора | 1982 |

|

SU1056176A2 |

| Устройство для ввода информации | 1983 |

|

SU1087976A1 |

i, .

Авторы

Даты

1981-06-30—Публикация

1979-09-19—Подача