(54) УСТРС ЮТВС ДЛЯ ЭЛЕКТРОСТАТИЧЕСКОЙ ЗАПИСИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1988 |

|

SU1644225A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1988 |

|

SU1606996A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели | 1989 |

|

SU1675935A1 |

| Устройство для отображения информации на газоразрядной индикаторной панели | 1990 |

|

SU1781698A1 |

| Устройство для дистанционного управления топливораздаточными колонками | 1982 |

|

SU1067472A1 |

| ЦИФРОВОЙ ФИЛЬТР | 1991 |

|

RU2029362C1 |

| Устройство для обмена информацией | 1987 |

|

SU1497619A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1992 |

|

RU2045781C1 |

| Устройство для цифровой фильтрации | 1984 |

|

SU1264306A1 |

| Многоканальное устройство ввода информации | 1985 |

|

SU1273936A2 |

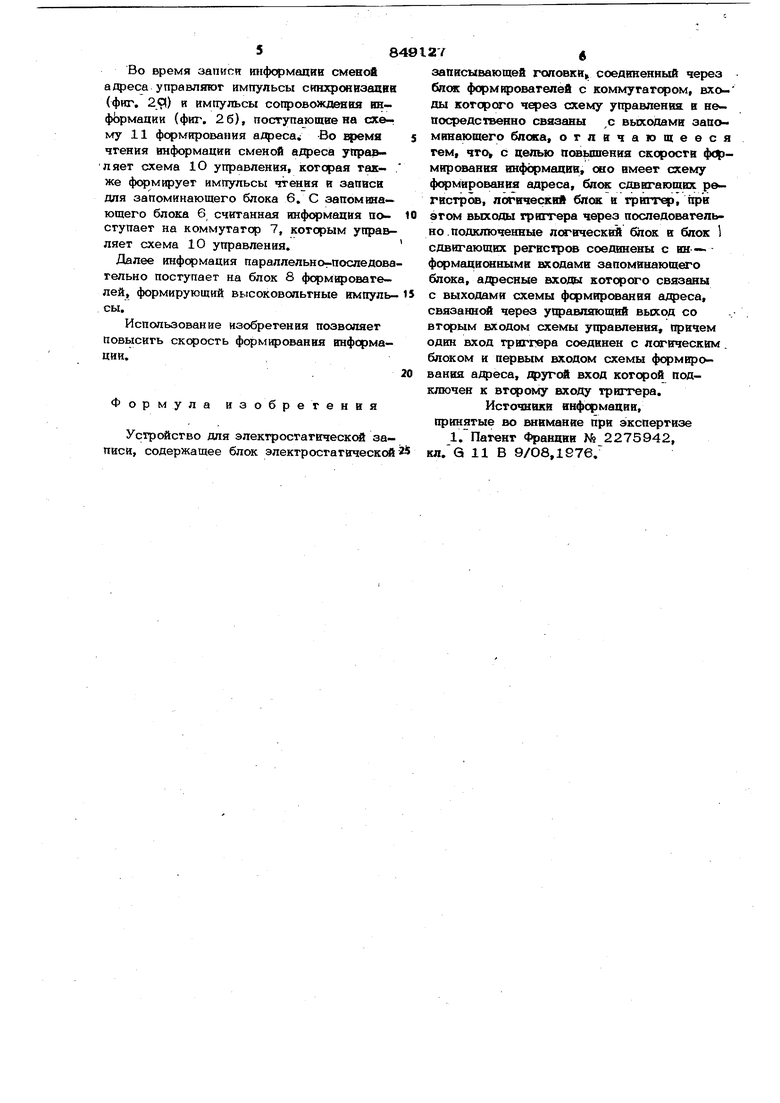

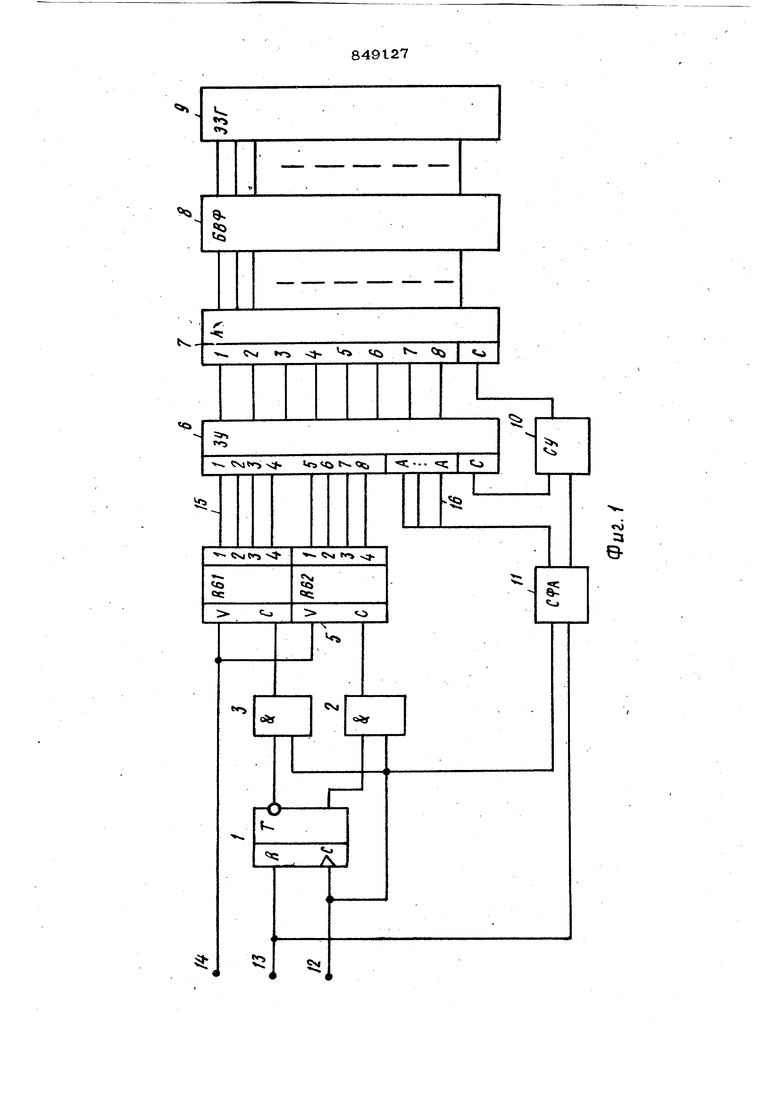

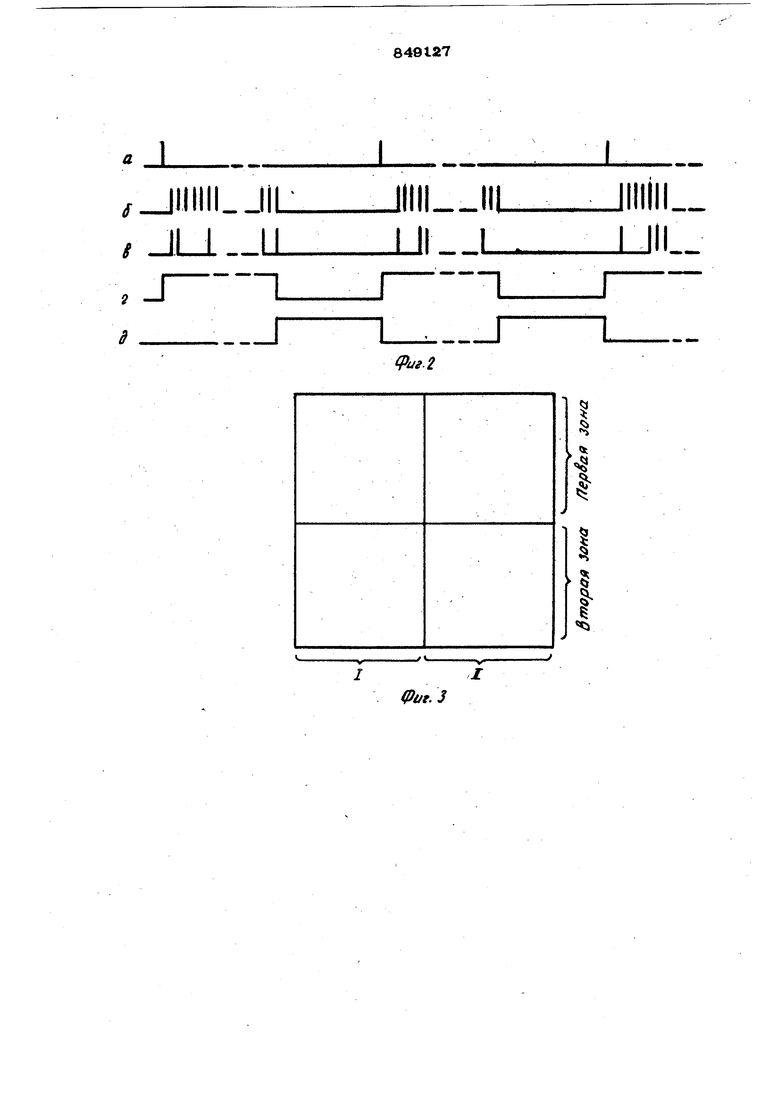

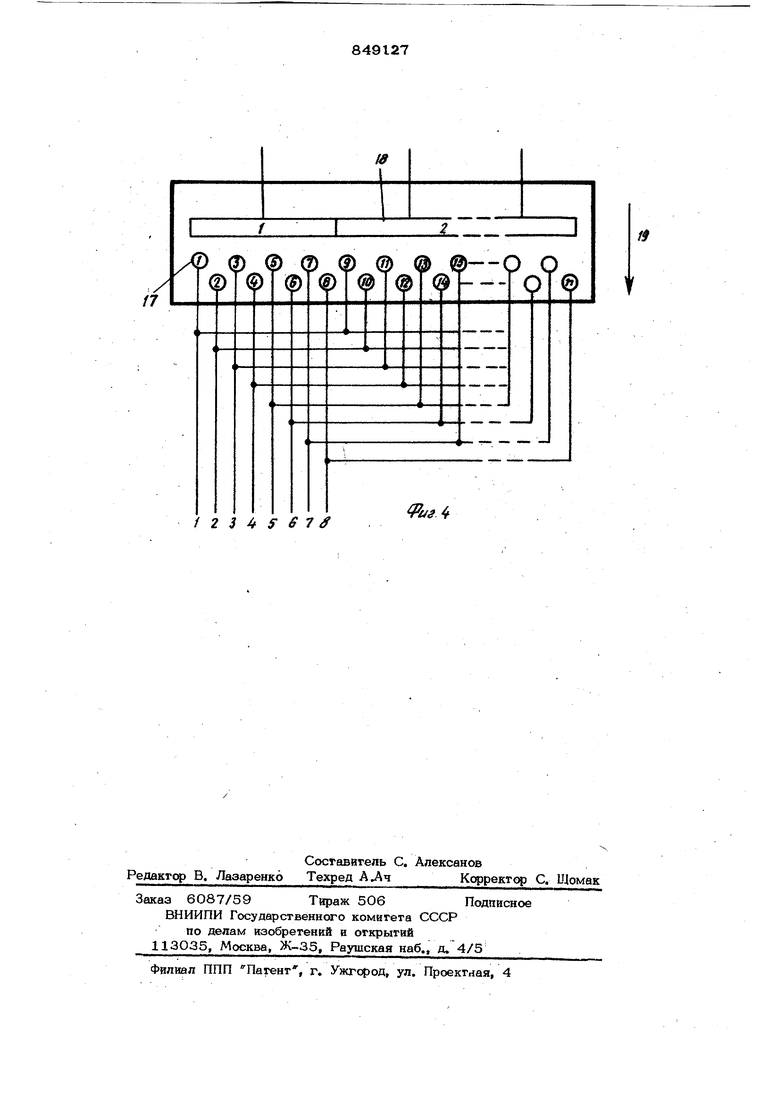

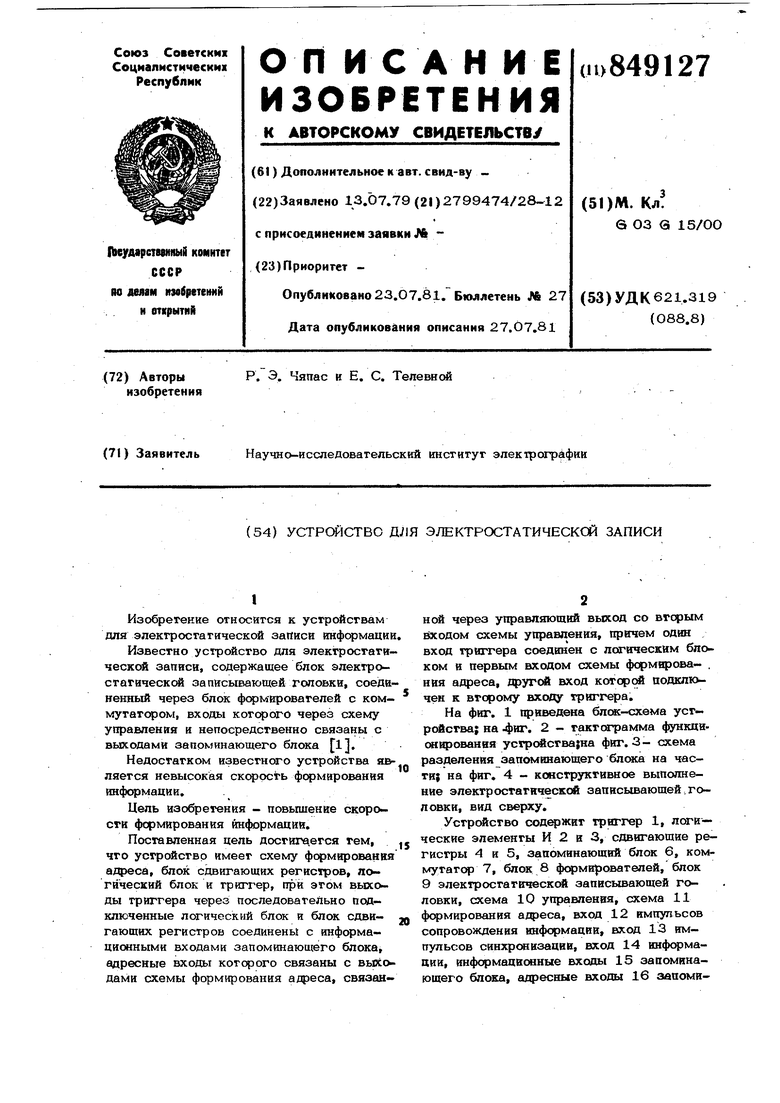

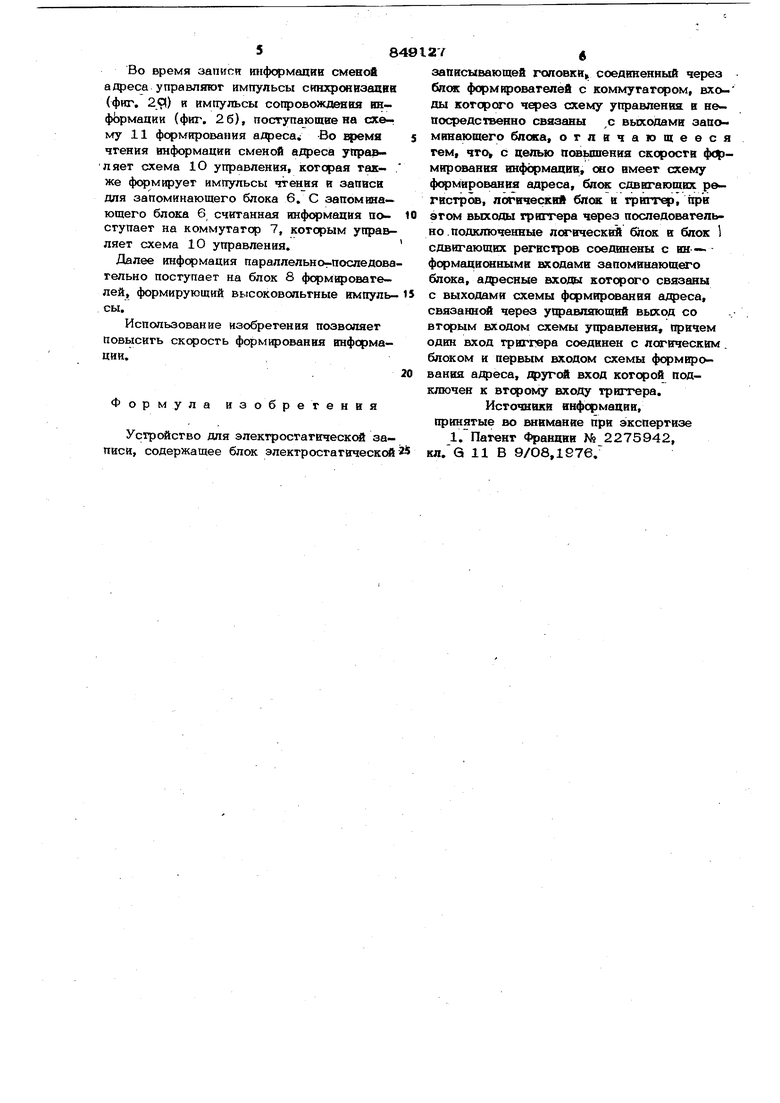

Изобретение отнсх игся к усгройсгвам для электросгагнческой записи информации Известно устройсгво для электростатической записи, содержащее блок электростатической записывающей головки, соеди ненный через блок формирователей с коммутатором, входы которого через схему управления и непосредственно связаны с выходами запоминающего блока 1. Недостатком известного устройства яв ляется невысокая скорость формирования инфсфмадии:. Цель изобретения - повьпиение скорости формирования информации. Поставленная цель достига.ется тем, что устройство имеет схему формирования адреса, блок сдвигающих регистров, логнческий блок и триггер, при этом выходы триггера через последовательно подключенные логический блок и блок сдвигающих регистров соединены с информационными входами запоминающего блока, адресные входы которого связаны с выхо дами схемы формирования адреса, связанной через управляющий выход со вторым входом схемы управления, причем один вход триггера соединен с лсхгическим блоком и первым входом схемы фсрмирова- . ния адреса, другой вход которой подключен к второму входу триггера. На фиг. 1 приведена блсж-схема устройства; на . 2 - гактсят)амма функциси«фования усгрсйства;на фиг. 3- схема разделения запоминающего блсяш на части; на фиг. 4 - конструктивное выполнение электростатической записывающей.головки, вид сверху. УстрсАство содержит триггер 1, логические элементы И 2 и 3, сдвигающие регистры 4 и 5, запоминающий блок 6, коммутатор 7, блок 8 фсчэми ователей, блок 9 электростатической записывающей головки, схема 10 управления, схема 11 формирования адреса, вход 12 импульсов сопровождения информации, вход 13 импульсов синхронизации, вход 14 информации, информационные входы 15 запоминающего блока, адресные входы 16 запоминающего блока, а также электроды 17 заавси и секдия 18 конгрэлекгродов. Стрелка 19 показывает натфавп ние движения носителя записи. Логический блок имеет логические элеменгы И 2 и 3. Блок сдвигающих регистров состоит из сдвигающих регистров 4 и 5. Регистры 4 и 5 представляют собой однотактовые сдвигающие регистры с последовательным сдвигом, они последовательно записывают код. Поступающий на V -входы регистров, при поступлении се: рии тактирующих импульсов на С - входы регистров 4 и 5. Регистры 4 и 5 в устройстве вьтолняют функцию преобразования последовательной информации, поступающей на вход 14 устройства, в параллельно-последовательную информацшо,поступающую далее на входы запоминающего блока 6, Каждая строка электростатической записывающей головквг имеет одинаковое количество информационных битов, которое равно hi . Для обеспечения растровой записи информации строки количество электродов записи тоже равно Ш . В данном устройстве m - число, кратное восьми, так как информация записывается на носи тел параллельно группами по восемь точек. На электростатическую записывающу головку одновременно подается информаци нечетных битов h -ой строки на нечетны электроды записи и информация битов (И-1)-ой строки на четные электроды записи. Устройство работает следующим образогл, На вход 13 поступают импульсы синхрсжизации, определжпощие начало поступления информации (фиг. 2а). На вход 12 поступают импульсы сопровождения инфор мации (фиг.25). Ка вход 14 поступает информация в виде построчно разложенног кода (фиг.2-в), совпадающая по фазе с им пульсами сопровождения информации (фиг. 2$). На фиг. 22 и фиг. 2д показа но распределение времени работы устройства. После поступления импульса синхронизации начинается последовательно - параллельная запись информации в запоми нающий блок 6 (фиг.2г). По окончании записи осуществляется чтение информаци из запоминающего блока 6 (фиг. 2д) и вывод ее на носитель. Триггер 1 и логические элементы И 2 и 3 схем осуществляют разделение импульсов сопровождения гафЬрмации на четные и на нечетные. Нечетные импульсы поступают на сдвиговый вход первого сдвигающего регистра 4,прй этом в него записывается информация нечетных точек изображения. Информация четных точек изображения записьшается во второй сдвигающий регистр 5. При выводе инфорлгации на бумагу точечно-растровым построчным методом с помощью многоэлектродной двухрядной записывающей головки щахматного типа на нечетные электроды записи (первый ряд) подается информация нечетных битов (точек) И -ой строки, на четные электроды записи (второй pяд подается инфqзмaция четньк битов ( И-1)-ой строки. Для обеспечения одновременной подачи информации на четные и нечетные электроды блока 9, запоминающий блок 6 имеет объем информации двух растровых строк, равной 2 Щ бит, где m - количество электродов записи в блоке 9 электростатической записывающей головки. Запоминающий блок 6 разделен на две равные части 1 и И (фиг. 3) с раздельными входами, выходами и адресными входами. В часть 1 записывается информация только нечетных битов строки из регистра 4, в часть 11 записьшается информация только четных битов строки из регистра 5. При этом каждая часть запоминающего блока разделена на две зсньи В первую зону записывается информация и -ой строки, во вторую зону записывается информация (и -1)-ай строки. Последовательность работы запоминающего устройства будет следующая: ЗПГ- ЧТ1 2 - ЗП2 - .ЧТ2 1 ЗП1-ЧТ1.2 и т.д., где гфиняты следующие обозначения: ЗП1 - запись информации строки в первую ЗОНУ ЧТ1 2 одновременное чтение информации с первой зоны нечетных бит и со второй зоны четных бит; ЗП1 запись информации строки во вторую зону; ЧТ2 одновременное чтение информации со второй зоны четных бит и с первой зоны нечетных бит, При записи инфсркации строки адрес на 1 и Г1 части запоминающего блока 6 формируется одинаковой. При чтении информации адреса на 1 и TI части запоминающего блока формируются разные в соотсетствик с вышеописанной последовательностью. Во время записи информацяв сменой адреса управляют импульсы синхронизацвв (фиг. 29) и импульсы сопровождения инфЬрмадии (фиг. 26), поступающие на c3te-t му 11 формирования адреса Во время чтения информации сменой йрресд управляет схема 1О управления, которая также формирует импульсы чтения и записи для запоминающего блока б. С запоминающего блока б считанная инфсфмация поступает на коммутатор 7, которым упра ляет схема 10 управления. Далее информация параллельног-последова тельно поступает на блок 8 формирователей, формирующий высоковольтные импульсы. Использование изобретения позволяет повьюить скорость формирования Ешфс|)маЦНИ. Формула изобретения Устройство для электростатическсий записи, содержащее блок электростатическсй 8 27в записывающей головки,, соединенный через блок формирователей с коммутатором, axcvды которого через схему управления и непосредственно связаны с выходами запоминающего блока, отличающееся тем, ЯГО, с целью пов лпения скорости формирования анформацви, оно имеет схему формирования адреса, сдвигающих регистров, лсг-вческнй блок и триггер, 1фи этом выходы триггера через последовательно, подключенные логический блок и блок 1 сдвигающих регистров соединены с информационными входами запоминающего блока, адресные входы которого связаны с выходами схемы формирования адреса, связанной через управляющий выход со вторым входом схемы управления, причем один вход триггера соединен с логическим, блоком и первым входом схемы формированва адреса, другой вход которой подключен к второму входу триггера. Источнвкп информации, принятые во внимание при экспертизе 1. Патент Франции № 2275942, кл.в 11 В 9/08,1976.

i;

N4 « . C Ча I

4i

. «

g 4b I

if

Csit

«SI Гг «N4

«5

«

«O

Cj

CM

r

c

- . X

I gp

г 1

k

«

:э

e

U

Фиг.З

17

f 2 3 4 у S 7 f

J,

f9

о о о

Авторы

Даты

1981-07-23—Публикация

1979-07-13—Подача