1

(21)4457328/24

(22) 08.07.88

(46) 23.04.91 .Бюл. №15

(71)Рязанский радиотехнический институт

(72)В.Л.Волковыский и Ю.М.Субботкин (53)681.327.6(088.8)

(56) Майоров С.А., Новиков Г.И. Принципы организации цифровых машин. - Л.: Машиностроение, 1974, с. 380-381.

Дроздов Е.А., Комарниц ий В.А., Пятиб- ратов А.П. Электронные вычислительные машины единой системы. - М.: Машиностроение, 1981, с.190-193, рис. 5.6. (54)ОПЕРАТИВНОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО

(57) Изобретение относится к вычислительной технике и может быть использовано в быстродействующих вычислительных системах. Цель изобретения - повышение быстродействия устройства. Оперативное запоминающее устройство содержит первый 1 и второй 2 блоки памяти, коммутатор 3 входных и коммутатор 4 выходных данных, первый 5 и второй 6 регистры адреса, коммутатор 7 адресов, блок 8 управления, адресные входы 9 и 10, входы 11 и 12 блока управления, входы задания режима 13-17, информационые входы 20 и 21 и информационные выходы 22 и 23. 1 э.п.ф-лы, 2 ил., 2 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор для мультипроцессорной системы | 1985 |

|

SU1295410A1 |

| Процессор для мультипроцессорной системы | 1987 |

|

SU1517035A1 |

| Процессор с микропрограммным управлением | 1990 |

|

SU1700564A1 |

| Микропрограммный процессор | 1986 |

|

SU1462339A1 |

| Устройство для отладки программно-аппаратных блоков | 1983 |

|

SU1242965A1 |

| Устройство для формирования видеосигнала | 1990 |

|

SU1741124A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

| Устройство для управления оперативной памятью | 1985 |

|

SU1291992A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Устройство управления доступом к памяти для обмена массивами данных в многопроцессорной системе | 1989 |

|

SU1633418A1 |

сл

с

сь

fc

ю го сл

Фиг.1

Изобретение относится к вычислительной технике и может быть использовано в быстродействующих вычислительных системах.

Цель изобретения -повышение быстро- действия устройства.

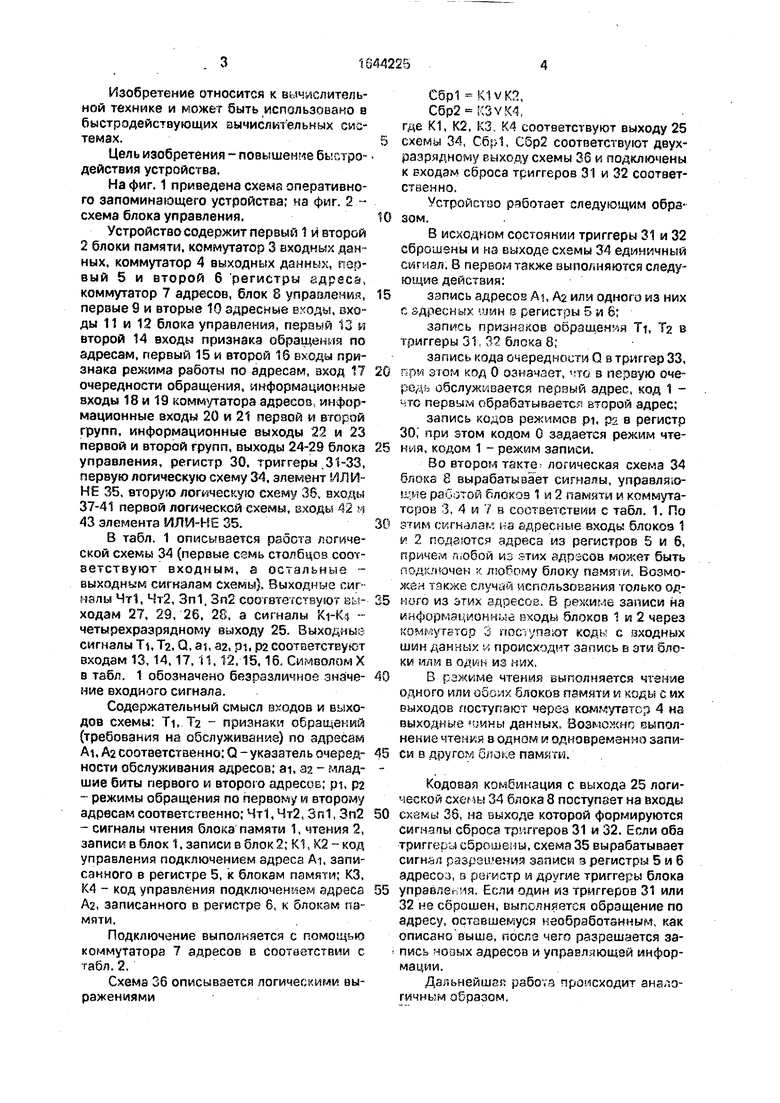

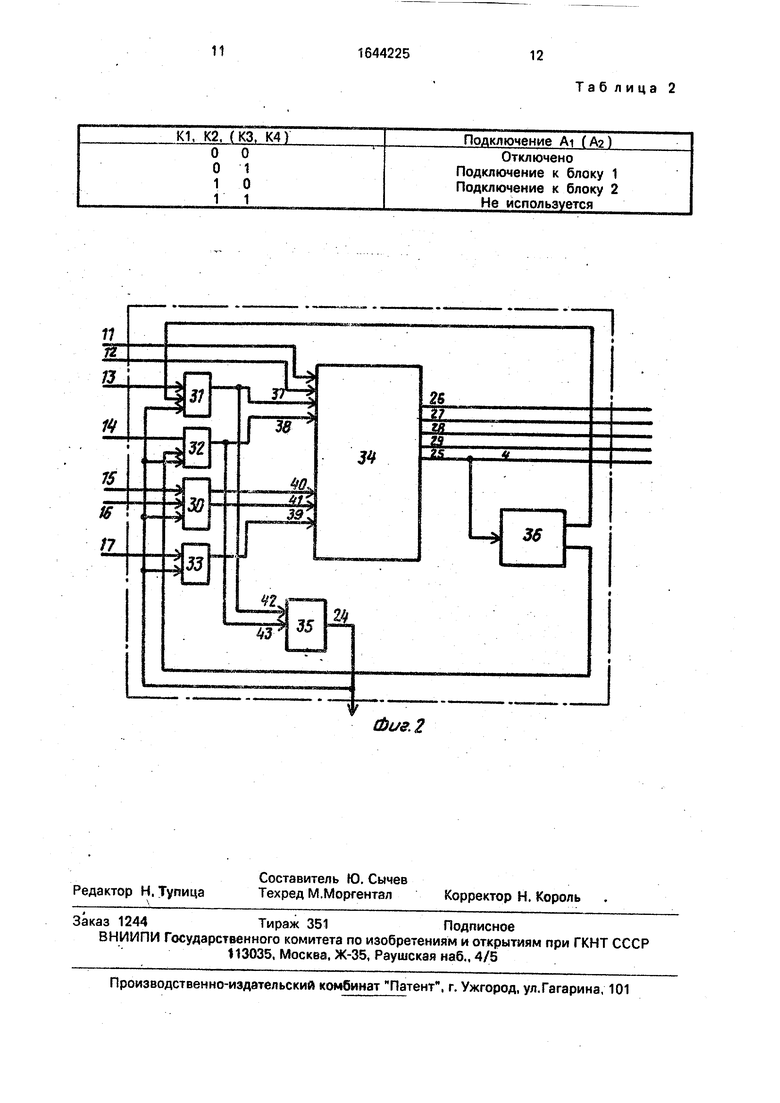

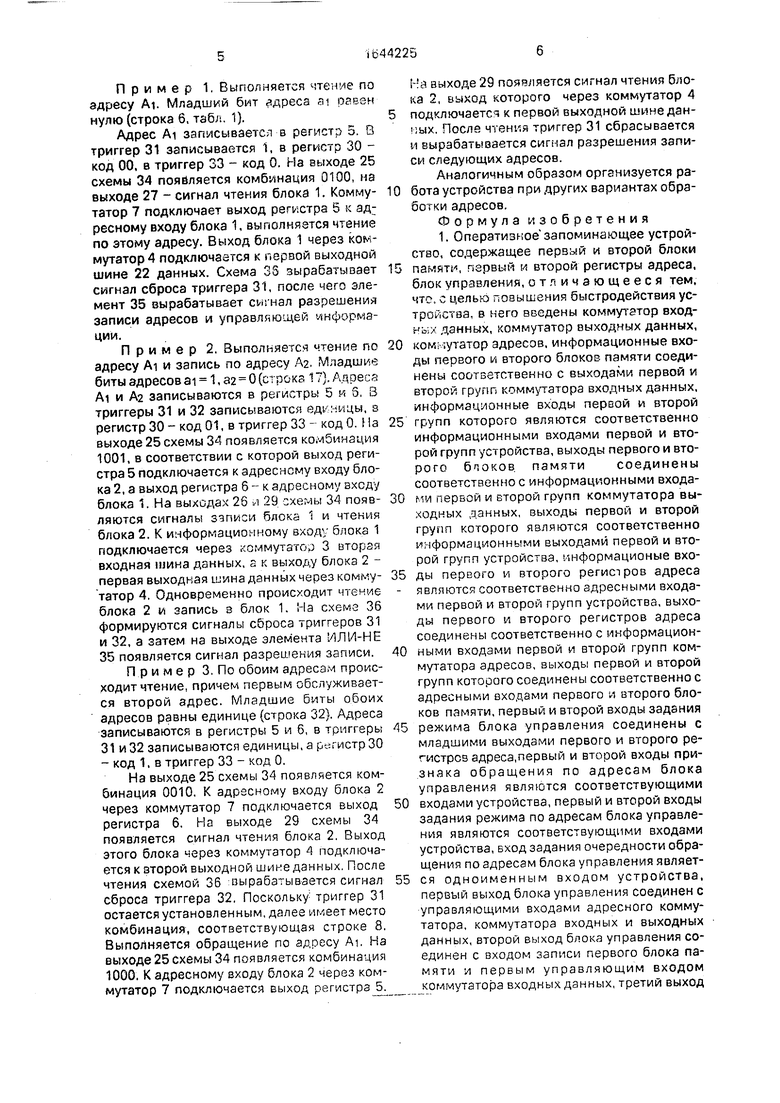

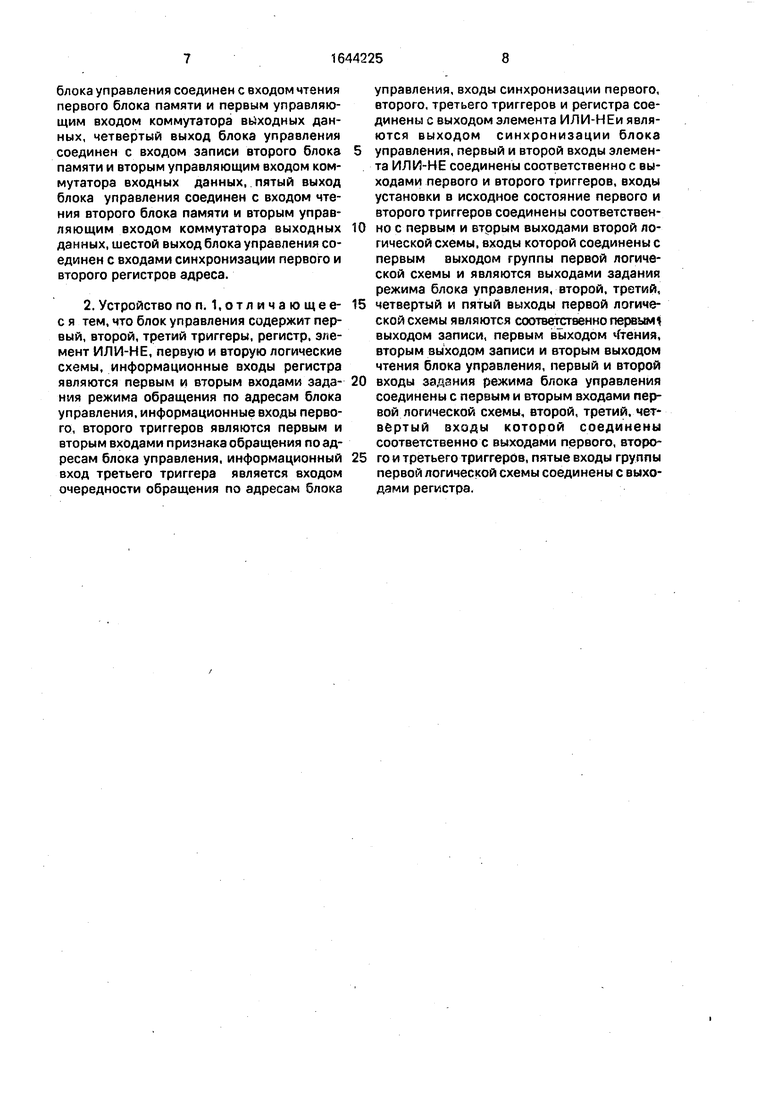

На фиг. 1 приведена схема оперативного запоминающего устройства; на фиг. 2 - схема блока управления.

Устройство содержит первый t и второй 2 блоки памяти, коммутатор 3 входных данных, коммутатор 4 выходных данных, первый 5 и второй 6 регистры адреса, коммутатор 7 адресов, блок 8 управления, первые 9 и вторые 10 адресные входы, входы 11 и 12 блока управления, первый 13 к второй 14 входы признака обращения по адресам, первый 15 и второй 16 входы признака режима работы по адресам, вход 17 очередности обращения, информационные входы 18 и 19 коммутатора адресов, информационные входы 20 и 21 первой и второй групп, информационные выходы 22 и 23 первой и второй групп, выходы 24-29 блока управления, регистр 30, триггеры .31-33, первую логическую схему 34, элемент МЛН- НЕ 35, вторую логическую схему 36V входы 37-41 первой логической схемы, входы 42 ч 43 элемента ИЛИ-НЕ 35.

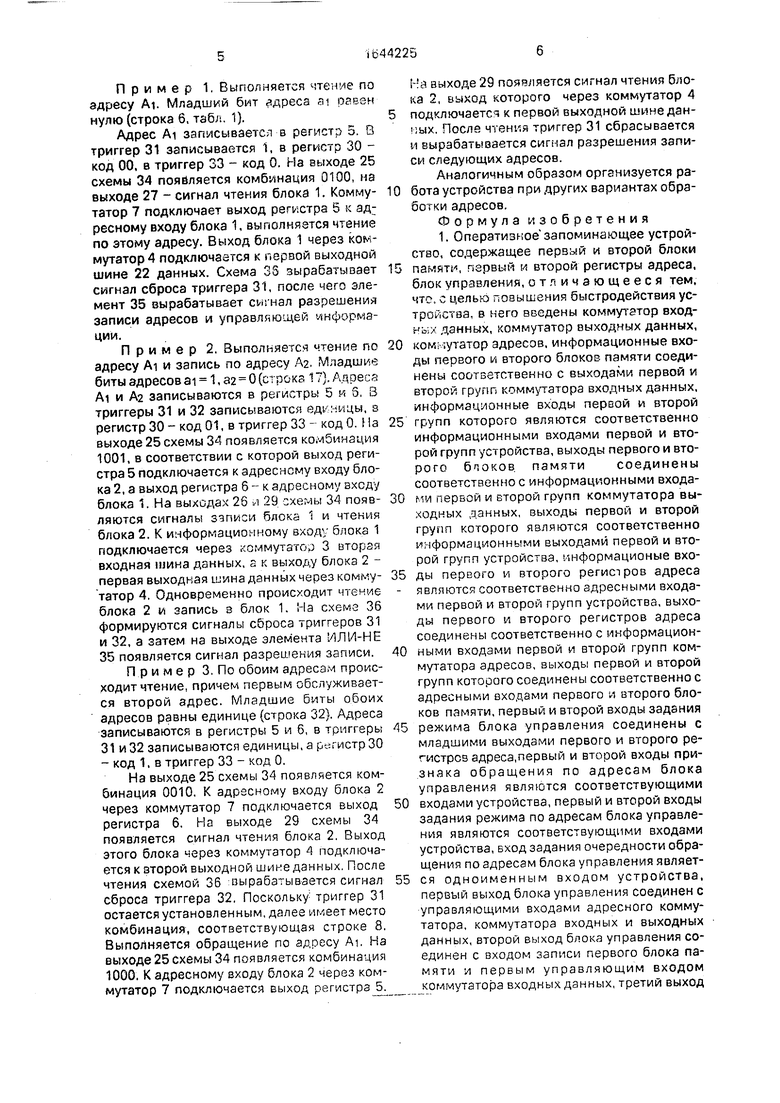

В табл. 1 описывается работа логической схемы 34 (первые семь столбцов соответствуют входным, а остальные - выходным сигналам схемы). Выходные сигналы Чт1, Чт2, Зп1. Зп2 соотвтетствуют БУ- ходам 27, 29, 26, 2В, а сигналы КН(4 - четырехразрядному выходу 25. Выходные сигналы Ti, Та, Q, ai, 32, pi, 02 соответствуют входам 13,14.17,11,12,15.16, Символом X в табл. 1 обозначено безразличное эначе- ние входного сигнала.

Содержательный смысл входов и выходов схемы: Ti, Jz - признаки обращений (требования на обслуживание) по адресам At, A2 соответственно: Q - указатель очеред- ности обслуживания адресов; ai, аг - млад- шие биты первого и второго адресов; pi, pa

-режимы обращения по первом/ м второму адресам соответственно; Чт1, Чт2, Зп1, Зп2

-сигналы чтения блока памяти 1, чтения 2, записи в блок 1, записи в блок 2; К1, К2 - код управления подключением адреса Ai. записанного в регистре 5, к блокам памяти; КЗ,

К4 - код управления подключением адреса А2, записанного в регистре 6, к блокам памяти.

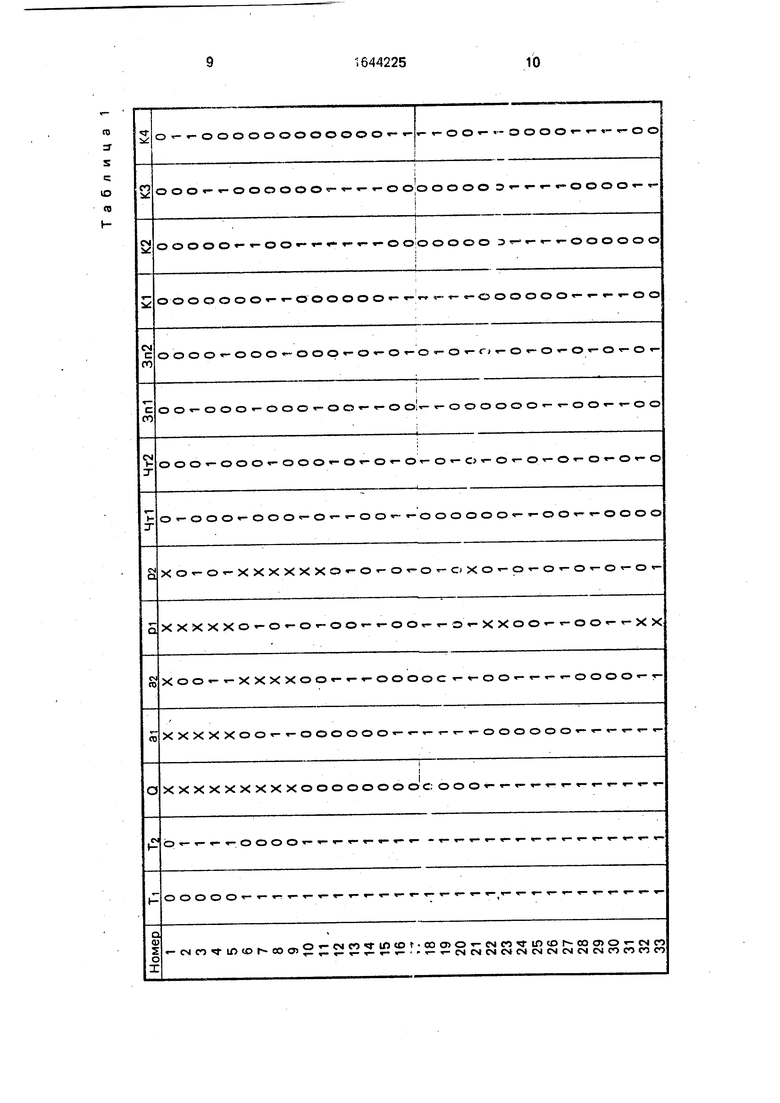

Подключение выполняется с помощью коммутатора 7 адресов в соответствии с табл. 2.

Схема 36 описывается логическими выражениями

Сбр1 -K1VK2, C6p2 K3VK4, где К1, К2, КЗ, К4 соответствуют выходу 25

схемы 34, Сбр1, Сбр2 соответствуют двухразрядному выходу схемы 36 и подключены к входам сброса триггеров 31 и 32 соответственно.

Устройство работает следующим образом.

В исходном состоянии триггеры 31 и 32 сброшены и на выходе схемы 34 единичный сигнал. В первом также выполняются следующие действия:

запись адресов Ai, А2 или одного из них с адресных шин в регистры 5 и 6;

запись признаков обращения Tt, Т2 в триггеры 31-32 блока 8;

запись кода очередности Q в триггер 33, npw этом код 0 означает, что з первую очередь обслуживается первый адрес, код 1 - что первым обрабатывается второй адрес;

запись кодов режимов pi, pa в регистр 30, при зтом кодом 0 задается режим чтения, кодом 1 - режим записи.

Во втором такте логическая схема 34 блока 8 вырабатывает сигналы, управляющие работой блоков 1 и 2 памяти и коммутаторов 3, 4 и 7 в соответствии с табл. 1. По этим сигналам из адресные входы блокоз 1 и 2 подаются адреса из регистров 5 и 6, причем любой из этих адрзсов может быть подключен . любому блоку памяти. Возможен также случай использования только одного из згих адресов. В режиме записи на информационные входы блоков 1 и 2 через коммутатор 3 поступают коды с входных шин данных v, происходит запись в эти блоки ИЛИ Б ОДИН ИЗ НИХ.

В рзжиме чтения выполняется чтение одного или обоих блоков памяти л коды с их выходов поступают через кош-яутатор 4 на выходные иины данных. Возможно выполнение чтения в одном и одновременно записи в другом блоке памяти.

Кодовая комбинация с выхода 25 логической схег ш 34 блока 8 поступает на входы схемы 36, на выходе которой формируются сигнапы сброса триггеров 31 и 32. Если оба триггера сброшены, схема 35 вырабатывает сигнал разреи.«ения записи з регистры 5 и 6 адресов, в регистр и другие триггеры блока управлегия. Если один из триггеров 31 или 32 не сброшен, выполняется обращение по адресу, оставшемуся необработанным, как описано выше, после чего разрешается запись чоаых адресов и упрайляющэй информации.

Дальнейшая работа происходит аналогичным образом.

Пример 1, Выполняется чтение по адресу AI. Младший бит адреса ai оавен нулю (строка 6, таб. 1).

Адрес Ai записывается в регистр 5. В триггер 31 записывается 1, в регистр 30 - код 00, в триггер 33 - код 0. На выходе 25 схемы 34 пояЁляется комбинация 0100, на выходе 27 - сигнал чтения блока 1. Коммутатор 7 подключает выход регистра 5 к а&- ресному входу блока 1, выполняется чтение по этому адресу. Выход блока 1 через коммутатор 4 подключается к первой выходной шине 22 данных. Схема 35 вырабатывает сигнал сброса триггера 31, после чего элемент 35 вырабатывает сигнал разрешения записи адресов и управляющей информации.

Пример 2. Выполняется чтение по адресу Ai и запись по адресу 2, Младшие биты адресов ai 1,32 0 (строка 17). Адреса AI и Аа записываются в регистры 5 и 5, В триггеры 31 и 32 записываются, единицы, в регистр 30 - код 01, в триггер 33 - код 0. На выходе 25 схемы 34 появляется комбинация 1001, в соответствии с которой выход регистра 5 подключается к адресному входу блока 2, а выход регистра б - к адресному входу блока 1. На выходах 26 -л 29 схемы 34 появляются сигналы зэписи блока 1 и чтения блока 2. К информационному входу блока 1 подключается через коммутатоо 3 вторая входная тина данных, г к выходу блока 2 - первая выходная шина данных через коммутатор 4. Одновременно происходит чтение блока 2 и запись з блок 1. На схема 36 формируются сигналы с&роса триггеров 31 и 32, а затем на выходе элемента ИЛИ-НЕ 35 появляется сигнал разрешения записи.

Пример 3. По обоим адресам происходит чтение, причем первым обслуживается второй адрес. Младшие биты обоих адресов равны единице (строка 32). Адреса записываются в регистры 5 и 6, в триггеры 31 и 32 записываются единицы, а регистр 30 - код 1, в триггер 33 - код 0.

На выходе 25 схемы 34 появляется комбинация 0010. К адресному входу блока 2 через коммутатор 7 подключается выход регистра 6. На выходе 29 схемы 34 появляется сигнал чтения блока 2. Выход этого блока через коммутатор 4 подключается к второй выходной шине данных. После чтения схемой 36 вырабатывается сигнал сброса триггера 32. Поскольку триггер 31 остается установленным, далее иг/.еет место комбинация, соответствующая строке 8. Выполняется обращение по адресу Ai. На выходе 25 схемы 34 появляется комбинация 1000. К адресному входу блока 2 через коммутатор 7 подключается выход регистра 5.

На выходе 29 появляется сигнал чтения блока 2, выход которого через коммутатор 4 подключается к первой выходной шине дан- :ых. После чтения триггер 31 сбрасывается и вырабатывается сигнал разрешения записи следующих адресов.

Аналогичным образом организуется работа устройства при других вариантах обработки адресов.

Формула изобретения 1. Оперативное запоминающее устройство, содержащее первый и второй блоки

памяти, первый и второй регистры адреса, блок управления, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены коммутатор входных данных, коммутатор выходных данных,

коммутатор адресов, информационные входы первого и второго блоков памяти соединены соответственно с выходами первой и второй групп коммутатора входных данных, информационные входы первой и второй

групп которого являются соответственно информационными входами первой и второй групп устройства, выходы первого и второго бпоков памяти соединены соответственное информационными входами первой и второй групп коммутатора выходных данных, выходы первой и второй групп которого являются соответственно информационными выходами первой и второй групп устройства, информационые входы первого и второго регистров адреса являются соответственно адресными входами первой и второй групп устройства, выходы первого и второго регистров адреса соединены соответственно с информационными входами первой и второй групп коммутатора адресов, выходы первой и второй групп которого соединены соответственно с адресными входами первого и второго блоков памяти, первый и второй входы задания

режима блока управления соединены с младшими выходами первого и второго регистров адреса,первый и второй входы признака обращения по адресам блока управления являются соответствующими

входами устройства, первый и второй входы задания режима по адресам блока управления являются соответствующими входами устройства, вход задания очередности обращения по адресам блока управления является одноименным входом устройства. первый выход блока управления соединен с управляющими входами адресного коммутатора, коммутатора входных и выходных данных, второй выход блока управления соединен с входом записи первого блока памяти и первым управляющим входом коммутатора входных данных, третий выход

блока управления соединен с входом чтения первого блока памяти и первым управляющим входом коммутатора выходных данных, четвертый выход блока управления соединен с входом записи второго блока памяти и вторым управляющим входом коммутатора входных данных, пятый выход блока управления соединен с входом чтения второго блока памяти и вторым управляющим входом коммутатора выходных данных, шестой выход блока управления соединен с входами синхронизации первого и второго регистров адреса.

управления, входы синхронизации первого, второго, третьего триггеров и регистра соединены с выходом элемента ИЛИ-НЕи являются выходом синхронизации блока управления, первый и второй входы элемента ИЛИ-НЕ соединены соответственно с выходами первого и второго триггеров, входы установки в исходное состояние первого и второго триггеров соединены соответственно с первым и вторым выходами второй логической схемы, входы которой соединены с первым выходом группы первой логической схемы и являются выходами задания режима блока управления, второй, третий, четвертый и пятый выходы первой логической схемы являются соответственно первым выходом записи, первым выходом Чтения, вторым выходом записи и вторым выходом чтения блока управления, первый и второй входы задания режима блока управления соединены с первым и вторым входами первой логической схемы, второй, третий, четвертый входы которой соединены соответственно с выходами первого, второго и третьего триггеров, пятые входы группы первой логической схемы соединены с выходами регистра.

Таблица 2

Фиг. 2

Авторы

Даты

1991-04-23—Публикация

1988-07-08—Подача