(54) ПРОЦЕССОР С ДИНАМИЧЕСКИМ МИКРОПРОГРАММНЫМ

1

Изобретение относится к цифровой вычислительной технике и может быть использовано при проектировании процессоров быстродействующих эмулир уемых вычислительных систем с микропрограммным управлением.

Известен процессор с микропрограммным управлением, содержащий операционный блок, блок данных, регистр и регистр адреса 1 .

tie}:i,ocraTOK процессора - недостач точная гибкость и универсальность, обусловленная статическим микропрограммированием.

Известен также процессор с динамическим микропрограммным управлением, содержащий регистр команд, операционный блок и блок управле- НИН 2.

Недостаток этого процессора заключается в низком быстродействии.

Наиболее близким к предлагаемому по технической сущности является процессор, содержащий регистры команд и адреса, операционный блок, узел ветвления, генератор импульсов и узел пуска-остановаС 3

Недостатком известного процессора является низкое быстродействие. , УПРАВЛЕНИЕМ

2

Цель изобретения - повышение быстродействия процессора.

Поставленная, цель достигается тем, что в процессор, содержащий регистр команд, регистр.адреса, операционный блок, блок ветвления, генератор импульсов, элемент И, командный, вход процессора соединен с информационным входом регистра

10 команд, первый разрядный выход которого соединен с первым информационным входом регистра адреса, выход которого является выходом адреса процессора, вход операндов процессо15ра соединен с первым информационным входом операционного блока, первый информационный выход которого соединен с-первым входом блока ветвления, выход генератора импульсов соединен

20 с первым входом элемента И, второй вход которого является первым управляющим входом процессора, вход адреса процессора соединен с вторым информационным входом регистра

25 адреса, второй информационный выход операционного блока является выходом операндов процессора, введены блоки элементов И, элемент ИИЛИ, элемент задержки/ сумматоры, 30 -дешифраторы, выход элемента И соединен с первым управляющим входом перв.ого сумматора, второй управляющий вход которого соединен с выходом элемента задержки и первым управляющим входом второго сумматора, выход первого сумматора соединен с вторым входом блока ветвления и входом первого дешифратора, группа выходов которого соединена с первой группой входов блоковэлементов И, с первого до п-го, и соединена с первой группой входов элемента И-ИЛИ вторая группа входов которого соеди.нена с первой группой разрядных выходов регистра команд, вторая группа разрядных выходов которого соединена с второй группой входов блоков элементов И, с первого до п-го,выходы которых соединены с входом микрокоманд бперационного блока и выходом микроопераций процессора, выход элемента И-ИЛИ соединен с вторым управляющим входом второго сумматора, выход которого соединен с входом второго дешифратора, группа выходов которого соединена с первой группой входов блока элементов И, с (п-1)-го до т-го, вторая группа входов которого соединена с третьей группой разрядных выходов регистра команд, выходы блоков элементов И, (п-И)-го до т-го,соединены с третьи входом блока ветвления, четвертый вход которого соединен с вторым разрядным выходом регистра команд,первый выход блока ветвления соединен с первым входом (п+т+1)-го блока элементов И, выход которого соединен с третьим информационным входом регистра адреса, второй вход (n+m+ +1)-го блока элементов И соединен с входом элемента задержки и выходом п-го блока элементов И,второй выход блока ветвления соединен с третьим управляющим входом первого сумматора, третий управляющий вход второго сумматора соединен с третьим входом блока ветвления.

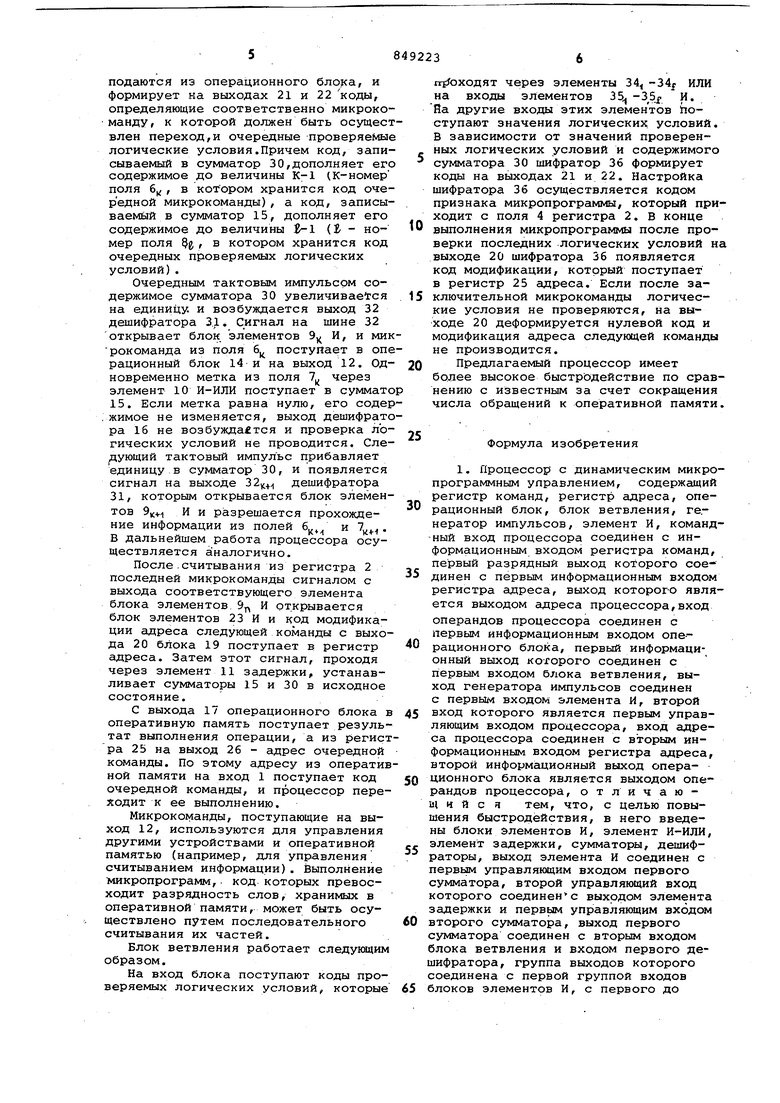

. Кроме того, блок ветвления содержит элементы И, ИЛИ и шифратор, выходы которого являются выходами блока, первый вход которого соединен с первым входом шифратора,, второй вход которого соединен с вторым входом блока, третий вход которого соединен с входами элементов ИЛИ, выходы которых соединены с третьим входом шифратора, четвертый вход блока соединен с вторыми входами элементов И.

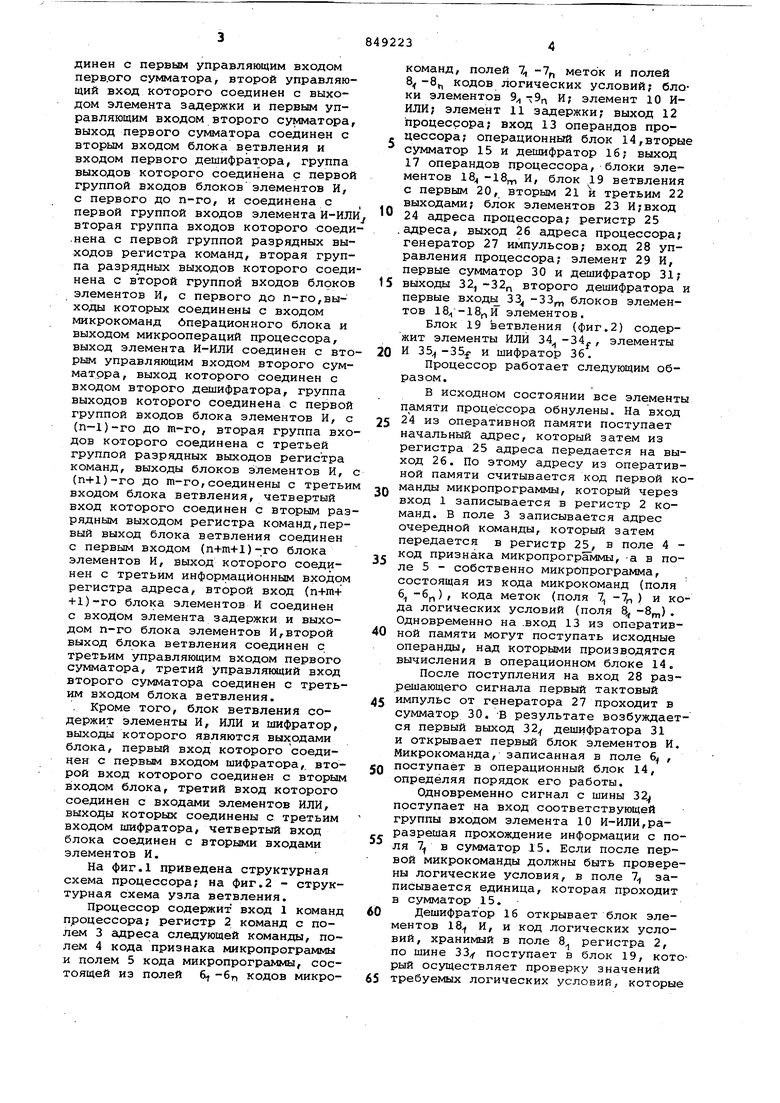

На фиг.1 приведена структурная схема процессора; на фиг.2 - структурная схема узла ветвления.

Процессор содержит вход 1 команд процессора; регистр 2 команд с полем 3 адреса следующей команды, полем 4 кода признака микропрограммы и полем 5 кода микропрограммы, состоящей из полей 6 -бг, кодов микрокоманд, полей 7, -7, меток и полей 8 -8„ кодов логических условий; блоки элементов И; элемент 10 ИИЛИ; элемент 11 задержки; выход 12 процессора; вход 13 операндов про, цессора; операционный блок 14,вторые сумматор 15 и дешифратор 16; выход 17 операндов процессора, блоки элементов 18 18рр И, блок 19 ветвления с первым 20, вторым 21 и третьим 22 выходами; блок элементов 23 И;вход

24 адреса процессора; регистр 25 .адреса, выход 26 адреса процессора; генератор 27 импульсов; вход 28 управления процессора; элемент 29 И, первые сумматор 30 и дешифратор 31;

5 вь1ходы 32 32г, второго дешифратора и первые входы 33 33 блоков элементов элементов.

Блок 19 ветвления (фиг.2) содержит элементы ИЛИ 34 34 , элементы

0 И .f и шифратор 36.

Процессор работает следующим образом.

В исходном состоянии все элементы памяти процессора обнулены. На вход

5 24 из оперативной памяти поступает начальный адрес, который затем из регистра 25 адреса передается на выход 26. По этому адресу из оперативной памяти считывается код первой коQ манды микропрограммы, который через вход 1 записывается в регистр 2 команд. В поле 3 записывается адрес очередной команды, который затем передается в регистр 25, в поле 4 код признака микропрограшлы, -а в поле 5 - собственно микропрограмма, состоящая из кода микрокоманд (поля 6 -б) , кода меток (поля 7, -7г, ) и кода логических условий (поля -8,„) . Одновременно на .вход 13 из оперативной памяти могут поступать исходные операнды, над которыми производятся вычисления в операционном блоке 14.

После поступления на вход 28 разрешающего сигнала первый тактовый

5 импульс от генератора 27 проходит в сумматор 30. -В результате возбуждается первый выход 32 дешифратора 31 и открывает первый блок элементов И. Микрокоманда, записанная в поле б ,

Q поступает в операционный блок 14, определяя порядок его работы.

Одновременно сигнал с шины 32 поступает на вход соответствующей группы входом элемента 10 И-ИЛИ,раразрешая прохождение информации с поля 7j в сумматор 15. Если после первой микрокоманды должны быть проверены логические условия, в поле 7 записывается единица, которая проходит в сумматор 15. 0 Дешифратор 16 открывает блок элементов 18 И, и код логических условий, хранимый в поле 8 регистра 2, по шине 33 поступает в блок 19, который осуществляет проверку значений

5 требуемых логических условий, которые подаются из операционного блока, и формирует ка выходах 21 и 22 коды, определяющие соответственно микрокоманду, к которой должен быть осущест влен переход,и очередные проверяемые логические условия.Причем код, записываемый в сумматор 30,дополняет его содержимое до величины К-1 (К-номер поля б| , в котором хранится код очередной микрокоманды), а код, записываемый в сумматор 15, дополняет его содержимое до величины -1 ( - номер поля §0, в котором хранится код очередных проверяемых логических условий). Очередным тактовым импульсом содержимое сумматора 30 увеличиваемся на единицу, и возбуждается выход 32 дешифратора 3.1. Сигнал на шине 32 открывает блок элементов 9 И, и мик рокоманда из поля 6 посту1 ает в опе рационный блок 14 и на выход 12. Одновременно метка из поля 7 через элемент 10 И-ИЛИ поступает в суммато 15. Если метка равна нулю, его содер . жимое не изменяется, выход дешифрато ра 16 не возбужда тся и проверка лЪгических условий не проводится. Следующий тактовый импульс прибавляет единицу в сумматор 30, и появляется сигнал на выходе 32, дешифратора 31, которым открывается блок элементов И и разрешается прохождение информации из полей 6, и 7. В дальнейшем работа процессора осуществляется аналогично. После .считывания из регистра 2 последней микрокоманды сигналом с выхода соответствующего элемента блока элементов 9„ И открывается блок элементов 23 И и код модификации адреса следующей команды с выхода 20 блока 19 поступает в регистр адреса. Затем этот сигнал, проходя через элемент 11 задержки, устанавливает сумматоры 15 и 30 в исходное состояние. С выхода 17 операционного блока в оперативную память поступает результат выполнения операции, а из регист ра 25 на выход 26 - адрес очередной команды. По этому адресу из оператив ной памяти на вход 1 поступает код очередной команды, и процессор переходит к ее выполнению. Микрокоманды, поступающие на выход 12, используются для управления другими устройствами и оперативной памятью (например, для управления считыванием информации). Выполнение микропрограмм, код которых превосходит разрядность слов, хранимых в оперативной памяти, может быть осуществлено путем последовательного считывания их частей. Блок ветвления работает следукнцим образом. На вход блока поступают коды проверяемых логических условий, которые 1г1 оходят через элементы 34, -34 ИЛИ на входы элементов 35 35 И. Йа другие входы этих элементов Ьоступают значения логических условий. В зависимости от значений проверенных логических условий и содержимого сумматора 30 шифратор 36 формирует коды на выходах 2l и 22. Настройка шифратора 36 осуществляется кодом признака микропрограммы, который приходит с поля 4 регистра 2. в конце выполнения микропрограммы после проверки последних логических условий на выходе 20 шифратора 36 появляется код модификации, который поступает в регистр 25 адреса. Если после заключительной микрокоманды логические условия не проверяются, на выходе 20 деформируется нулевой код и модификация адреса следующей команды не производится. Предлагаемый процессор имеет более высокое быстродействие по сравнению с известным за счет сокращения числа обращений к оперативной памяти. Формула изобретения 1. Процессор с динамическим микропрограммным управлением, содержащий регистр команд, регистр адреса, операционный блок, блок ветвления, ге.нератор импульсов, элемент И, командный вход процессора соединен с информационным входом регистра команд, первый разрядный выход которого сое- динен с первым информационным входом регистра адреса, выход которого является выходом адреса процессора,вход операндов процессора соединен с первым информационным входом опе-рационного блока, первый информационный выход которого соединен с первым входом блока ветвления, выход генератора импульсов соединен с первым входом элемента И, второй вход которого является первым управляющим входом процессора, вход адреса процессора соединен с вторым информационным входом регистра адреса, второй информационный выход операционного блока является выходом операндов процессора, отличающий с ч тем, что, с целью повышения быстродействия, в него введены блоки элементов И, элемент И-ИЛИ, элемент задержки, сумматоры, дешифраторы, выход элемента И соединен с nepBfciM управлянвдим входом первого сумматора, второй управляющий вход которого соединен с выходом элемента задержки и первьлм управляющим входом второго сумматора, выход первого сумматора соединен с вторым входом блока ветвления и входом первого дешифратора, группа выходов которого соединена с первой группой входов блоков элементов И, с первого до

n-го, и соединена с первой группой входов элемента И-ИЛИ, вторая группа входов которого соединена с первой группой разрядных выходов регистра команд,вторая группа разрядных которого соединена с второй группой входов блоков элементов И,с первого до п-го,выходы которых соединены е входом микрокоманд операционного блока и выходом микроопераций процессора, выход элемента И-ИЛИ соединен с вторым управляющим входом второго сумматора, выход которого соединен с входом второго дешифратора, группа выходов которогосоединена спервой группой входов блойа элементов И, с (п+1)-го до га-го, вторая группа.входов которого соединена /третьей группой разрядных выходов регистра команд, выходы блоков элементов И, с (п+1)-го до т-го, соединены с третьим входом блока ветвления, четвертый вход которого соединен с вторым разрядным выходом регистра команд, первый выход блока ветвления соединен с первым входом (п+т+1)-го блока элементов И, выход которого соединен с третьим информационным входом регистра адреса, второй вход (n+ro+D-ro блока элементов И соединен с входом элемента задержки и выходом Iv-ro блока элементов И, второй выход блока ветвления соединен с третьим управляющим входом первого сумматора.

третий управляющий вход второго сум.матора соединен с третьим входом блока ветвления.

2,Процессор .по п.1, отличающийся тем, что блок ветвления содержит элементы ИЛИ, элементы И и шифратор, выходы которого являются выходами блока ветвления, первый вхо которого соединен с первым входом шифратора, второй вход которого соединен с вторым входом блока ветвления, третий вход которого соединен

с входами элементов ИЛИ, выходы кото titax соединены с первьами входами элементов И, выходы которых, соединены с третьим входом шифратора, четвертый вход блока ветвления соединен с вторыми входами элементов И.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР .№ 525956, кл. G 06 F 15/20, G 06 F 9/14, 1976.

2, Палагин А.В. Мини-ЭВМ. Принцицы построения и проектирования. Киев, Наукова думка , 1975, с.71, Р. 18;

3.Атовиян И.О. и Березкин Е.Ф. Диагностическая процедура микропрограммного процессора.- Сб. Инженерно-математические методы в физике и кибернетике , М., Атомиздат, 1977, вып.6, 0.58, рис.1 (прототип).

Фиг:2

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммное устройство для контроля и управления | 1985 |

|

SU1325476A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1124299A1 |

| Микропрограммный процессор | 1987 |

|

SU1517034A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Перестраиваемый микропрограммный процессор | 1981 |

|

SU983713A1 |

| Процессор | 1985 |

|

SU1280378A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1108449A1 |

| Процессор с микропрограммным управлением | 1982 |

|

SU1124298A1 |

| Микропрограммный процессор | 1981 |

|

SU980095A1 |

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

Авторы

Даты

1981-07-23—Публикация

1979-10-22—Подача