(54) УСТРОЙСТВО ДЛЯ ВОССТАНОВЛЕНИЯ ИНФОРМАЦИИ В БЛОКАХ ПАМЯТИ

1

Изобретение относится к вычислительной технике и предназначено для использования в динамических запоминающих устройствах (ЗУ) на МДП-транзисторах.

Известны устройства для восстановления информации, которые используют адресный принцип управления регенерацией информации и обеспечивают принудительную регенерацию с запретом доступа внешних устройств к ЗУ. Эти устройства довольно сложны. Устройства содержат блок счетчиков, количество которых равно количеству адресов строк, необходимых для управления регенерацией 1 и 2.

Однако при количестве строк динамических ЗУ до 128 и более практическая реализация устройств представляет значительные трудности.

Наиболее близким по технической сущности к предлагаемому является устройство для восстановления информации. Это устройство содержит счетчик адресов, коммутатор, дещифратор, блок памяти, элемент И 3

Недостатком устройства является большое количество выходов блока памяти, а также рост их числа с увеличением количества адресов строк ЗУ, используемых для регенерации информации, что обусловлено использованием параллельного доступа к запоминающим элементам блока памяти для определения их состояния. Кроме того, это - накладывает определенные схемо-топологические ограничения при реализации на БИС. Цель изобретения - упрощение устройства и повышение его надежности.

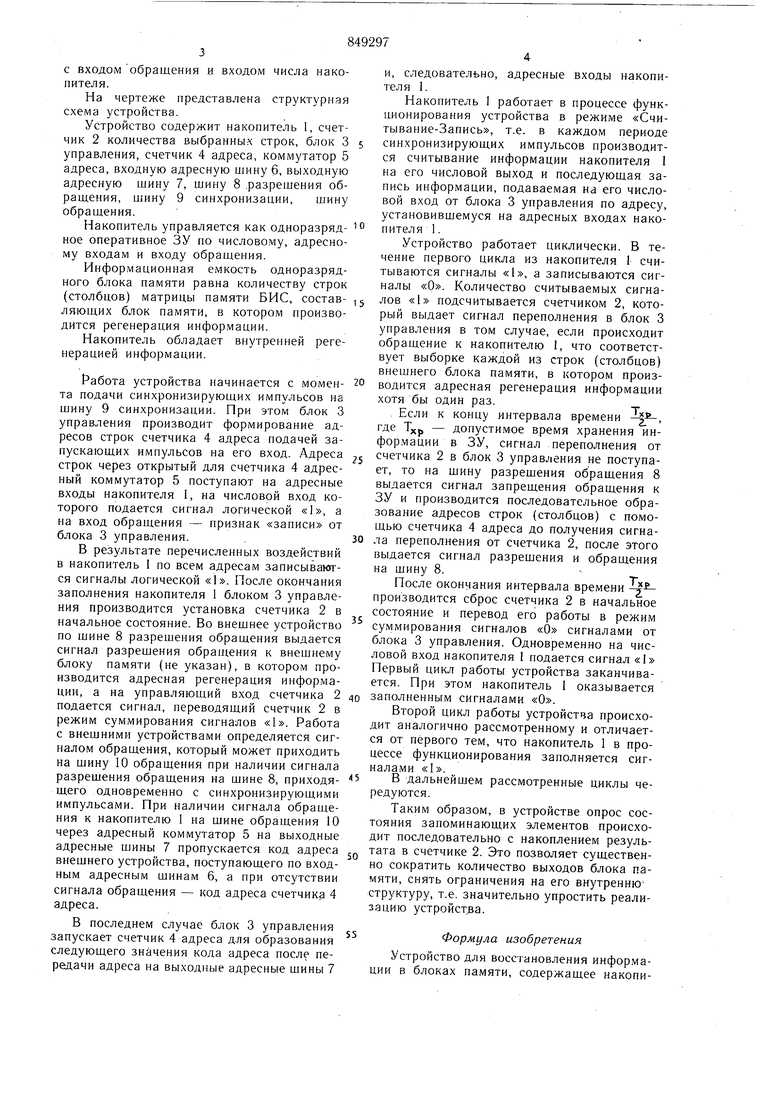

Поставленная цель достигается тем, что в устройство для восстановления информации в блоках памяти, содержащее накопитель, адресные входы которого соединены с выходами коммутатора адреса и выходной адресной шиной, а входы коммутатора адреса соединены с выходами счетчика адреса и первым выходом блока управления, вто15рой выход которого соединен с входом счетчика адреса, введен счетчик количества выбранных строк, информационный вход которого соединен с выходом накопителя, управляющие входы - с третьим и четвертым

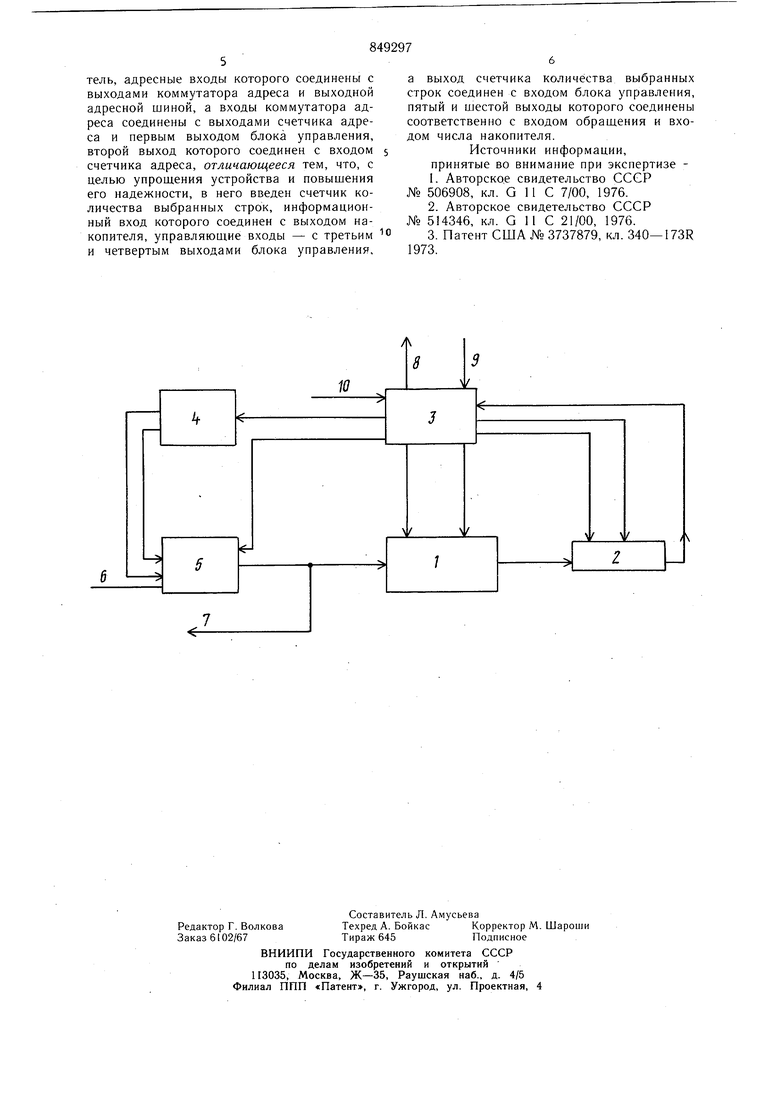

-д выходами блока управления, а выход счетчика количества выбранных строк соединен с входом блока управления, пятый и шестой выходы которого соединены соответственно е входом обращения и входом числа накопителя. На чертеже представлена структурная схема устройства. Устройство содержит накопитель 1, счетчик 2 количества выбранных строк, блок 3 управления, счетчик 4 адреса, коммутатор 5 адреса, входную адресную шину 6, выходную адресную шину 7, шину 8 разрешения обращения, шину 9 синхронизации, шину обращения. Накопитель управляется как одноразрядное оперативное ЗУ по числовому, адресному входам и входу обращения. Информационная емкость одноразрядного блока памяти равна количеству строк (столбцов) матрицы памяти БИС, составляющих блок памяти, в котором производится регенерация информации. Накопитель обладает внутренней регенерацией информации. Работа устройства начинается с момента подачи синхронизирующих импульсов на щину 9 синхронизации. При этом блок 3 управления производит формирование адресов строк счетчика 4 адреса подачей запускающих импульсов на его вход. Адреса строк через открытый для счетчика 4 адресный коммутатор 5 поступают на адресные входы накопителя 1, на числовой вход которого подается сигнал логической «I, а на вход обращения - признак «записи от блока 3 управления. В результате перечисленных воздействий в накопитель 1 по всем адресам записываются сигналы логической «1. После окончания заполнения накопителя 1 блоком 3 управления производится установка счетчика 2 в начальное состояние. Во внешнее устройство по щине 8 разрещения обращения выдается сигнал разрешения обращения к внещнему блоку памяти (не указан), в котором производится адресная регенерация информации, а на управляющий вход счетчика 2 подается сигнал, переводящий счетчик 2 в режим суммирования сигналов «1. Работа с внешними устройствами определяется сигналом обращения, который может приходить на щину 10 обращения при наличии сигнала разрещения обращения на шине 8, приходящего одновременно с синхронизирующими импульсами. При наличии сигнала обращения к накопителю I на шине обращения 10 через адресный коммутатор 5 на выходные адресные шины 7 пропускается код адреса внешнего устройства, поступаюшего по входным адресным шинам 6, а при отсутствии сигнала обращения - код адреса счетчика 4 адреса. В последнем случае блок 3 управления запускает счетчик 4 адреса для образования следующего значения кода адреса после передачи адреса на выходные адресные щинь 7 и, следовательно, адресные входы накопител я 1. Накопитель 1 работает в процессе функционирования устройства в режиме «Считывание-Запись, т.е. в каждом периоде синхронизирующих импульсов производится считывание информации накопителя 1 на его числовой выход и последующая запись информации, подаваемая на его числовой вход от блока 3 управления по адресу, установившемуся на адресных входах накопителя 1. Устройство работает циклически. В течение первого цикла из накопителя 1 считываются сигналы «1, а записываются сигналы «О. Количество считываемых сигнас1 подсчитывается счетчиком 2, котоловрый выдает сигнал переполнения в блок 3 управления в том случае, если происходит обращение к накопителю 1, что соответствует выборке каждой из строк (столбцов) внешнего блока памяти, в котором производится адресная регенерация информации хотя бы один раз. Если к концу интервала времени , где Тцр - допустимое время хранения информации в ЗУ, сигнал переполнения от счетчика 2 в блок 3 управления не поступает, то на щину разрещения обращения 8 выдается сигнал запрещения обращения к ЗУ и производится последовательное образование адресов строк (столбцов) с помощью счетчика 4 адреса до получения сигнала переполнения от счетчика 2, после этого выдается сигнал разрещения и обращения на шину 8. После окончания интервала времени - производится сброс счетчика 2 в начальное состояние и перевод его работы в режим суммирования сигналов «О сигналами от блока 3 управления. Одновременно на числовой вход накопителя 1 подается сигнал «1 Первый цикл работы устройства заканчивается. При этом накопитель 1 оказывается заполненным сигналами «О. Второй цикл работы устройства происходит аналогично рассмотренному и отличается от первого тем, что накопитель 1 в процессе функционирования заполняется сигналами «1. В дальнейшем рассмотренные циклы чередуются. Таким образом, в устройстве опрос состояния запоминающих элементов происходит последовательно с накоплением результата в счетчике 2. Это позволяет существенно сократить количество выходов блока памяти, снять ограничения на его внутренню структуру, т.е. значительно упростить реализацию устройства. Формула изобретения Устройство для восстановления информации в блоках памяти, содержащее накопитель, адресные входы которого соединены с выходами коммутатора адреса и выходной адресной шиной, а входы коммутатора адреса соединены с выходами счетчика адреса и первым выходом блока управления, второй выход которого соединен с входом s счетчика адреса, отличающееся тем, что, с целью упрощения устройства и повышения его надежности, в него введен счетчик количества выбранных строк, информационный вход которого соединен с выходом накопителя, управляющие входы - с третьим и четвертым выходами блока управления.

а выход счетчика количества выбранных строк соединен с входом блока управления, пятый и шестой выходы которого соединены соответственно с входом обращения и входом числа накопителя.

Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 506908, кл. G 11 С 7/00, 1976.

2.Авторское свидетельство СССР № 514346, кл. G 11 С 21/00, 1976.

3.Патент США № 3737879, кл. 340-173R 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1985 |

|

SU1278984A1 |

| Динамическое полупроводниковое запоминающее устройство | 1979 |

|

SU1001173A1 |

| Динамическое запоминающее устройство | 1983 |

|

SU1166177A1 |

| Устройство для регенерациииНфОРМАции B диНАМичЕСКиХблОКАХ пАМяТи | 1979 |

|

SU809388A1 |

| Запоминающее устройство | 1977 |

|

SU733021A1 |

| Динамическое запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1133625A1 |

| Логическое запоминающее устройство | 1979 |

|

SU864336A1 |

| Запоминающее устройство с произвольным доступом и одновременной выборкой переменного массива слов | 1983 |

|

SU1167655A1 |

| Запоминающее устройство с самоконтролем | 1978 |

|

SU763977A1 |

| Запоминающее устройство с само-КОНТРОлЕМ | 1979 |

|

SU836682A1 |

Авторы

Даты

1981-07-23—Публикация

1978-10-04—Подача