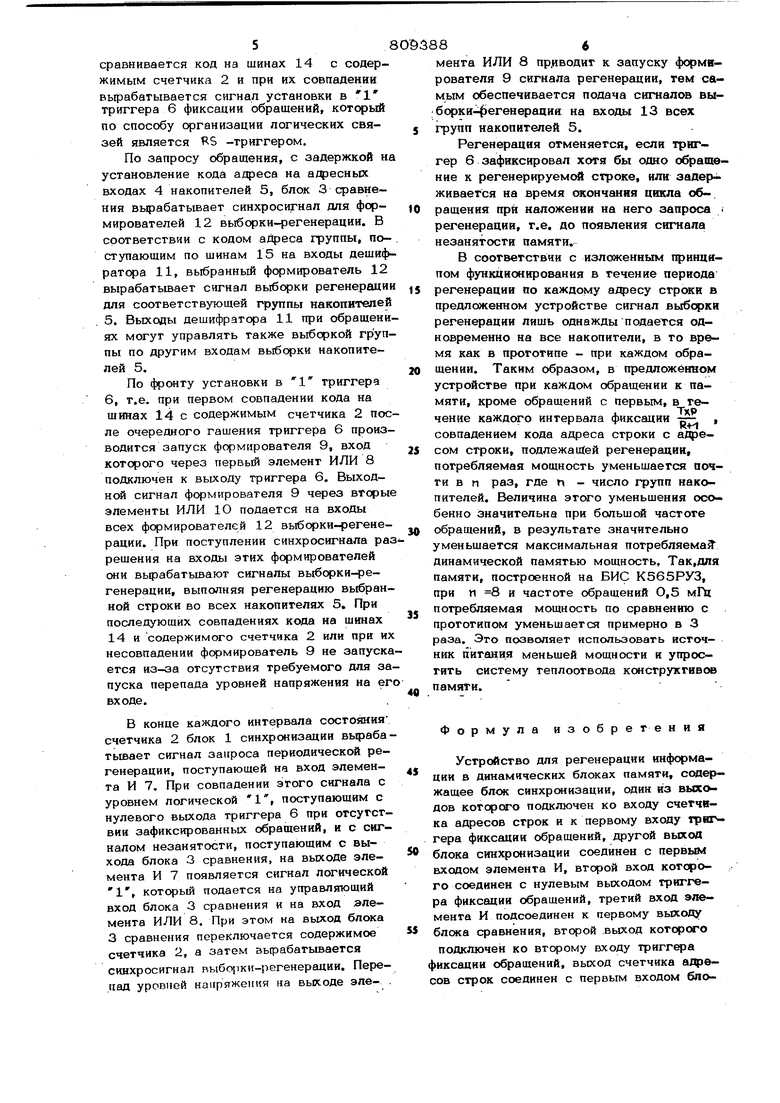

Изобретение относится к вычнслигель ной технике и предназначено для использования в полупроводниковых запоминающих устройствах с динамическими блоками памяти, объединенными в группьи Известно устройство, обеспечивающее регенерацию информации в динамических блоках памяти, которое использует свойство автоматической регенерации адресуемой строки в блоках памяти при любом обращении. Устройство содержит блок управления, дешифратор, элементы памяти, элемент И, коммутатор и счетчик адреса регенерация всей памяти запрещается до разряда емкости одного или нескольких элементов фиксации обращений, заряжающихся после обращений к соответствующим строкам l. Известно устройство,более оптимально использующее указанное свойство за счет регенерации только тех строк, к которым не было обращений. Это устройство дополнителыго содержит элементы И и щифрато() :.2 . Недостатком обоих устройств являегся сложность аппаратурной реализации, связанная с использованием больщого количества элементов фиксации обращений. Наиболее близким из известных по технической сущности является устрсЛство, которое отменяет очередную регенерацию, если в течение интервала ТГг - (Т.г,допустимый период хранения информации, R - количество строк) перед запросом регенерации строки к ней было зафиксировано обращение. Оно содержит блсж синхронизации, выходы которого подключены к счетному входу счетчика строк, первому входу элемента фиксации обращений и первому входу элемента И, выходы счетчика подключены к первым информационным входам блока разрещения обращения и регенерации, ко вторым информационным входам которого подключены кодовые шины адреса, соответствующие выходы блока разрещения подключены к адресным входам блоков памяти, входам формирователей сигналов вьйорки-регенерации, второму входу элемента И и второму входу элемента фиксации обращений, выход которого подключен к третьему входу элемента И, а выход элемента И подключен к управляющему входу блока разрешения Гз, Однако при управлении регенерацией с помощью как этого, так и ранее рассмотренных устройств, при каждом обращении к памяти необходимо подавать разрешающий сигнал выборки-регенерации, как и при регенерации, на входы выборки-регенерации. (СЕ ипи RA5 - в зависимости от типа микросхемы) всех блоков памяти в каждом разряде. При подаче этого.сигнала динамически блоки памяти переходят в активный режим работы и потребляемая ими мощность воз растает в Ю и более раз. Поэтому такая организация регенерации приводит к допол нительному расходу мощности для накопителей большой емкости, содержащих не сколько групп блоков памяти. Каждай группа представляет собой полноразрядную часть накопителя, выбираемую при обраще киях по /фугим входам выборки блоков памяти { С5 или СА5 - в зависимости от типа микросхемы) с помощью дешифратора групп. Последовательная же регенерация групп невыгодна, так как обратно пропорционально их количеству уменьшается длительность i/ , что приводит к резкому снижению эффективности управления регенерацией с использованием обращений, и затраты времени на регенерацию при отсутствии зафиксированных обращений возрастают пропорционально количеству груп Цель изобретения - снижение потребляемой мощности за счет уменьшения числа сигналов выборки-регенерации. Поставленная цель достигается тем, что в устройство для регенерации информации в динамических блоках памяти, содержащее блок синхронизации, один из вькодов которого подключен ко входу счетчика адресов строк и к первому входу триггера фиксации обращений, другой выход блока синхронизации соединен с первым входом элемента И, второй вход которсйго соединен с нулевым выходом триггера фиксации обращений, третий вход элемента И подсоединен к первому вых-оау блока сравнения, второй выход ко торого подключен ко второму входу триггера фиксации обращений, выход счетчика .адресов строк соединен с первым вх дом блока сравнения, второй вход которого подсоединен к кодовой шине адреса отрете, выход элемента И соединен с третьим входом блока сравнения, четвертый вход которого подключен к шине управления, третий выход блока сравнения соединен с адресными входами накопителей, входы выборки-регенерации которых соединены с выходами формирователей сигнала выборки-регенерации, дешифратор выборки групп накопителей, вход KOTqjoro соединен с кодовой шиной адреса группы накопителей, четвертый выход блока сравнения соединен с одним из. входов формирователей сигнала выборкирегенерации, введены элементы ИЛИ и формирователь сигнала регенерации, вход которого соединен с выходом первого элемента ИЛИ, один из входов первого элемента ИЛИ подключен к единичному выходу триггера фиксации обращений, другой вход первого элемента ИЛИ соединен с выходом элемента И и управляющим выходом устройства, выход формирователя сигнала регенерации подключен к первым входам вторых элементов ИЛИ, вторые входы которых соединены с выходами де шифратора выборки групп, накопителей, выходы BTqjbCc элементов ИЛИ подключены к другим входам формирователей сигнала выборки-регенерации. На чертеже изображено устройство, функциональная схема. Оно содержит блок 1 синхронизации, счетчик 2 адресов строк, блок 3 сравнения, адресные входы 4 накопителей 5, триггер 6 фиксации обращений, элемент И 7, первый элемент ИЛИ 8, формирователь 9 сигнала регенерации, вторые элементы ИЛИ 1О, дешифратор 11 выборки групп накопителей, формирователи 12 сигнала вьборки-регенерации, входы 13 выборки-регенерации накопителей 5, кодовая шина Г4 адреса строк, кодовая шина 15 адреса группы накопителей, шина 16 управления и управляюший выход 17 устройства. Работа устройства осуществляется следующим образом. Устройство принимает из прсщессора запросы обращений к памяти и посылает в процессор квитирующие сигналы выполнения циклов регенерации.Блок 1 синхронизации с частотой г изменяет состояние счетчика 2 и одновременно с этим производит гашение триггера 6 фиксации обращений. При отсутствии запросов регенерации по шине 16 управления кодовая шина 14 адреса строк подключена к адресным вхо;дам 4 накопителей 5. По запросам обращений из процессора в блоке 3 сравнения сравнивается код на шинах 14 с содержимым счетчика 2 и при их совпадении вырабатывается сигнал установки в триггера 6 фиксации обращений, который по способу организации логических связей является RS -триггером. По запросу обращения, с задержкой н установление кода адреса на адресных входах 4 накопителей 5, блок 3 сравнения вырабатывает синхросгагнал для формирователей 12 выборки-регенерации. В соответствии с кодом адреса группы, поступающим по шинам 15 на входы деши(| ратсра 11, выбранный формирователь 12 вырабатьшает сигнал выборки регенераци для соответствующей группы накопителей . 5. Выходы дешифратора 11 при обращени ях могут управлять также выборкой группы по другим входам вьйорки накопителей 5. По фронту установки в 1 триггера 6, т.е. при первом совпадении кода на щшах 14 с содержимым счетчика 2 пос ле очередного гашения триггера 6 производится запуск формирователя 9, вход которого через первый элемент ИЛИ 8 подключен к выходу триггера 6. Выходной сигнал формирователя 9 через вторые элементы ИЛИ 1О подается на входы всех формирователей 12 выборки-регенерации. При поступлении синхросигнала раз решения на входы этих формирователей они вьфабатьшают сигналы выборки-регенерации, выполняя регенерацию выбранной строки во всех накопителях 5. При последующих совпадениях кода на шинах 14 и содержимого счетчика 2 или при их несовпадении формирователь 9 не запуска ется из-за отсутствия требуемого для за пуска перепада уровней напряжения на ег входе. В конце каждого интервала состояния счетчика 2 блок 1 синхронизации вьфабатьшает сигнал запроса периодической регенерации, поступающей на вход элемента И 7. При совпадении этого сигнала с уровнем логической , поступающим с нулевого выхода триггера 6 при отсутствии зафиксированных обращений, и с сигналом незанятости, поступающим с выхода блока 3 сравнения, на выходе элемента И 7 появляется сигнал логической , который подается на управляющий вход блока 3 сравнения и на вход элемента ИЛИ 8. При этом на выход блока 3 сравнения переключается содержимое счетчика 2, а затем вьсрабатывается синхросигнал выборки-регенерации. Перепад уровней напряжения на выходе эле- . мента ИЛИ 8 пр,иводит к запуску формирователя 9 сигнала регенерации, тем самым обеспечивается подача сигналов выбс кн-фегенерацнв на входы 13 всех групп накопителей 5. Регенерация отменяется, если триггер 6 зафиксировал хотя бы ошю обращение к регенерируемсЛ строке, или задери живается на время окончания цикла обращения при наложении на него запроса регенерации, т.е. до появления сигнала незанятости памяти. В соответствии с изложенным принципом функционирования в течение периода регенерации по каждому адресу строки в предложенном устройстве сигнал выбсрки регенерации лишь однажды подается одновременно на все накопители, в то время как в прототипе - при каждом обращении. Таким образом, в предложенном устройстве при каждом обращении к памяти, кроме обращений с первым, в течение каждого интервала фиксации - , совпадением кода адреса строки с адресом строки, подлежащей регенерации, потребляемая мощность уменьшается почти в п раз, где г - число групп накопителей. Величина этого уменьшения особенно значительна при большой частоте обращений, в результате значительно уменьшается максимальная потребляема динамической памятью мощность, Так,для памяти, построенной на БИС К565РУЗ, при п 8 и частоте обращений О,5 мГ потребляемая мощность по сравнению с прототипом уменьшается примерно в 3 раза. Это позволяет использовать источник питания меньшей мощности и упростить систему теплоотвода ксиструктивов памяти. Формула изобретения Устройство для регенерации информации в динамических блоках памяти, сод жащее синхронизации, один из выходов которсго подключен ко входу счетчвка адресов строк и к первому входу триггера фиксации обращений, другой выход блока синхронизации соединен с первым входом элемента И, второй вход которого соединен с нулевым выходом триггеа фиксации обращений, третий вход элемента И подсоединен к первому выходу блока сравнения, второй выход которого подключен ко второму входу триггера иксации обращений, выход счетчика адреов строк соединен с первым входом блока сравнения, второй вход которого подсоединен к кодовой шине адреса строк, выход элемента И соединен с третьим входом блока сравнения, четвертый вход которс о подключен к шине управления,

третий выход блока сравнения соединен с афесными входами групп накопителей, входы выборки-регенерации которых соединены с выходами формирователей сигнала выборки-регенерации, дешифратор выборки групп накопителей, вход которого соединен с кодовой шиной адреса группы накопителей, четвертый выход блока сравнения соединен с одними из входов формирователей сигнала выборки-регенерации, о т л и ч аю ш е е с я тем, что) с целью снижения потребляемой мощности за счет уменьшения числа сигналов выборки-регенерации, в него введены элементы ИЛИ и фс мирователь сигнала регенерации, вход которого соединен с выходом первого элемента ИЛИ, один из входов первого элемента

ИЛИ подключен к единичному выходу триггера фиксации обращений, другой вход первого элемента ИЛИ соединен с выходом элемента И и управляющим выходом устройства, выход формирователя сигнала регенерации подключен к первым входам вторых элементов ИЛИ, вторые входы которых соединены с выходами дешифратора выборки групп накопителей, выходы вторых элементов ИЛИ подключены к другим входам формирователей сигнала выборкирегенерации.

Источники инфс мации, принятые во внимание при экспертизе

1.Автсч ское свидетельство СССР

№ 637863, кл. Q Ц С 7/ОО, 2.О2. 79

2.Авторское свидетельство СССР

NO 514346, кл. q 11 С 21/00, опублик. 1976.

3.Патент США № 376О379,

кл. 34О-173Р, опублик. 1973 (прототип)

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления динамической памятью | 1987 |

|

SU1524089A1 |

| Устройство для отображения информации | 1986 |

|

SU1506478A1 |

| Устройство для управления регенерацией информации в динамической памяти | 1985 |

|

SU1374280A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1125657A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Устройство для управления полупровод-НиКОВыМ НАКОпиТЕлЕМ | 1979 |

|

SU842811A1 |

| Оперативное запоминающее устройство | 1988 |

|

SU1580442A1 |

| Устройство для контроля оперативной памяти | 1983 |

|

SU1295455A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 1991 |

|

RU2017241C1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО ИЗОБРАЖЕНИЙ | 1990 |

|

RU2047921C1 |

f7 Q процессор

Авторы

Даты

1981-02-28—Публикация

1979-06-11—Подача