(54) РЕЗЕРВИРОВАННОЕ ЗАПОМИНА 0 1ЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1981 |

|

SU982086A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1070608A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1080217A1 |

| Резервированное запоминающееуСТРОйСТВО | 1978 |

|

SU803014A1 |

| Резервированное запоминающее устройство | 1980 |

|

SU936034A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1149319A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Резервированное запоминающее устройство | 1979 |

|

SU881875A2 |

| Резервированное запоминающее устройство | 1983 |

|

SU1149317A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1076953A1 |

Изобретение относится к запоминающим устройствам.

Известно резервированное запомина Ю1дее устройство, срлержащее основные и резервные блоки памяти, блоки формирования адреса, коммутаторы и блок контроле С 11

Недостатком этого устройства я-вля ется большой объем резервного оборудования.

Наиболее близким по технической сущности к изобретению является резервированное запоминающее устройство, содержащее регистр адреса, два рабочих блока .памят.и и один резервный блок (в который занесена поразрядная сумма по модулю два информации одноименных разрядов соответствующих ячеек рабочих блоков памяти), три коммутатора, блок контроля, сумматор, генератортактовых импульсов, элепбнтн И С2.

Недостатком этого устройства является низкая надежность при использовании его в качестёе ОЗУ,так как в случае записи в один из рабочих блоков памяти и неисправности в одноименной ячейке другого рабочего блока памяти в резервный блок памяти будет записана неверная информация.

что не позволит восстановить правильную информацию при считывании из рабочих блоков памяти.

Целью изобретения является повьлыение надежности уст эойства.

Поставленная цель достигается тем, что в резервированное запоминающее устройство, содержащее основные и резервный блоки памяти, коммутато10ры, блок контроля, первый по модулю два, группу элементов И и генератор тактовых импульсов, BJJход которого подключен к одним из входов элементов П группы, причем ; выходы первого основного блока памяти соединены с одними извходов первого и второго коммутаторов, другие входы которых подключены к выходам второго основного блока памяти, вы20ходы первого коммутатора соединены с входами блока контроля и одними из входов третьего комг-тутатора, управляющий вход, которого подключен к выходу блока контроля, а другие входы

25 соединены с выходами первого сумматора по модулю два, входы которого подключены соответственно к выходам резервного блока памяти и к выходам второго коммутатора, выходы третьего

30 коммутатора соединены с другими входами элементов И группы, выходы которых являются выходами устройства, введены 6л.ок местного управления, регистр и второй сумматор по модулю два, входы которого соединены соответственно с выходами третьего коммутатора и с информационными входами Основных блоков памяти, а выходы подключены к информационным входам регистра, управляющий вход которого соединен с выходом генератора тактовых 1 1пульсов, а выходы подключены к информационным входам резервного блока памяти, управляющий вход которого и управляющие входы основных блоков памяти и первого и второго /коммутато DOB соединены соответственно с выходами блока местного управления, входы которого являются управляющими входами устройства, информационными входами которого являются информационные входы основных блоков памяти.

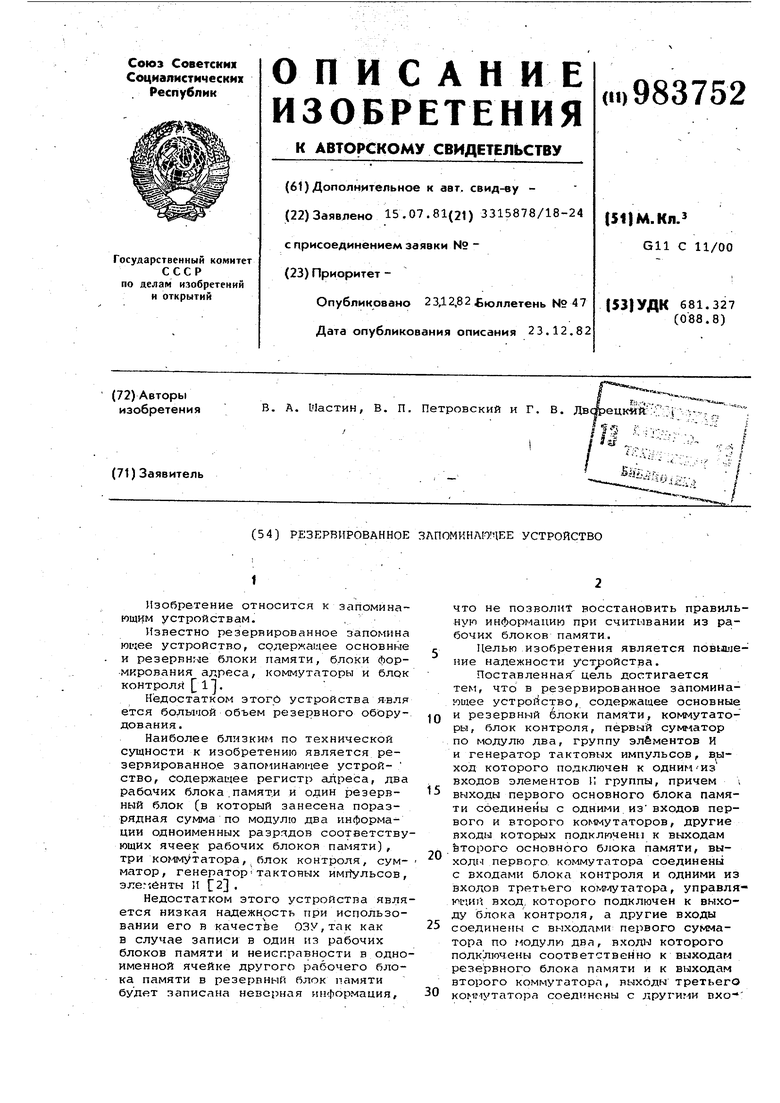

Кроме того, блок местного управления содержит элементы И, элемент НЕ, элемент Неравнозначность и элемент задержки, выход которого соединен с первыми входами элементов И, а вход - с первым входом элемента Неравнозначность, второй вход которого подключен к второму входу первого элемента И и входу элемента НЕ, выход которого соединен с вторым входом второго элемента И, вход элемента задержки и второй вход элемента Неравнозначность являются входами блока, выходами которого являются соответственно выходы элементов И, эле мента задержки и элемента Неравнозначность.

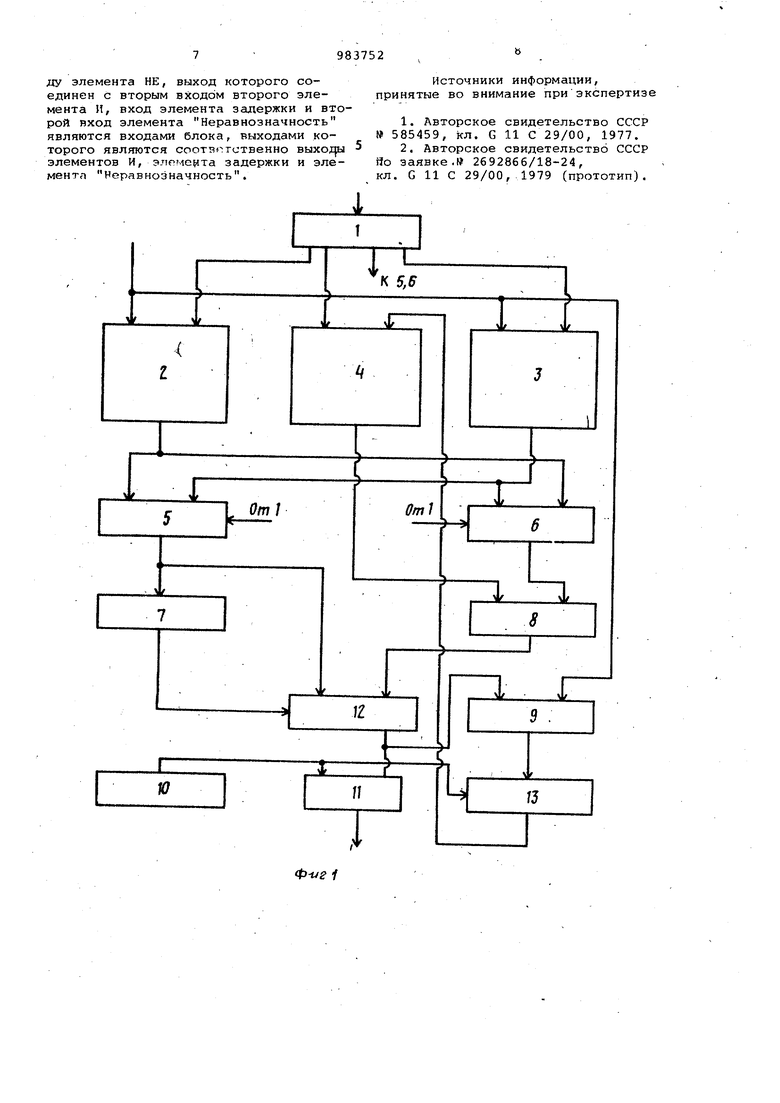

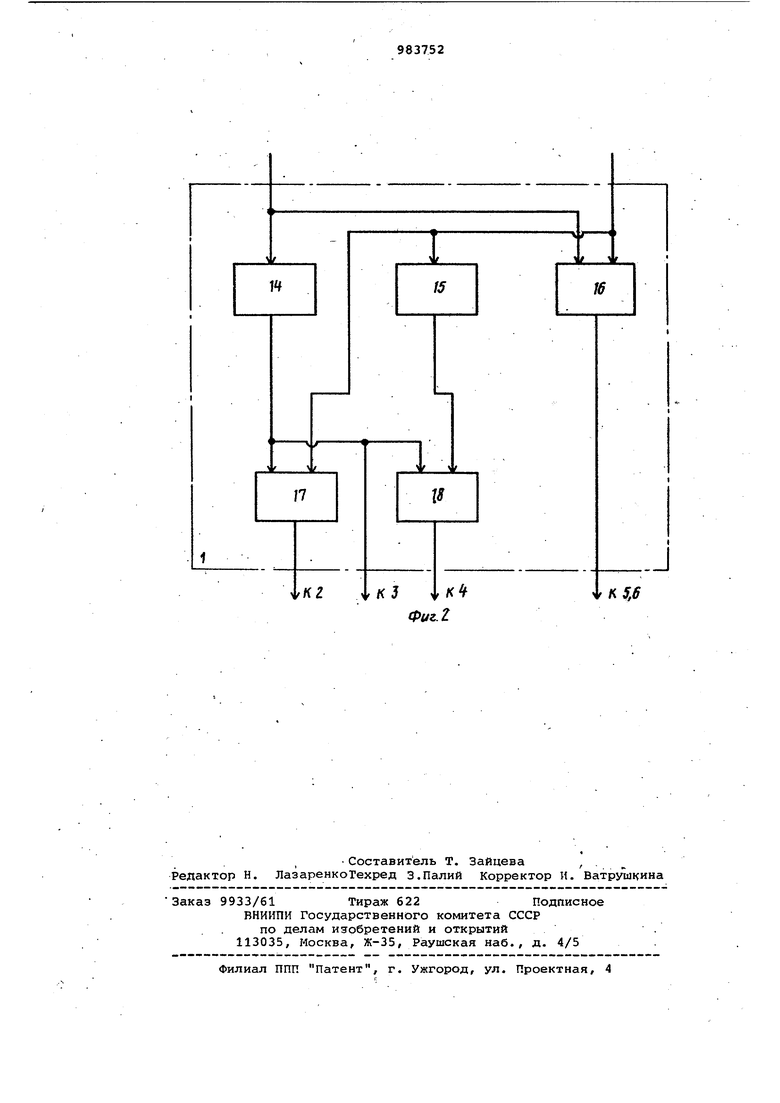

На.фиг. 1 приведена функциональная схема предлагаемого устройства, на фиг. 2 - то же, блока местного управления.

Предлагаемое устройство содержит блок 1 местного управления, первый 2 и второй 3 основные блоки памяти, , резервный блок 4 памяти, первый 5 и второй б коммутаторы, блок 7 контроля, первый 8 и второй 9 сумматоры по модулю два, генератор 10 тактовых импульсов, группу 11 элементов И по числу разрядов слова, третий коммутатор 12 и регистр 13.

Блок местного управления (фиг, 2) содержит элемент 14 задержки, элемент НЕ 15, элемент Неравнозначност 16, первый 17 и второй 18 элементы И

Устройство работает следующим образом.

Устройство может функционировать в двух режимах: режиме записи и режиме считывания информации.

Работа устройства в режиме записи например, в бЛок 3 памяти (фиг. 1) происходит следующим образом.

На вход элемента 14 задержки (фиг. 2) и на первый вход элемента

Неравнозначность 16 поступает сигнал записи (например, единичным уровнем) . На второй вход элемента Неравнозначность 16 поступает сигнал обращения к блоку 3 памяти (например, нулевым уровнем).

На информационные входы блоков 2 fi 3 f а также на второй вход сумматора 9 поступает информация, предназначенная для записи по определенному адресу (адресные входы блоков 2, 3 и 4 нафиг. 1 не показаны). До момента появления сигнала на выходе элемента 14 задержки (фиг. 2) на первом втором и третьем выходах блока 1 сигнал записи отсутствует.и блоки 2, 3 и 4 (фиг. 1) находятся в режиме считывания информации одноименных ячеек соответствующих адресу, по которому должна производиться запись информации. С выхода элемента Неравнозначность 16 (фиг. 2) поступает сигнал управления первым 5 (фиг. 1) и вторым 6 коммутаторами, который разрешает прохождение через коммутатор 5 на первые входы коммутатора 12 и на входы блока 7 информации, считываемой из блока 2, а через коммутатор 6 на вторые входы сумматора 8 инфорглации, считываемой из блока 3 памяти. На первые входы сумматора 8 поступает инфop Iaция из резервного блока 4.

Поразрядная сумма по модулю два информации, поступившей из блоков 3 и 4 памяти, .с выхода сумматора 8 поступает на вторые входы коммутатора 12 (фиг. 1). Если блоком 7 не зарегистрировано искажение информации, поступившей с выхода коммутатора 5, то он вырабатывает сигнал, разрешающий прохождение этой информации через коммутатор 12 на вторые входы элементов И 11 и на первые входы сумматора 9. Если результат контроля отрицательный, то через коммутатор 12 на вторые входы элементов И 11 и на первые входы сумматора 9 поступает информация с выходов сумматора 8,

Поразрядная сумма о модулю два информации, поступившей с в ыходов ко,мутатора 12 и информационных входов устройства, поступает с выхода сумматора -9 на информационные входы регистра 13, запись в которой производится по тактовому импульсу генератора 10. С выхода реигистра 13 информация поступает на информационные входы резервного блока 4 памяти.

После появления на выходе элемента 14 задержки (фиг. 2) сигнала записи, на втором и, через элемент И 1В, на третьем выходе блока 1 появляются сигналы, которые поступают на управляющие входы соответственно резервного 4 и основного 3 блоков памяти, разрешая запись по заданному адресу информации, находящейся на информационных входах блоков 4 и 3. Период времени, на который задерживается сигнал записи, поступивший .на вход элемента 14 задержки (фиг. 2 и интервалы следования импульсов ген ратора 10 (фиг. 1) должны соответствовать следую1чии условием ЬоА 1 7. t 7/ t. - t, + inax(t5-, % где t, - время от начала обрамения к устройству до момента .ус тановки информации- на инфо мационные входы резервного блока 4 памяти7 t - время от начала обращения к устройству до переднего фронта тактового импульса генератора 10, t - задержка сумматора 9 tj - задержка блоков 2, 3 и 4 J t - задержка коммутатора (приJ нята одинаковой для всех трех коммутаторов 5, б и 12); tg. - задержка блока 7, t - задержка сумматора 8, t7 - задержка регистра 13. Запись информации в блок 2 памяти производится аналогично описанному. При этом на второй вход элемента Неравнозначность 16 (фиг, 2) посту пает сигнал обращения к блоку 2 (фиг.1) памяти (например, единичным уровнем), формируя, совместно с задержанным сигналом записи, на первом и втором выходах блока 1 сигналы управления, разрешающие запись инфор мации соответственно в блок 2 (фиг.1 и резервный блок 4 памяти. Работа предлагаемого устройства в режиме считывания аналогична работе известного устройства и отличается от работы в режиме записи только тем, что на первый, второй и третий выходы блока 1 (фиг. 2) сигналы, управления записью не поступают, а на четвертом выходе появляется сигнал управления коммутаторами 5 и 6 (фиг обеспечивающий считывание требуемой информации с выхода заданного блока 2 или 3 памяти через элементы И 11 по тактовоь1у импульсу генератора 10 на выход устройства. Таким образом, устройство обеспечивает возможность записи достоверной информации в блоки 2 и 3 памяти и восстановления информации, записываемой в один из этих блоков (при неиспрайности одного из блоков 2 или всех блоков 2-4, если адреса неисправных ячеек не совпадают) путе организаций перед записью считывания информации из другого блока 2 или 3 формирования поразрядной суммы по модулю два считанной и записываемой информации и занесения этой суммы в резервный блок 4 памяти. Технико-экономическое преимущество предлагаемого устройства заключается в более высокой, по сравнению с известным надежности при использовании его в качестве ОЗУ. Формула изобретения 1.Резервированное запоминающее устройство, содержащее основные и резервный блоки памяти, коммутаторы,, блок контроля, первый сумматор по модулю два, группу элементов И и генератор тактовых импульсов, выход которого подключен к одним из входов элементов И группы, причем выходы первого основного блока памяти соединены с одними из входов первого и второго коммутаторов, другие входы которых подключены к выходам второго основного блока памяти, выходы первого коммутатора соединены с входс1ми блока контроля и одними из входов треть его коммутатора, управляющий вход которого подключен к выходу блока контроля, а другие входы соединены с выходами первого сумматора по модулю два, входы которого подключены соответственно к выходам резервного блока памяти и к выходам второго коммутатора, выходы третьего коммутатора соединены с другими входами эле- ментов И группы, выходы которых являются выходами устройства, о т л ичающееся тем, что, с целью повышения надежности устройства, в него введены блок местного управления, регистр и второй сумг1атор по модулю два, входы которого соединены соответственно с выходами третьего коммутатора и с информационными входами основных блоков памяти, а выходы подключены к информационным входам регистра, управляющийвход которого соединен с выходом генератора тактовых импульсов, а выходы подключены к информационным входам резервного блока памяти, управляющий вход которого и управляющие входы основных блоков памяти и первого и второго коммутаторов соединены соответственно с выходами блока местного управления, входы которого являются управляющими входами устройства, информационными входами которого являются информационные входы основных блоков памяти. 2.Устройство по п. 1, отличающееся тем, что блок местного управления содержит элементы И, элемент НЕ, элемент Неравнозначность и элемент задержки, выход которого соединен с первыми входами элементов П,а вход - с первым входом элемента Неравнозначность, второй вход которого подключен к второму входу первого элемента И и входу элемента НЕ, выход которого соединен с вторым входом второго элемента И, вход элемента задержки и второй вход элемента Неравнозначность являются входами блока, выходами которого являются соотвпгственно BHXOJ элементов И, элемента задержки и элемент Неравнозначность.

I

Oml

1

Источники информации, принятые во внимание при экспертизе

кл. G 11 С 29/00, 1979 (прототип).

Т

К 5,5

I

ОтП

3 :

If

s

ГЗ

т

Авторы

Даты

1982-12-23—Публикация

1981-07-15—Подача