(54) ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ ИСЧИСЛЕНИЯ ФУНКВДЙ

1

Изобретение относится к вычис лительной технике и предназначено для использования в информационновычислительных системах, дискретных преобразователях координат, в аисте-, мах с функциональными npeoepiasosaTeлями дискретной информации.

Известно устройство, содержащее . блок памяти, регистру информационные входы которого соединены с информационными входами устройства, выходы регистра через первую группу элементов И соединены со входами блока адресации, а через вторую группу элементов И с подключенным к выходу устройства, выходы блока адресации подключены ко входам первого коммутатора, управляющие входы цервой и второй групп элементов И, первого коьв 1утатора и регистра соединены с выходом блока управления, группу элементов ИЛИ, распределительный блок и дополнительные коммутаторы. Входы коммутатора соединет с выходами блока адресации, управляющие входы подключены к выходу блока управления, выходы первого и дополнительных коммутаторов соединены соответственно с входом блока .памяти и через группу элементов ИЛИ

подключены к управляющим входам распределительного блока, выходы блока памяти через распределительный блок подключены к счетным входам регистра l Однако при, увеличении точности воспроизведения функции уменьшается величина ступени аппроксимирующей функции, что увеличивает число участ10ков аппроксимации, следовательно растет объем адресной части и чиоло коммутаторов, это увеличивает затраты оборудования, уменьшает надежность и быстродействие.

15

Наиболее (близким к предлагаемому по технической сущности является устройство, содержащее регистр, информационные входа которого соедипены с информационными входами ус20тройства, разрядные выходы регистра соединены с информационными входами адресной комбинационной схемы, управляющий вход которой подключен к входу управления, а выходы соединены

25 с входсши блока памяти, первая группа выходов которого подключена к первой группе входов сумматора, а вторая к соответствующим входам микропрограммного автомата, управляющие

30 выходы которого подключены к управляющим входам регистра комбинационной , сумматора и сдвигового регистра, входы сдвигового рягистра соединены параллельно с информацион.ными входами регистра, а выходы подключены к второй группе входов сумматора, выходы сумматора являются выходами устройства 2.

Недостатком данного устройства является низкое быстродействие. Действительно, быстродействие этого устройства определяется по формуле

в-

где t - время выборки констант сдвига и корректирующих констант ПЗУ (постоянное запоминающее устройство);

г - число сдвигов входной информации ; t - время вглполнения операции

сдвига на один разряд; п - число операций суммирования; Г,- время выполнения одной операции суммирования двух чисел.

При увеличении точности воспроизведения функции и сохранении аппаратурных затрат блока памяти количество сдвигов растет, а следовательно, уменьшается быстродействие воспроизведения функции.

Цель изобретения - повышение быстродействия устройства при сохранении аппаратурных затрат блока памяти.

Поставленная цель достигается тем, что в устройство, содержащее регистр, дешифратор, блок памяти и сумматор, причем информационные входы регистра соединены с входами устройства, первый управляющий вход регистра соединен с входом сброса устройства, выходы разрядов регистра соединены с соответствующими входами дешифратора, выходы КОТОЕЭОГО соединены со входами блока памяти, первая группа выходов которого подключена к первой группе входов сумматора, управляющий вход которого соединен со входом сброса устройства, дополнительно введены m группы элементов И, где га - разрядность коэффициента наклона айпроксимирующей прямой, группа элементов залержки группа элементов ИЛИ и триггер, первый и второй входы которого соединены соответственно со вxoдa ли сброса и запуска устройства, прямой выход триггера соединен со вторым управляющим входом регистра, инверсный выход триггера соединен с управлякнцим входом дешифратора, выходы разрядов регистра соединены с первыми входами соответствующих элементов И каждой группы, вторые входы элементов И каждой группы подключены к соответствующим выходам второй группы выходов блока памяти, выходы элементов И каждой группы

через соответствующие элементы задержки группы соединены с входами соответствующих элементов ИЛИ группы, выходы которых соединены со второй группой входов сумматора, выходы е которого ЯВЛЯЮТСЯ выходами устройства.

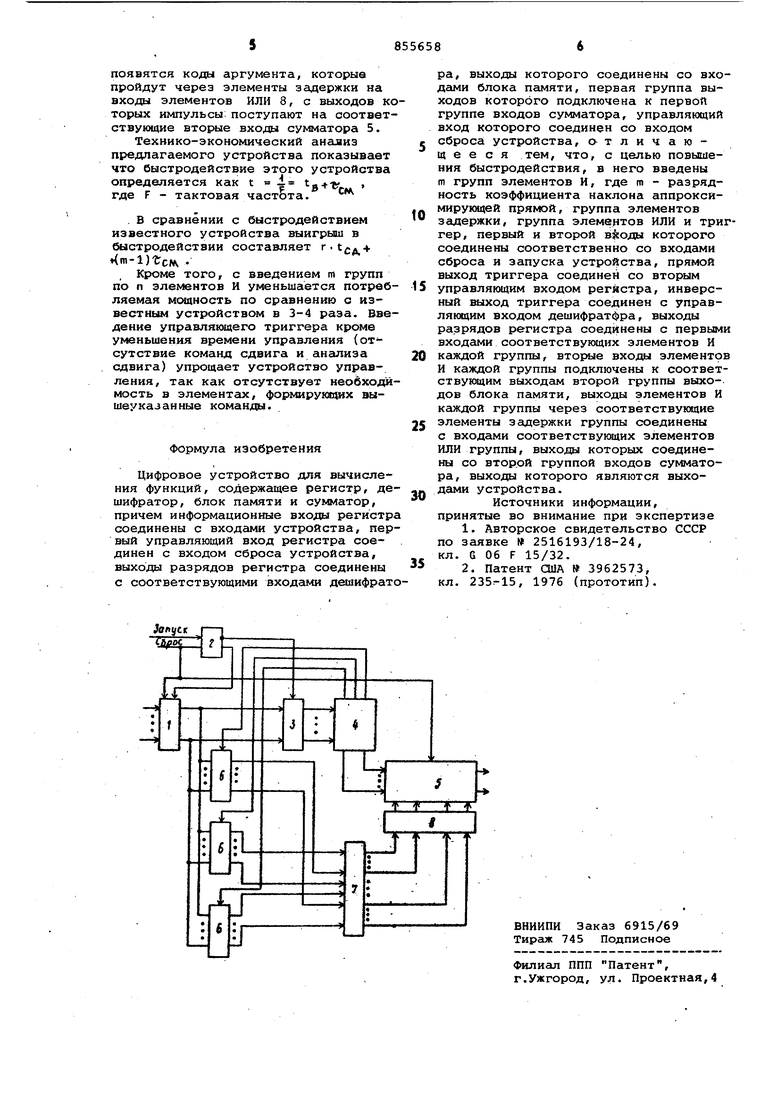

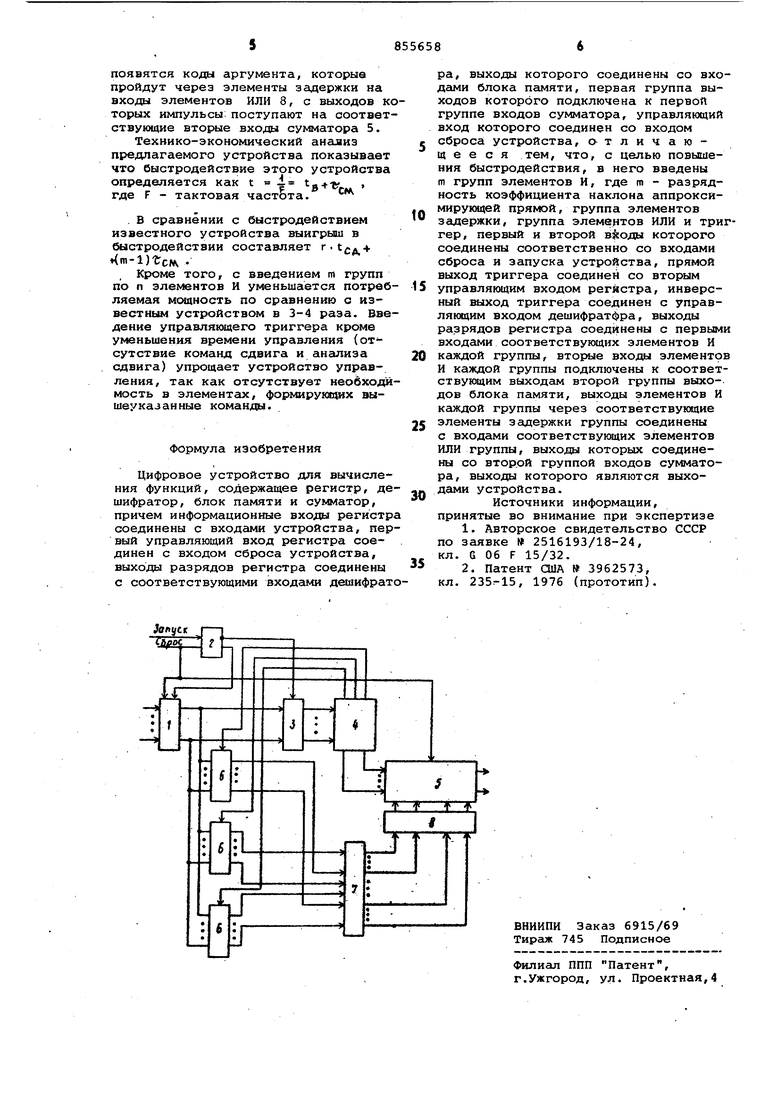

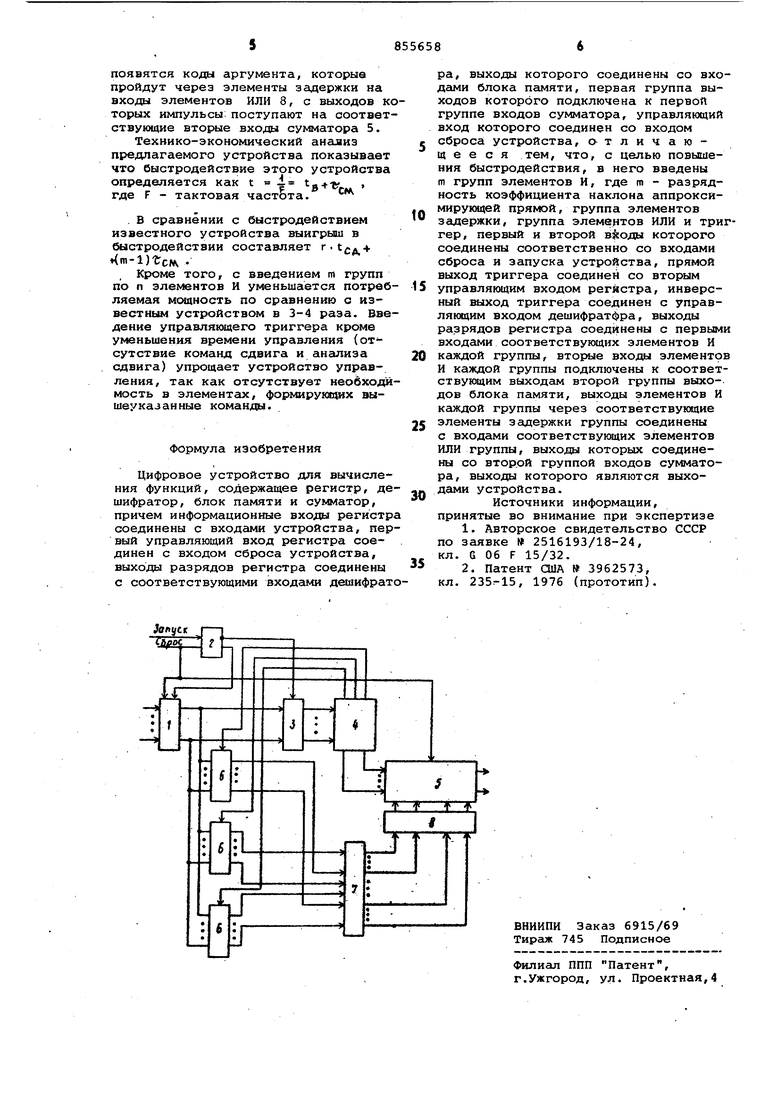

На чертеже представлена блоксхема устройства.

Устройство содержит регистр 1,

триггер 2, дешифратор 3, блок 4 памяти, сумматор 5, СП групп элементов И 6группу элементов 7 задержки и группу элементов ИЛИ 8.

В предлагаемом устройстве значеНИН функций представляются в виде

5 суперпозиции трансформированной в Т-блоках элементов И кодовой последовательности входного аргумента и корректирующих констант. Для участка изменения аргумента (х. х )

0 функция представлена в следуквдем виде(-)-( .)+

где X - аргумент функции, 5 g основание принятой системы

счисления,

f константы преобразования, ° принимающие значения О или 1,

Дj- значение корректирующих Q констант, при 1 i-я

группа элементов И открывается, а при О нет. Количество и знаки выбираются с учетом необходимой точности , произведения функции.Процедура расчета реализуемой функции заключается в том,что определяется значение корректирующей константы Дj и коэффициентаfojr° tiQ: е- наклона прямой на j-ом линейном участке аппроксимации.

Цифровое устройство для вычисления функций работает следующим образом. По входу Сброс устройства импульс устанавливает в исходное состояние регистр 1 и сумматор б. Импульс Запуск поступает на счетный вход триггера и устанавливает на его единичном выходе потенциал, который устанавливав на выхода

Q регистра 1 выходную кодовую последовательность аргумента. Поскольку разрешакяций вход дешифратора 3 открыт нулевым уровнем инверсного входа триггера 2, то под действием кода аргумента на выходе дешифратора 3

сформируется импульс, котогямй пос- тупает на соответствующий вход блока 4 памяти, под действием которого с первой группы выходов блока 4 памяти считывается код константы, который поступает на первую группу входов сумматора 5, а со второй группы выходов блока 4 поступает код константы преобразования на соответствующие управляющие входы группы

5 элементов И б, на выходе которых

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1982 |

|

SU1061136A1 |

| Устройство для вычисления функций | 1977 |

|

SU696472A1 |

| Интерполятор | 1983 |

|

SU1129622A1 |

| Конвейерное устройство для потенцирования массивов двоичных чисел | 1984 |

|

SU1191909A1 |

| Устройство для моделирования конечных автоматов | 1980 |

|

SU955080A1 |

| Устройство для интерполяции | 1984 |

|

SU1171807A1 |

| Устройство для вычисления функции | 1984 |

|

SU1180884A1 |

| Устройство для деления | 1981 |

|

SU987621A1 |

| Устройство для вычисления спектрафуНКций уОлшА | 1979 |

|

SU849224A1 |

| Устройство для вычисления массы нефти и нефтепродуктов в резервуарах | 1983 |

|

SU1117653A1 |

Авторы

Даты

1981-08-15—Публикация

1979-12-07—Подача