Изобретение относится к вычислительной технике и может найти применение в запоминающих устройствах.

Цель изобретения - повышение достоверности контроля и производительности устройства.

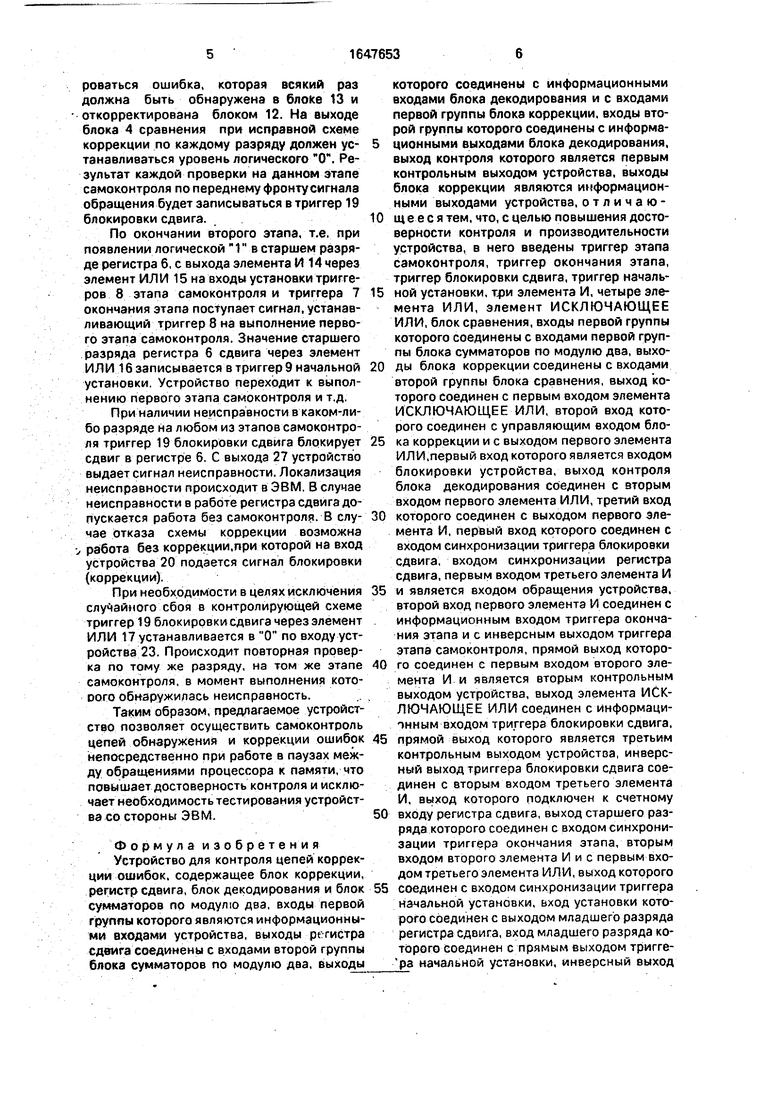

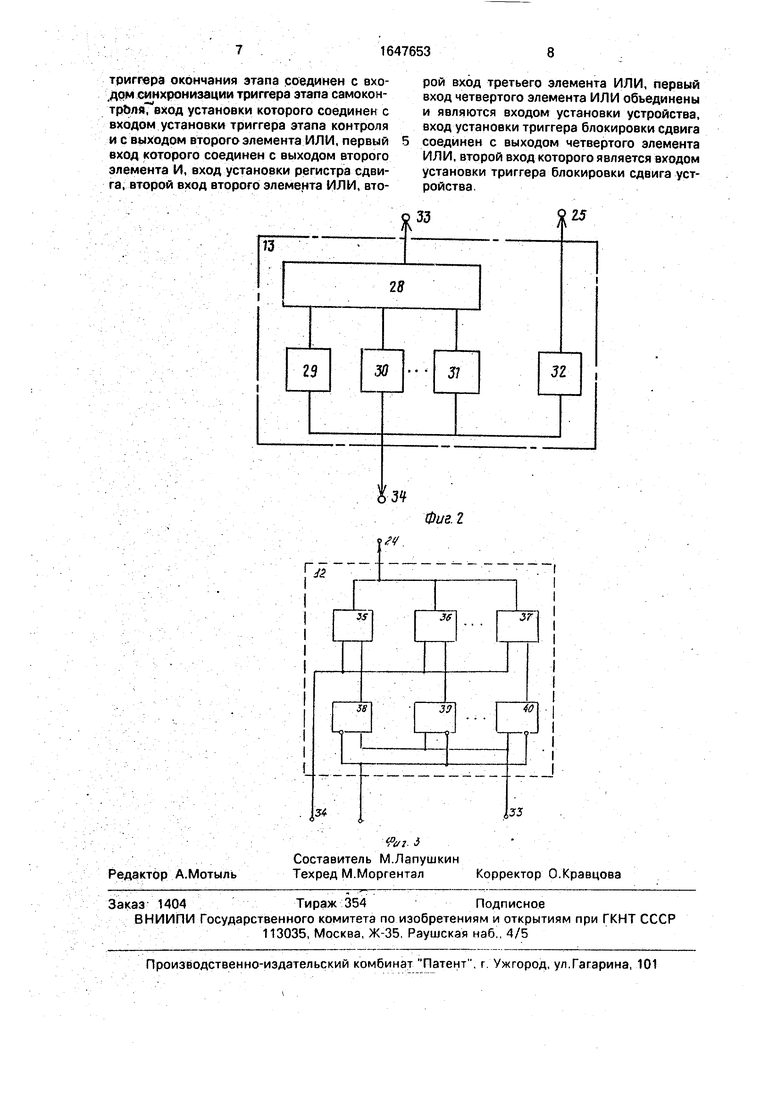

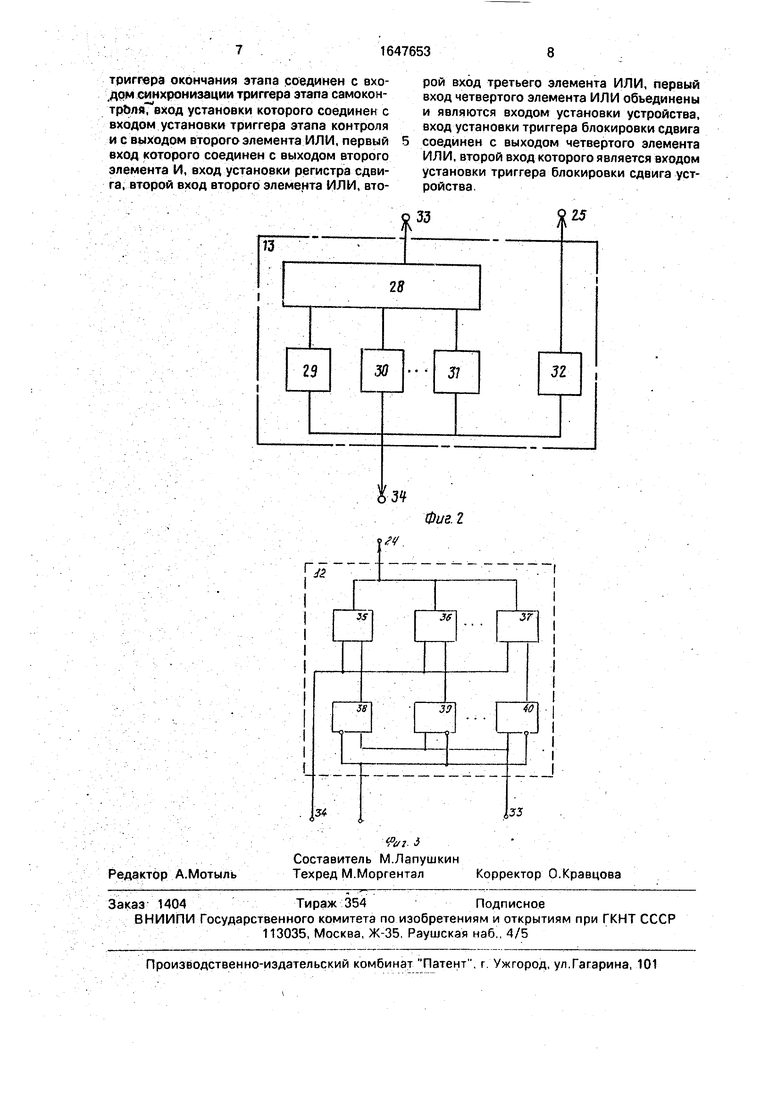

На фиг.1 изображена функциональная схема устройства; на фиг.2 - блок декодирования; на фиг.З - блок коррекции.

Устройство содержит накопитель 1, регистр 2, блок 3 сумматоров по модулю два, блок 4 сравнения, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5, регистр 6 сдвига, триггер 7 окончания этапа, триггер 8 этапа самоконтроля, триггер 9 начальной установки, пери- вый элемент И 10, первый элемент ИЛИ 11, блок 12 коррекции, блох 13 декодирования, второй элемент И 14, второй элемент ИЛИ 15, третий элемент ИЛИ 16, четвертый элемент ИЛИ 17. третий элемент И 18 триггер 19 блокировки сдвига.

Кроме того на фиг.1 обозначены вход 20 блокировки устройства, вход 21 установки устройства, вход 22 обращения устройства, вход 23 установки триггера блокировки сдвига, информационные выходы 24 устройства, первый 25. второй 26, третий 27 контрольные выходы устройства.

Блок 13 декодирования содержит дешифратор 28 синдрома ошибки, группу сумматоров 29 - 32 по модулю два. блок 12 коррекции содержит группу элементов ИСКЛЮЧАЮЩЕЕ ИЛ И 35-37, группу элементов И 38 - 40.

Блок сравнения может быть реализован на основе группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, соединенных между собой для организации поразрядного сравнения входных кодов с последующей шифрацией результатов в значении выходного сигнала блока.

Устройство работает в двух режимах.

Основной режим. По команде обращения из процессора слово, считанное из накопителя 1, поступает в регистр 2, с выхода которого подается на входы первой группы блока 3 сумматоров по модулю два, и далее на входы первой группы блока 12 коррекции и на входы 34 блока 13 декодирования. С выходов блока 13 на входы 33 второй группы блока 12 коррекции подается корректирующий код в случае, если в считываемом из памяти слове обнаружена ошибка или нулевой код в случае отсутствия ошибок. С выходов 24 блока коррекции считываемое слово поступает в процессор. При двойной ошибке (ошибках одновременно в двух разрядах считываемого кода) блок 13 через элемент ИЛИ 11 запрещает коррекцию и выдает в

процессор сигнал, наличия двойной ошибки на выход 25 устройства.

Режим поэтапного самоконтроля. Самоконтроль проводится схемой при непосредственном ее функционировании поэтапно в паузах между обращениями процессора к памяти. Управляющим для схемы самоконтроля служит сигнал обращения на выходе 22 устройства. Начальная установка схемы

0 проводится по сигналу общей установки с входа 21, При этом триггер 8 этапа самоконтроля устанавливает первый этап -контроль регистра б сдвига.

Триггер 9 начальной установки подает

5 уровень логической 1 на вход младшего разряда регистра б сдвига. По заднему фронту сигнала обращения происходит запись логической 1 в младший разряд регистра 6. При этом на сумматоре 3 инвертируется

0 значение младшег разряда кода, снимаемого с регистра 2 числа. Открывается элемент И 10. Сигнал с инверсного выхода триггера 8 через элемент ИЛИ 11 включает блок 12 коррекции и устанавливает уровень

5 логической 1 на входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 5 для сравнения результатов контроля на данном этапе.

Имитированная в младшем разряде кода ошибка при нормальной работе схем ы

0 должна быть обнаружена при сравнении в блоке 4, так как коррекция отключена. Об обнаружении ошибки свидетельствует появление логической 1 на выходе блока 4 сравнения и логического О на выходе эле5 мента 5. С приходом следующего сигнала обращения по его переднему фронту состояние выхода элемента 5 запишется в триггер 19 блокировки сдвига..

Отличаются выходы регистра 6 и блоки0 руется элементом И 10 нулевой выход триггера 8 этапа самоконтроля. Устройство переходит к работе в основном режиме. По заднему фронту сигнала обращения происходит сдвиг логической 1 в регистре 6 и

5 т.д. При появлении логической Г в старшем разряде регистра б устанавливается , триггер 7 окончания этапа, переводящий триггер 8 этапа самоконтроля на второй этап - контроль работы схемы коррекции.

0 Установленный в О инверсный выход триггера 8 включает блок коррекции и устанавливает уровень логического О на втором входе элемента 5 для сравнения результатов поразрядной проверки работо5 способности схемы коррекции. Прямой выход триггера 8 этапа самоконтроля открывает элемент И 14. Аналогично первому этапу во время каждой паузы в обращении регистром 6 будет последовательно по каждому разряду считываемого кода имитироваться ошибка, которая всякий раз должна быть обнаружена в блоке 13 и откорректирована блоком 12. На выходе блока А сравнения при исправной схеме коррекции по каждому разряду должен ус- 5 танавливаться уровень логического О. Результат каждой проверки на данном этапе самоконтроля по переднему фронту сигнала обращения будет записываться в триггер 19 блокировки сдвига.10

По окончании второго этапа, т.е. при появлении логической 1 в старшем разряде регистра 6, с выхода элемента И 14 через элемент ИЛИ 15 на входы установки триггеров 8 этапа самоконтроля и триггера 7 15 окончания этапа поступает сигнал, устанавливающий триггер 8 на выполнение первого этапа самоконтроля. Значение старшего разряда регистра 6 сдвига через элемент ИЛИ 16 записывается в триггер 9 начальной 20 установки. Устройство переходит к выполнению первого этапа самоконтроля и т.д.

При наличии неисправности в каком-либо разряде на любом из этапов самоконтроля триггер 19 блокировки сдвига блокирует 25 сдвиг в регистре 6. С выхода 27 устройство выдает сигнал неисправности. Локализация неисправности происходит в ЭВМ. В случае неисправности в работе регистра сдвига допускается работа без самоконтроля. В слу- 30 чае отказа схемы коррекции возможна работа без коррекции,при которой на вход устройства 20 подается сигнал блокировки (коррекции).

При необходимости в целях исключения 35 случайного сбоя в контролирующей схеме триггер 19 блокировки сдвига через элемент ИЛИ 17 устанавливается в О по входу устройства 23. Происходит повторная проверка по тому же разряду, на том же этапе 40 самоконтроля, в момент выполнения которого обнаружилась неисправность.

Таким образом, предлагаемое устройст- ство позволяет осуществить самоконтроль цепей обнаружения и коррекции ошибок 45 непосредственно при работе в паузах между обращениями процессора к памяти, что повышает достоверность контроля и исключает необходимость тестирования устройства со стороны ЭВМ.50

Формула изобретения Устройство для контроля цепей коррекции ошибок, содержащее блок коррекции, регистр сдвига, блок декодирования и блок 55 сумматоров по модулю два, входы первой группы которого являются информационными входами устройства, выходы pt гистра сдвига соединены с входами второй группы блока сумматоров по модулю два, выходы

которого соединены с информационными входами блока декодирования и с входами первой группы блока коррекции, входы второй группы которого соединены с информационными выходами блока декодирования, выход контроля которого является первым контрольным выходом устройства, выходы блока коррекции являются информационными выходами устройства, отличающееся тем, что, с целью повышения достоверности контроля и производительности устройства, в него введены триггер этапа самоконтроля, триггер окончания этапа, триггер блокировки сдвига, триггер начальной установки, три элемента И, четыре элемента ИЛИ, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, блок сравнения, входы первой группы которого соединены с входами первой группы блока сумматоров по модулю два, выходы блока коррекции соединены с входами второй группы блока сравнения, выход которого соединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с управляющим входом блока коррекции и с выходом первого элемента ИЛИ.первый вход которого является входом блокировки устройства, выход контроля блока декодирования соединен с вторым входом первого элемента ИЛИ, третий вход которого соединен с выходом первого элемента И, первый вход которого соединен с входом синхронизации триггера блокировки сдвига, входом синхронизации регистра сдвига, первым входом третьего элемента И и является входом обращения устройства, второй вход первого элемента И соединен с информационным входом триггера окончания этапа и с инверсным выходом триггера этапа самоконтроля, прямой выход которого соединен с первым входом второго элемента И и является вторым контрольным выходом устройства, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с информационным входом триггера блокировки сдвига, прямой выход которого является третьим контрольным выходом устройства, инверсный выход триггера блокировки сдвига соединен с вторым входом третьего элемента И, выход которого подключен к счетному входу регистра сдвига, выход старшего разряда которого соединен с входом синхронизации триггера окончания этапа, вторым входом второго элемента И и с первым входом третье го элемента ИЛИ, выход которого соединен с входом синхронизации триггера начальной установки, вход установки которого соединен с выходом младшего разряда регистра сдвига, вход младшего разряда которого соединен с прямым выходом тригге- ра начальной установки, инверсный выход

триггера окончания этапа соединен с входом синхронизации триггера этапа самоконтроляГвход установки которого соединен с входом установки триггера этапа контроля и с выходом второго элемента ИЛИ, первый вход которого соединен с выходом второго элемента И, вход установки регистра сдвига, второй вход второго элемента ИЛИ, второй вход третьего элемента ИЛИ, первый вход четвертого элемента ИЛИ объединены и являются входом установки устройства, вход установки триггера блокировки сдвига соединен с выходом четвертого элемента ИЛИ, второй вход которого является входом установки триггера блокировки сдвига устройства

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1059630A1 |

| Устройство для контроля полупроводниковой памяти | 1986 |

|

SU1432612A2 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1661840A1 |

| Устройство для коррекции ошибок внешней памяти | 1987 |

|

SU1501173A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1243032A1 |

| Устройство для сопряжения процессора с памятью | 1982 |

|

SU1059560A1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1167659A1 |

| Запоминающее устройство с самоконтролем | 1989 |

|

SU1718276A1 |

| Устройство для поиска перемежающихся неисправностей | 1986 |

|

SU1381511A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1302435A1 |

Изобретение относится к вычислительной технике и может найти применение в запоминающих устройствах Цель изобретения - повышение достоверности контроля и производительности устройства. Устрой6 37 ство содержит накопитель 1, резистор 2, блок 3 сумматоров по модулю два, блок 4 сравнения, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 5, регистр 6 сдвига, триггер 7 окончания этапа, триггер 8 этапа самоконтролядриггер 9 начальной установки.первый.второй и третий элементы 10,14,18, первый 11. второйдретий и четвертый элементы ИЛИ 15 - 17. блок 12 коррекции, блок 13 декодирования,триггер 19 блокировки сдвига. В устройстве реализован принцип пошагового тестирования цепей коррекции ошибок во время отсутствия обращения из ЭВМ, что позволяет исключить необходимость тестирования этих цепей со стороны ЭВМ Устройство локализует неисправности по функциональным узлам. 3 ил. I 27 6 О XI о (Я GJ Ц3иг1

м

33

Х

28

33

| Запоминающее устройство с контролем цепей обнаружения ошибок | 1985 |

|

SU1367046A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с исправлением ошибок | 1979 |

|

SU920845A1 |

| кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-05-07—Публикация

1988-10-28—Подача