(St) УСТРОЙСТВО для ВЫВОДА ИНФОРМАЦИИ НА ДИСПЛЕЙ

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО РЕГИСТРАЦИИ СТАТИЧЕСКИХ ТЕЛЕВИЗИОННЫХ ИЗОБРАЖЕНИЙ | 1992 |

|

RU2054818C1 |

| Устройство для проверки выполнения последовательности команд микропроцессора | 1984 |

|

SU1247874A1 |

| Устройство для ввода и вывода динамически изменяющейся информации | 1982 |

|

SU1115043A1 |

| Устройство для передачи информации | 1981 |

|

SU1012311A1 |

| Устройство для отладки программно-аппаратных блоков | 1984 |

|

SU1290329A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1985 |

|

SU1354242A1 |

| Устройство для определения координат треков | 1985 |

|

SU1255976A1 |

| Устройство для формирования изображения на экране телевизионного приемника | 1985 |

|

SU1288751A1 |

| Устройство для сопряжения двух ЭВМ с общей памятью | 1985 |

|

SU1256034A1 |

| Устройство для индикации | 1985 |

|

SU1261005A1 |

I

Изобретение относится к автоматике и вычислительной технике и может быть использовано для вывода информации на дисплей.

Известно устройство для вывода -. информации на дисплей, содержащее , последовательно соединенные ЗУ емкостью на кадр изображения, буферное ЗУ емкостью на строку изображения, знакогенератор, а .е узел управления и тактирвания 1,

Недостатком устройства является наличие буферного ЗУ емкостью на строку изображения, что обусловлено высокими требованиями к быстродействию ЗУ емкостью на кадр изображения без специальной организации последнего. Использование буферного ЗУ ем кост.ью на строку изображения приводит к увеличению затрат оборудова НИИ и снижению надежности устройства.

Наиболее близким по технической сущности к предлагаемому является

устройство для вывода информации на дисплей, содержащее синхронизатор, первый выход которого подключен к первому входу преобразователя кодвидеосигнал, выход которого выходом устоойства, второй вход преобразбвателя код-видеосигнал соединен с выходами первого и второго блоков памяти, первые входы которых подключены к выходу

10 регистра, вход которого является первым входом устройства, второй вход которого соединен через первый инвертор с первым входом первого элемента И и. соединен с вторыми входами первого и второго блоков памяти и первым входом второго элемента И, третий вход - с вторыми входами первого и второго.элементов И JJ.

20

Недостатком устройства являetcя низкое быстродействие. .

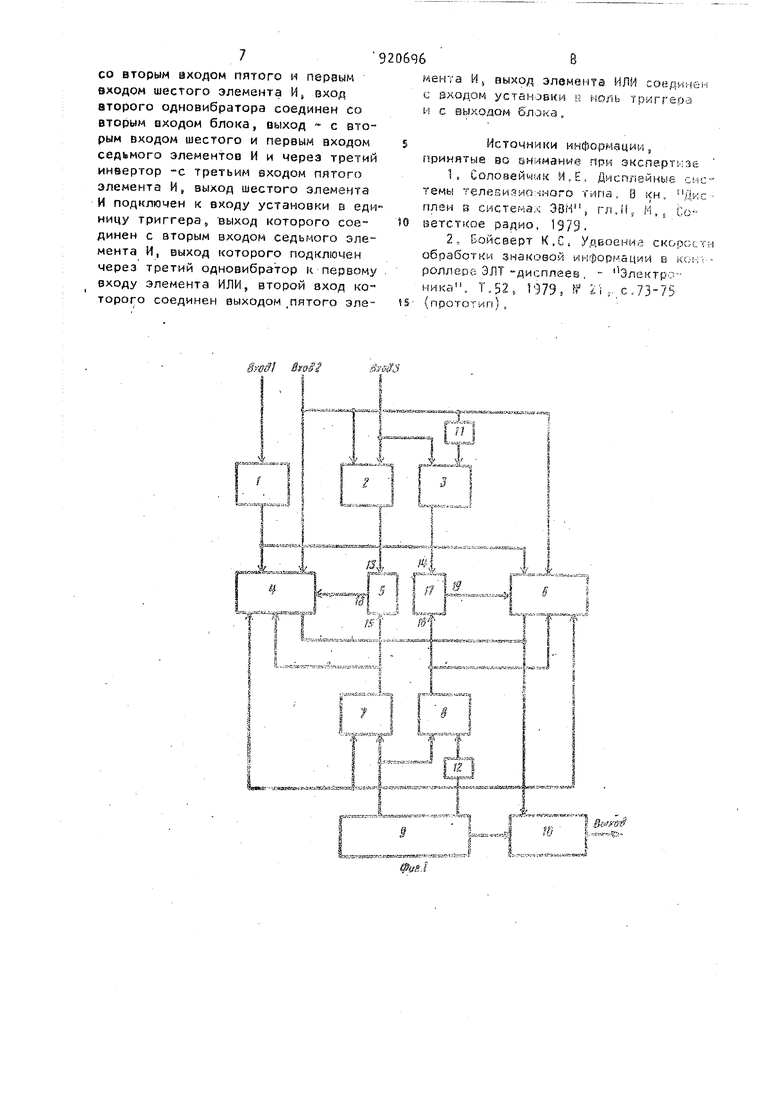

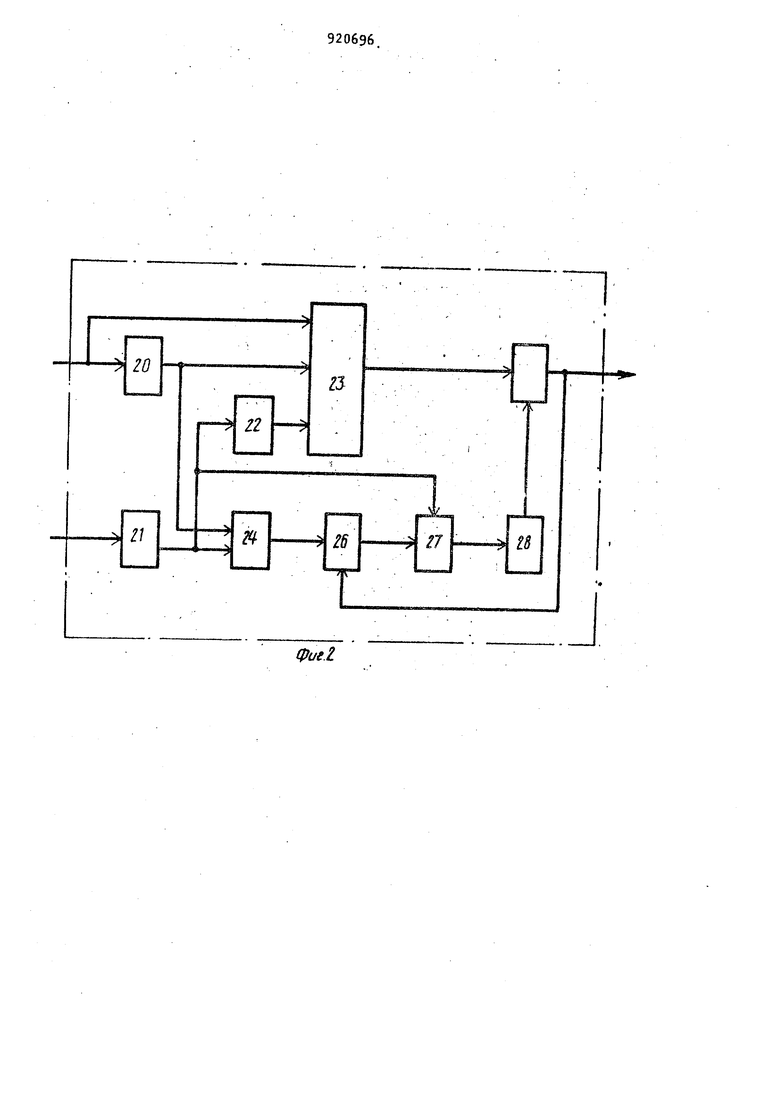

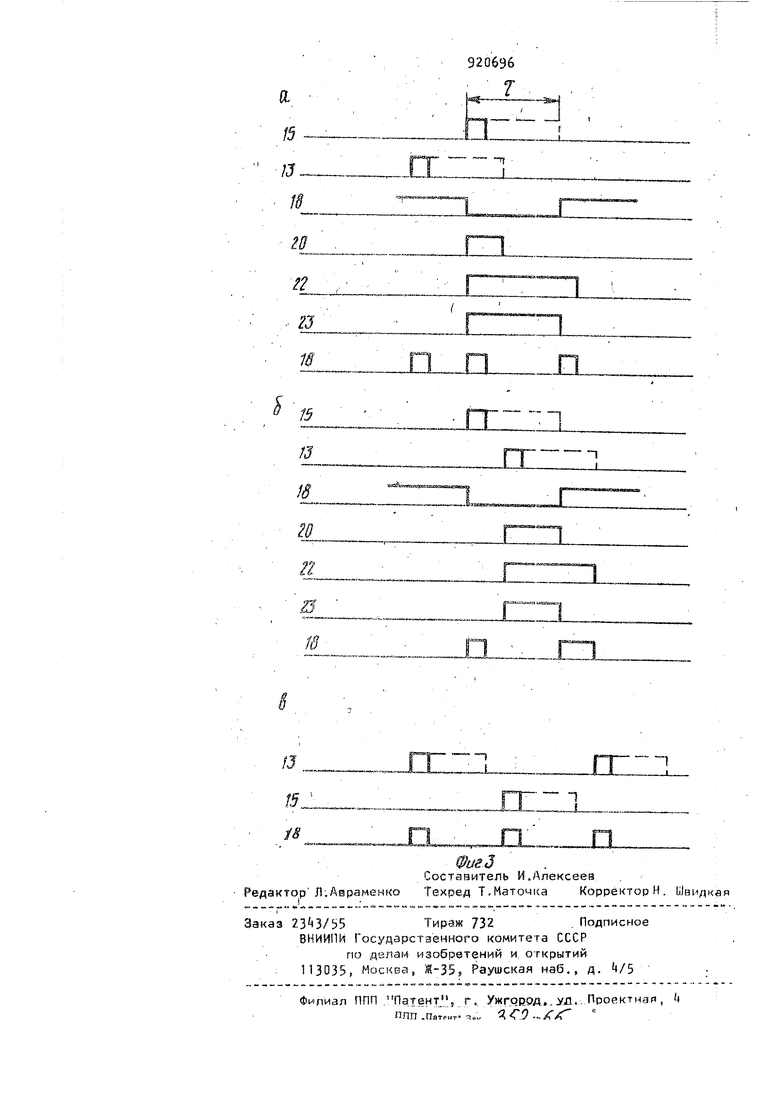

Цель изобретения - повышение бы стродействия устройства. 39 Указанная цель достигается тем, Цто а устройство введены второй ин ертор,. третий ц четвертый элементы 14 и первый и второй блоки управления , входы первого и второго блоков управления подключены к выходам первого, второго, третьего и четвертого элементов И соответственно, выходы к третьим входам соответственно первого и второго блоков памяти, четвер ТЫе входы которых соединены с выхода мИ третьего и четвертого элементов И соответственно, пятые входы - с первым входом третьего элемента И И;с вторым выходом синхронизатора.третий выход которого соединен с. вторым входом третьего и с первым входом четвертого элементов И, второй выход синхронизатора подключен через второй инвертор к второму входу четвертого элемента И, а также тем, что каждый блок управления памятью содержит элемент ИЛИ, первый, второй и третий одновибраторы, гер, третий инвертор и пятый, шестой и седьмой элементы И., вход первого одновибратора соединен с первым входом блока и первым входом пятого эле мента И, выход - со вторым входом пятого и первым входом шестого, элемента И, вход второго одновибратора соединен со вторым входом блока, выход - с вторым входом шестого и первым входом седьмого элементов И а через третий инвертор - .с третьим .входом пятого элемента И, выход шестого элемента И подключен к входуустановки в единицу триггера, выход .которого соединен с вторым входом седьмого элемента И, выход которого подключен через третий одновибратор к первому входу элемента ИЛИ, второй вход которого соединен с выходом элемента И, выход элемента ИЛИ соединен с входом установки е ноль триггера и с выходом блока. На фиг,1 изображена блок-схема устройства для вывода информации на дисплей; на фиг.2 структура блока управления памятью; на фиг.З - временные диаграммы процесса согласования чтения и записи. На фиг.1-3 оЬозиачено: регистр 1, первый и второй элементы И 2 и 3 первый блок памяти , первый блок управления 5, второй блок памяти 6, третий и четвертый элементы И 7 и 8 синхронизатор 3, преобразователь кода В видеосигнал 10, первый и второй инверторы 11 и 12, .первые 13 и 44 и вторые 15 и 16 входы блока управления, второй блок управления 17,выходы первого и второго блоков управления блоков управления 18 и 19, первый и второй одновибраторы 20 и 21, третий инвертор 22, пятый и шестой элементы И 23 и 2, элементы ИЛИ 25, триггер 26, седьмой элемент И 27, третий одновибратор 28. Устройство работает следующим образом. 8 запоминающем устройстве (ЗУ), образованном блоками памяти и 6, хранится кодовый экаиаалент изсбражёния (КдЭИ), который преобразуется в видеосигнал для отображения его на экране телевизионного индикатора. Синхронизатор 9 управляет считыванием информации из ЗУ, Коды символовсчитываются из. блоков памяти и 6 синхронно с движением луча вдоль строки растра. Младший разряд адреса чтения, который формирует синхронизатор У,таким образом управляет элементами И 7 и 8, что информация попеременно считывается, то из блока памяти k, то из блока памяти 6. Это позволяет вдвое уменьшить частоту обращений при чтеНИИ к каждому из блоков Памяти 4 и 6 без изменения объема ЗУ и результирующей частоты, обращения, Одновременно с чтением информации необходимо осуществлять асинхронную запись КдЭИ в блоки памяти. Младший разряд адреса записи управляет элементами И 2 и 3 таким образом, что информация записывается попеременно, то в блок памяти 4, то в блок памяти 6, Например все слова, имеющие четный адрес, записываются в блок памяти 7, з иечетный - в блок памяти 6. Для обеспечения одновременности записи и чтения -используются блоки управления 5 и 17. Этот блок разрешает конфликт в том случае, если в одном из,блоков памяти необходимо одновременно и за писать и считать слово КдЭИ. Блок управления 5 с учетом того, что для исключения мельканий на экране дисплея при обращении к блоку памяти, приоритет необходимо отдавать считываниюi работает следующим образом.(Блок управления 17 выполнен образом. (Bj идентично. 5 Импульсы записи и чтения поступа ют соответственно на одновибраторы и 21, которые формируют из этих импульсов импульсы большей длительнос ти Т .. Причем % выбирается из условия t t-oTTip , где toTTJp минимал но возможный период обращения к бло памяти. В случае, приведенном на фиг.За, запрос на чтение приходит тогда, ко да еще не закончилась запись. Код, который должен быть записан в f(a fный момент хранится в регистре 1 до прихода разрешения на запись Разре шение на запись формируется после такта чтения через время it. . Задерж ка записи осуществляется следующим образом. Сигнал с выхода инвертора 22 бло кирует Запись, запирая элемент И 23 по информационному входу 16. В То же время сигнал с выхода элемента И 2 переводит триггер 2Ь в единичное состояние. Это позволяет импуль су с выхода одновибратора 21 череа элемент И 27 воздействовать на вход одновибратора 28. Последний формиру импульсы записи по окончании процесса считывания. По этому импульсу код который хранится в регистре 1 и не записан вследствие того, что процесс записи прерван чтением, записывается в блок памяти. Необходимо отметить, что при некотором опережении записи может формироваться неполноценный импульс записи. При этом информация может записываться , однако для надежной записи, как видно из фиг.За, формируется полноценный импульс записи.На фиг.36 показана ситуация, когда обращение на запись приходит до окончания считывания информации из данного блока памяти. В этом случае задержка записи peaлизована аналогично. На фиг.Зв приведен случай, когда запись и считывание разнесены во времени и конфликтной ситуации нет. В этом случае одновременность записи и считывания обеспечивается без участия блока управления 5. Полезный эффект изобретения по сравнению с известными устройствами заключается в повышении скорости обработки знаковой информации Полезный эффект изобретения достигается за счет использования сущест96венных отличительных признаков предложения путем обеспечения возможности одновременно записывать и считывать информацию при обращении к устройству. Формула изобретения 1 .Устройство для вывода информации на дисплей, содержащее синхронизатор, первый выход которого подключен к первому входу преобразователя код-видеосигнал, выход которого является выходом устройства, второй вход пре(Образователя код-видеосигнал соединен с выходом первого и второго блоков памяти, первые входы которых подключены к выходу регистра, вход которого подключен к первому входу устройства, второй вход которого соединен через первый инвертор с первым входом первого элемента И и сое- динен с вторыми входами первого и второго блоков памяти и первым входом второго элемента И, третий вход с вторыми входами первого и второго элементов И,отличающееся тем, что, с целью повышения быстродействия устройства, в него введены второй инвертор, третий и четвертый элементы И и первый и второй блоки управления, первые и вторые входы первого и второго блоков управления подключены к выходам первого, второго, -третьего и четвертого элементов И соответственно, выходы к третьим входам первого и второго блоков памяти соответственно, четвертые входы которых соединены с выходами третьего и четвертого элементов И соответственно, пятые входы с первым входом третьего элемента И и с вторым выходом синхронизатора, третий выход которого соединен с вторым входом третьегои с первым входом четвертого элементов И, второй выход синхронизатора подключен через второй инвертор к второму входу четвертого элемента И. 2. Устройство ПОП.1, о т лич а ю щ е е с я тем, что каждый блок управления памятью содержит элемент ИЛИ первый, вторбй и третий одновибраторы, триггер, третий инвертор и пятый, шестой и седьмой элементы И, ход первого одновибратора соединен первым входом блока и с первым ходом пятого элемента И. выход со вторым эходом пятого и первым входом шестого элемента И вход второго одиовибратора соединен со вторым входом блока, выход - с вторым входом шестого и первым входом седьмого элементов И и через третий инвертор -с третьим входом пятого элемента И, выход шестого элемента И подключен к входу установки в еди ницу триггера, выход которого соединен с вторым входом седьмого элемента И, выход которого подключен через третий одновибратор к первому входу элемента ИЛИ, второй вход которого соединен выходом пятого эле§гкП Sioii

:, ВЫХОД эламента ИЛИ соединен с входом установки s ноль триггера и с выходом блока. Источники информации. принятые во йнимаиие при экспертизе К Соловейчых И,Е, Дисплейные системы телезия /10:-«ного типа. В кн. Дис плен в системах ЭВМ, гл.П,, Н,, СоЕзетсткое радио, 1979. 2, Бойсверт К,С, УдЕоеииа ск&рост;обработки знаковой информации в кчл-; роллере ЭЛТ дисплеев . - Электроника, Т.52. 1979, г ,.,сЛЗ-75 (прототип),

1

:.. j

16 П

,,„ ; .

„„„.„„....„„.„jnzzi

C.±II -

Авторы

Даты

1982-04-15—Публикация

1980-07-18—Подача