(54) РЕГИСТР

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сдвига информации | 1979 |

|

SU1005034A1 |

| АССОЦИАТИВНЫЙ ПРОЦЕССОР | 1988 |

|

SU1521118A1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ПАРАЛЛЕЛЬНОГО | 1973 |

|

SU362295A1 |

| Устройство для сдвига | 1975 |

|

SU723570A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Вычислительное устройство | 1975 |

|

SU705478A1 |

| Регистр сдвига | 1975 |

|

SU666583A1 |

| Устройство для умножения с накоплением комплексных чисел | 1988 |

|

SU1587230A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

t

ИзоЕ тение относится к )й вычиспигепьной технике и моявет явиться составной частью устройств ЭВМ.

Известен регистр, в котором для выполнения оптации логнческсжо сложения и логическсяо умножения требуются отдельные двухвходовые погнческне элементы типа И в каждом разряде 1.

Однако это приводит к неэкономвяиому использованию оборудования.

Наиболее близким к предлагаемому по технической сущности является регвстр, содержащий статические триггеры со схемами парафазной записи из двух элементов И и первого элемента НЕ, который по входу соединен с первым входом вого элемента И, а по выходу - с первым входом второго элемента И, выход первого элемента И соединен с единичным входом триггера, а выход второго элемента И соединен с нулевым входом триггера, причем, второй вход второго элемента И соединен с выходом первого элемента ИЛИ, первый вход которого соединен с

шиной установки регистра в ноль, а вторсА вход - с шиной команды записи. В известном регистре совмещено вьтолнение элементарных операций парафазной.записи и установки регистра в ноль на отих и тех же лсйгнческих элементах схемы управления 22.

Недостатком известного регистра являются его ограниченные функциональные возмонщости, например, he выполняются

to операции типа логического сложения в логического умножения.

Цель изобретения - расширение фувкцисмальных возможностей регистра за счег выполнения операций логического слшкеыкя

tS и умножения и его упрощение.

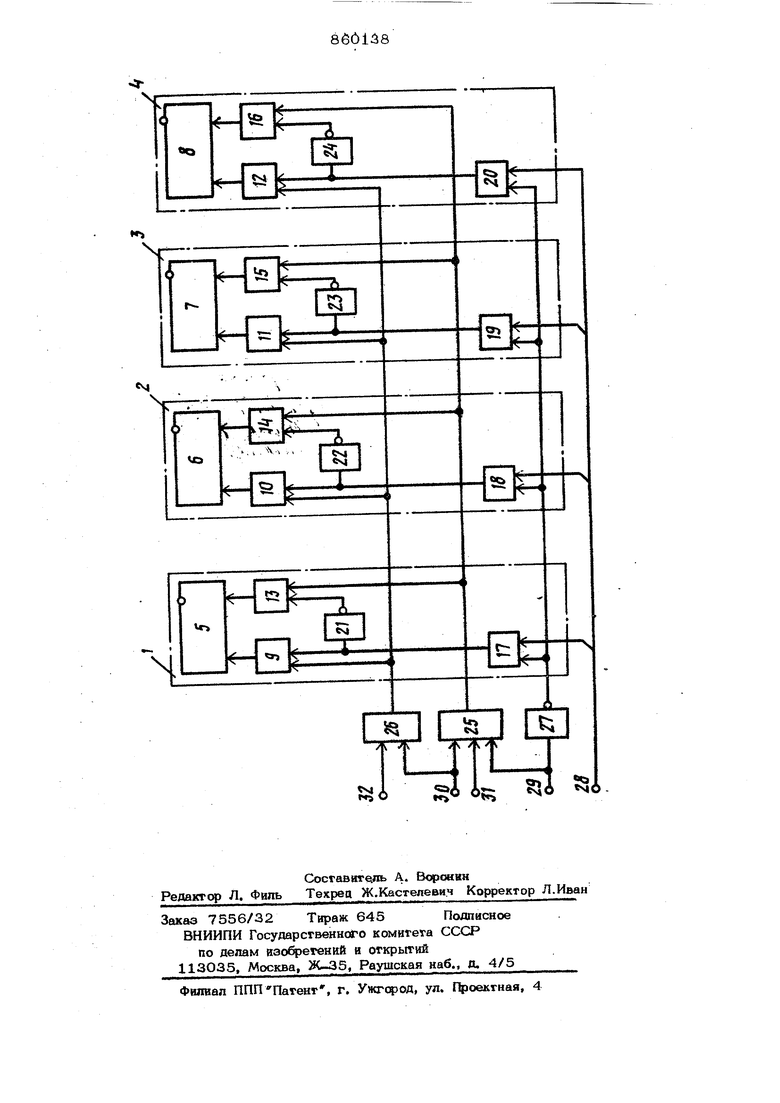

Поставленная цель достигается твм,что в регистр, содержащей перЬый элемент ИЛИ и ячейка памяти, каждая из которых выполнена на статическом триггере, пер20вом и втором элементах И в первом эле« менте НЕ, вход которого соединен с ОДним из входов первого элемента И, а вы ход - с одним из входов второго эле38мента И, выходы элементов И подключены к входам сгагического триггера, Другие вхо ды вгорьк элементов И ячеек памяги соединены с выходом первого эпеменга ИЛИ один из входов которого соединен с шино управления записью, другой вход первого элемента ИЛИ подключен к шине установки О, и числовую шину, введены агорой элемент ИЛИ, элемент НЕ и шину управления логическим сложением и умножением, а в каждую ячейку памяти введен третий элемент И, выход которого подклю чен ко входу первого элемента НЕ, один из входов третьего элемента И каждой ячейки памяти соединен с выходом второго элемента НЕ, другой вход третьего элемента И каждой Ячейки памяти подсоединен к числовой Шине;вход второго элемента НЕ соединен с шиной установки О третий вход первого элемента ИЛИ соединен с шиной управления логическим умножением, входы второго элемента ИЛИ подключены соответственно к шине управления записью И шине управления логическим сложением, а выходы второго элемента ИЛИ Подсоединены к другому входу первого элемента И каждой ячейки памяти. На чертеже изображена функциональная схема предлагаемого регистра. Регистр содержит ячейки 1-4 памяти (показаны только четыре ячейки памяти регистра), которые выполнены на статических триггерах 5-8, первых элементах И 9-12, вторых элементах И 13-16, третьих элементах И 17-20 и первых элементах НЕ 21-24, элементы ИЛИ 25 26, второй элемент НЕ 27, числовую шину 28, шину 29 установки О, шину ЙО управления записью и шины управлени Логическим сложением и умножением 31 И 32. Как видно из чертежа, в регистре отсутствуют поразрядные логические элемен ты типа И-ИЛИ для выполнения операций Логического сложения и логического умно жения. В тфедлагаемом регистре выпопнение этих операций совмещено с выполнени ем элементарных операций парафазной записи и установки в ноль, при этом тригге ры не имеют отдельного дополнительного входа установки в ноль. Регистр функцисдаирует следуюшим образом. Элементарная операция установки регистра в ноль осуществляется подачей сигнала на шину 29, в результате чего элементы И 17-2О закрьшаются и формируют на своем вькоде сигнал логиче- 8 ского нуля, через элементы НЕ 21-24 записывается в триггеры 5-8, так как команда установки в ноль через элемент ИЛИ 25 поступает на вторые входы элементов И 13-16. Операция парафазной записи инфс мации осуществляется подачей команды записи на шику 30, которая через элементы ИЛИ 25 и 26 поступает на элементы И 9 и 13, При этом элемент НЕ 27 формирует разрешающий потенциал для элементов И 17-20, поскольку на его вход по шине 29 установки О сигнал не поступает. При выполнении операции логического сложения необходимо предусмотреть поразрядную запись только единичной инфс)мации, а пqpaзpядаyю нулевую информацию записывать не нужно. Например, предположим, что в регистре находится числа Х, ООН, а по числовой шине 28 через элементы И 17-2О поступает число Xi2 HOI. После выполнения операции логического сложения ( V) должно получигься в регистре число Xj-1111, т.е. ,VX,j 0011V1101 1111, В предлагаемом схемном решении запись нуля в третий разряд не происходит, так как сигнал логического сложения по шине 32 через элемент ИЛИ 26 поступает только на элементы И 9-12 единичных входов триггеров 5-8. При выполнении операции логического умножения необходимо предусмотреть поразрядную запись только нулевой информации, а поразрядную единичную информацию записывать не нужно. Например, если , а , то после выполнения логического умножения ( Д) должно получиться число Xj 0001, т.е. Хз Х Л Х ОО11Л11О1 ОО01. При формировании числа Xj первую, вторую и четвертую ячейки памяги (разряды) у числа Х должны остаться без изменения, а третий разряд необходимо переключить в состояние, поскольку у Xj третий разряд равен нулю. Операция логического умножения выполняется подачей сигнала на шину 31, котсфая через элемент ИЛИ 25 поступает на элементы И 13-16 нулевьк входов триггеров 5-8 и устанавливает их в Ноль, если в соответствующем разряде числа Хл имеется ноль.. При вьтопнении операции лсягического сложения и умножения элемент НЕ 27 формирует разрешающий потенциал для элементов И 17-2О. Расширение функциональньрс возможностей устройства осуществляется дополнительным выполнением двух логических oneраций, а именно: логического сложения в логического умножения. В известных реги страх на выполнение одной операции типа логическся о сложения и умножения используется один двухвходовой элемент И, объединенный по выходу элементом ИЛИ, т.е. на одну операцию требуется 1,5 двухвходового элемента И, .а на две операцив требуется 3 двухвходовых элемента типа И-ИЛИ. В предлагаемом регистре операции логического сложения к умножения реализованы на элементах И схемы парафазной записи, т.е. для их реалваадвв в каждом разряде не требуются дсюолнитель ные элементы, и экономия оборудования равняется 3-м элемв{там И на один разряд. Однако для совмещенного выполн ия четьфех операций: параллельной записи, установки в ноль, логическсмго сложения и логического умножения требуется один дополнительный двухвходовый элемент И, поэтому общая экономия оборудования равна двум двухвходовым элементам И на один разряд регистра. Формула изобретения Регистр, содержащий первый элемент ИЛИ и ячейки памяти, каждая из которых выполнена на статическом триггере, первом и втором элементах И и первом элементе НЕ, вход которого соединен с из входов первото элемента И, а выход - с одним из входов второго элемента И, выходы элементов И подключены ко входам статического триггера, другие вхо ды элементов И ячеек памяти соединены с выходми первого элемента ИЛИ, один из входов которого соединен с шиной управл 1ия записью, другой вход первого элемента ИЛИ подключен к шине установка О, и числовую шину, отличающийся тем, что, с целью расширения функциональных возможностей регистра за счет выпо1шения оптации логического сложения и умножения и его утфощевия, в него введены второй элемент ИЛИ, второй элемент НЕ и шины управления логическим сложением и умножением, а в каждую ячейку памяти введен третий элемент И, вьосод которого подключен ко входу первого элемента НЕ, один из входов третьего элемента И ячейки памяти соединен с выходом BTcfioro элемента НЕ, другой . вход третьего элемента И каждой ячейки памяти подсоединен к числовой шине, axbff элемента НЕ соединен с шиной установки О, третий вход первого элемента ИЛИ соединен с шин(А управления логическим умножением, входы второго ИЛИ подключены соответств(Жно к шине управления записью в шине управления логическим сложением, а выход второго элемента ИЛИ подсоединен к другому входу элемента И каждой ячейки памяти. Источники информации, принятые во внимание при экспертвзе 1.Папернов А. А. Лсгические осяооы ЦВТ. М., Ck eTCKoe радио , 1972, с. 265. 2.Авторское свидетельство СССР DO заявке № 2176О32/18-24 кл.й 11 С 19/ОО, 1975 (прототва).

Авторы

Даты

1981-08-30—Публикация

1979-10-09—Подача