(54) ПРОГРАММИРУЕМОЕ ЛОгаЧЕСКОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемая логическая матрица | 1976 |

|

SU739651A1 |

| Оперативное запоминающее устройство на мдп-транзисторах | 1974 |

|

SU744726A1 |

| Программируемое логическое устройство | 1980 |

|

SU982092A1 |

| ПОЛУПРОВОДНИКОВОЕ УСТРОЙСТВО НЕРАЗРУШАЕМОЙ ПАМЯТИ | 1992 |

|

RU2097842C1 |

| Программируемая запоминающая матрица | 1981 |

|

SU1003144A1 |

| Генератор импульсов | 1979 |

|

SU834841A1 |

| Двухтактный сдвигающий регистр | 1968 |

|

SU736172A1 |

| Усилитель считывания на моп-транзисторах /его варианты/ | 1980 |

|

SU883968A1 |

| Компаратор | 1979 |

|

SU843179A1 |

| Устройство для выборки адресов из блоков памяти | 1976 |

|

SU744722A1 |

t

Изобретение относится к вычиспитеп :рой технике.

Известны программируемые логические устройства в интегральном исполнении, состоящие из двух п6следователь но включенных матриц, первая из которьк является дешифратором входных слов, а вторая - полем памяти, хранящим выходные слова. Каждая из матриц представляет собой набор вентилей НЕ-ИЛИГ11,

Недостаток таких устройств -, наличие значительного числа общих шин.

Наиболее близким техническим .решением к изобретению является устройств во, состоящее из двух последовательно включенных матриц, каждая из которых содержит нагрузочные МОП-1ранзисторы, подключенные между шиной питания и соответствующей.выходной шиной и столбцы, образованные МОП-транзисторами, затворы которых подключены к соответ- ствутощей входной шине, истоки - к общей шине, стоки МОП-транзисторов каждого столбца первой матрицы и стоки

МОП-транзисторов первого и последнего столбца второй матрицы - к соо-рветствующей выходной шине, стоки МОПтранзисторов остальных соседних столбцов второй матрицы подключены к одной соответствующей выходной шинеГ21,

Однако известное устройство обладает наличием значительного числа общих шин, что приводит к усложнению устройства, увеличению занимаемой площади, по10вышенлю стоимости.

Цель изобретения - упрощение уст ройства, уменьшение зан шаемой площади и снижение стоимости.

Поставленная цель достигается

15 тем, что в программируемом логическом устройстве, cocTosnaeM из двух последовательно включенных матриц, каждая из которых содержит нагрузочные МОПтранзисторы, подключенные между шиной

20 питания и соответствующей выходной шиной и столбцы, образованные МОП-транзисторами, затворы которых подключены к соответствуквдей входной шине, истоки МОП-тронзисторов первого столбца первой матрицы и истоки МОП-транзисторов каждого столбца второй матрицы - к обшей шине, стоки МОП-транзисторов каждого столбца первой матрицы и первого и последнего столбца второй матрицы подключены к соответствующей вы ходной шине, а стоки МОП-транзисторов остальных каждых двух соседних столбдов второй матрицы подключены к одной соогветствукядей выходной шине, в каждом из столбцов первой матрицы, кроме первого i истоки МОП-транзисторов подключены к стокам МОП-транзисторов предыдущего столбца этой мат

рицы.

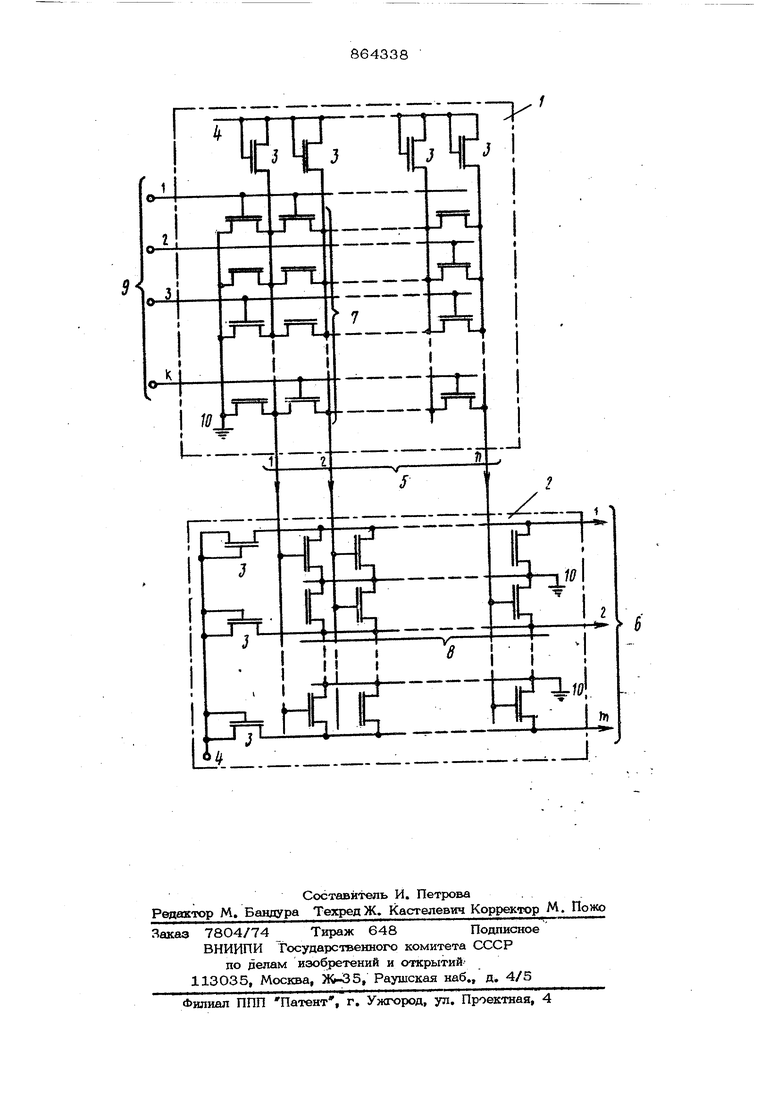

На чертеже представлена принципиальная электрическая схема программируемого логического устройства,

Устройство содержит две последовательно включенные .матрицы 1 и 2, каждая из которых содержит нагрузочные МОП- транзисторы 3, подключенные между шинами 4 питания и одной из выходных шин 5 первой матрицы и, соответственно, ЭДНОЙ из выходных шин 6 второй матр1:цы , и столбцы 7 к 8 , образованные МОП-транзисторами 3,, затворы которых в матрице I под ключены , соответственно, у первых МОП-транзисторов 3 столбцов

7к первой из входных шин 9 а в матрице 2 затворы МОП-транзисторов 3 каждого столбца 8 подключень, соответственно, к одной из шин 5, которые являются выходными для матрицы 1 и входными для матрицы 2. Истоки МОПтранзисторов 3 первого из столбцов 7 матрицы 1 и истоки МОП-транзисторов

3 каждого из столб цов 8 подключень к обшим Ш1шам 10, стоки МОП-транзисторов 3 каждого столбца 7 матрицы 1 и первого и последнего из столбцов

8матрицы 2 подключены , соответственно, к одной из выходных шин

5 или 6, а строки остальных кагвдых дв соседних столбцов 8 подключены, соответственно, к одной из вьпсодных шин 6. В каждом из столбцов 7, кроме первого., истоки МОП-транзисторов 3 подключены к стокам МОП-транзисто-н ров 3 предьщущего столбца.

Устройство работает следующим образом.

На входные шины 9 матрицы 1 поступает определенный набор двоичных СИ налов, который выбирает один из столбцов 7 МОП-транзисторов 3, т.е. запи-

поскопъку указанные выходные подключаются к обшим шинам 4. В тех же столбцах, где отсутствуют связи затворов МОП-транзисторов 3 с входной шиной, происхо,ит появление высокого уровня потенциала на соответствуюших выходных шинах 6, благодаря тому, что нагрузочные МОП-транзисторы 3 находятся в открытом состоянии и обес5 печивают поступление высокого уровня потенциала от шины питания 4 на соответствующую выходную шину 6.

На всех выходных шинах 5, расположенных дальше от обшей шины 10, чем

0 выбранная входами сигналом шина, так же появляется высокий потенциал. Поэтому для правильной работы устройства необходимо , чтобы слова, выбираемые из матрицы 2 соседними выходны5 МИ шж1ами 5, удовлетворяли определен- ному условию поглошения. Оно закЛкжается в том, что слово, выбираемое первой из шин Я (т. е. соседней с обшей шиной 10) поглощает все другие, ело-

Q во, выбираемое пторым из шин 5, поглощает вес: . последующие (кроме первого) и т.д.

Заметим, что удсвгетворить указанному условию в случае реальных дискретных устройств достаточно просто,для этого следует лишь расположить слова, хранимые в матрице 2, в надлежащем порядке,: При необходимости выходные, слова могут быть также разбиты на соответствующие группы, внутри каждой из

которых указа1« ый порядок соблюдается.

Предлагаемое устройство позволяет иметь лишь одну общую шину, приходящуюся на п столбцов первой матрицы, 55 Это упрощает схему устройства, и, при .значениях 10- (которые являются характерными /для современного уровня развития интетральной технологии). jjaoT все транзисторы этого столбца. Нагрузочные МОП-транзисторы 3, находясь в открытом состоянии, обеспечивают прохождение высокого потенциала от шины питания 4 к одной из выходных шин 5. При этом связь указан ной выходной шины с общей шиной 10 отсутствует , поскольку МОП-транзисторы 3 заперты. Палее этот сигнал поступает на одну из входных шин матрицы 2, попадая на затворы соответствук ших МОП-транзисторов 3 в столбцах 8, этот сигнал отпирает их и приводит к появлению низкого уровня потенциала на соответствуюших выходных шинах 6,

сокращает площадь интегральной схемы примерно JB 1,5 раза, что снижает ее стоимость.

Формула изобретения

П рограммируемое логическое устройство, состоящее из двух последовател но включенных матриц, каждая из которых содержит нагрузочные МОП-транзисторы, подключенные между шгшой ni тания и соответствующей выходной шиной и столбцы, образованные МОП-транзисторами, затворы которых подключены к соответствующей входной ипше, истоки МОП-транзисторов первого столбца первой матрицы и истоки МОП-транзис -торов каждого столбца второй матрИ11Ы к -общей шине, стоки МОП-транзисторов каждого столбца первой матрицы и первого и последнего столбца второй матри643386

«ы подключены ь. соответствующей выкодной шине, а стоки МОП-транзисторов остальных каждых двух соседних столбцов второй матрицы подключены к од5 ной соответствующей выходной щине, о т личаюшееся тем, что с целью упрощения устройства, уменьшения зёнимаемой площади и снижения стоимости, в каждом из столбцов первой матрицы

10 кроме первого, истоки МОП-транзисторов подключены к стокам МОП-трэнзисторов предыдущего столбца этой матрицы.

Источники информации,

(5 принятые во внимание при экспертизе

20 с. 22-26.

Авторы

Даты

1981-09-15—Публикация

1979-12-06—Подача