(54) СГЛАЖИВАЮЩИЙ ФИЛЬТР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой анализатор энергетического спектра | 1978 |

|

SU769443A1 |

| Адаптивное устройство для передачи информации | 1984 |

|

SU1244693A1 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2010 |

|

RU2450445C2 |

| УСТРОЙСТВО КОМПЕНСАЦИИ СТРУКТУРНЫХ ПОМЕХ | 2013 |

|

RU2534221C1 |

| Дифференцирующе-сглаживающее устройство | 1975 |

|

SU610115A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА КАНАЛА СВЯЗИ | 2002 |

|

RU2216865C1 |

| Адаптивный цифровой корректор | 1979 |

|

SU794734A1 |

| Сглаживающее устройство | 1984 |

|

SU1265797A1 |

| УСТРОЙСТВО СЛЕЖЕНИЯ ЗА ЗАДЕРЖКОЙ ШУМОПОДОБНЫХ ЧАСТОТНО-МАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2006 |

|

RU2313184C1 |

| Разделитель коррелограмм | 1988 |

|

SU1506453A1 |

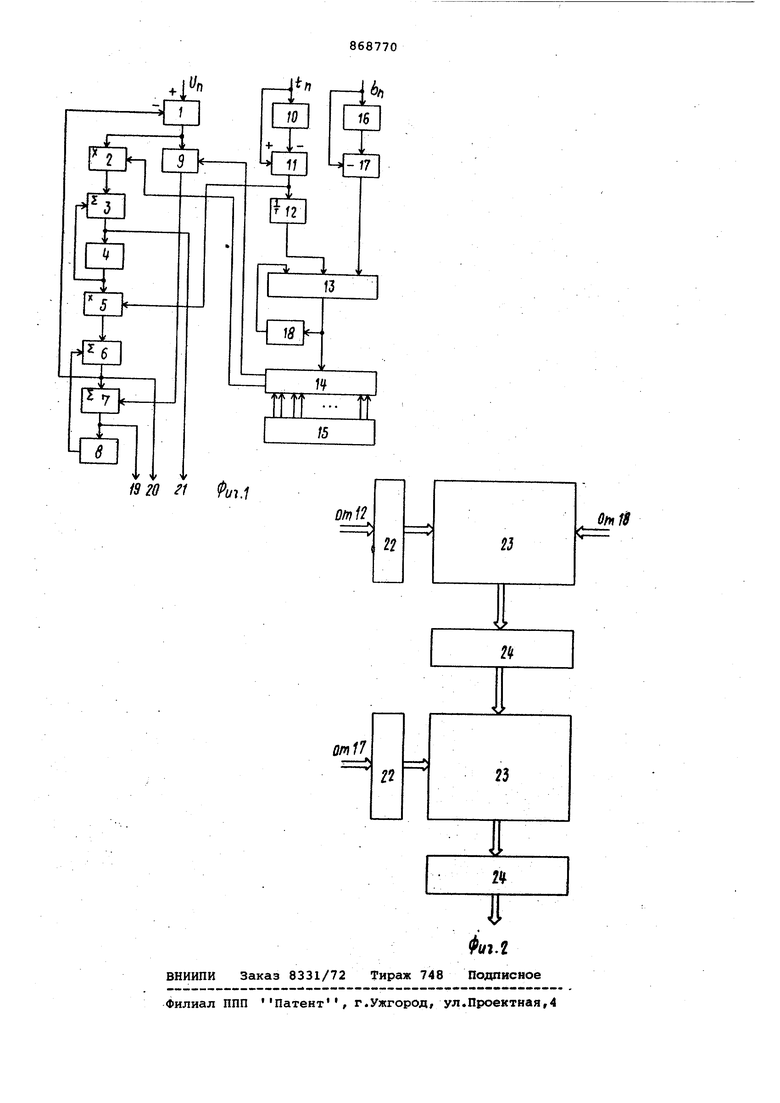

Изобретение относится к вычислительной технике и может быть использовано для сглаживания процессов с линейным изменением среднего значения случайного параметра. Известна Параллельная арифметическая структура для выполнения рекУрсивной цифровой фильтрации,содер жащая сумматор, умножитель, вентили буферную память, накопитель, память коэффициентов, блок переполнения и блок масштабирования 1} . Недоотатком этого устройства явля ется низкое быстродействие. Наиболее близким к предлагаемому является Фильтр скользящего сгла живания, содержсцций перемножители, вычитатели, сумматоры и элементы за держки 21 . Недостатком известного устройств является низкая точность сглаженного параметра. Цель изобретения - повышение точ ности работы устройства. Поставленная цель достигается тем, что в сглаживающий фильтр, содержащий три перёмножителя, первый вычитатель, три сумматора, два элемента задержки, причем выход первого вычитателя соединен с первым входом первого перемножителя, выход первого перемножителя соединен с первым входом первого сумматора, выход которого соединен через первый элемент задержки с первым входом второго перемножителя, выход которого соединен с первым входом второго сумматора, выход которого соединен с первым входом третьего сумматора, выход которого через второй элемент задержки соединен со вторым входом второго суммато-; ра, выход второго сумматора соединен с первым входом первого вычитателя, выход которого соединен с первым входом третьего перемножителя, выход которого соединен со вторым входом третьего сумматора, введены третий, четвертый и пятый элементы задержки, делитель, блок памяти, второй вычитатель, четвертый перемножитель, узел формирования коэффициентов сглаживания и коммутатор, причем второй вход первого вычитателя является первым входом фильтра, второй вход фильтра соединен с первым входом второго вычитателя и через третий элемент задержки со вторым входом второго вычитателя, выход которого соединен со вторым входом второго перемножителя и с входом четвертого перемножителя. выход четвертого перемножителя соеди нен с первым входом узла формировани коэффициентов сглаживания, выход которого соединен с входом коммутатора и с входом четвертого элемента задер жки, выход которого соединен со вторым входом узла формирования коэффициентов сглаживания, первый и второй выход коммутатора соединены соответственно со вторыми входами первого и третьего перемножителя, группа вы ходов блока памяти соединена с группой входов коммутатора, третий вход фильтра соединен с первым входом делителя и через пятый элемент задержки со вторым входом делителя, выход делителя соединен с третьим входом узла формирования коэффициентов сгла живания, выходы первого, второго и третьего сумматоров являются соответ ственно первым, вторым и третьим выходами фильтра. Узел формирования коэффициентов сглаживания содержит два дешифратора два блока элементов И и два блока элементов ИЛИ, причем вход первого дешифратора соединен с первым входом узла, выход первого дешифратора соединен с первым входом первого блока элементов И, второй вход которого соединен со вторым входом узла, выход первого блока элементов И соединен с входом первого блока элементов ИЛИ, выход которого соединен с первым входом второго блока элементов И, второй вход которого соединен с выходом второго дешифратора, вход ко торого является третьим входом узла, выход второго блока элементов И соединен с входом второго блока элементов ИЛИ, выход которого является выходом узла. На фиг. 1 представлено предлагаемое устройство, структурная схема; на фиг. 2 - блок-схема логического узла. Устройство содержит вычитатель 1, перемножитель 2 сумматор 3, элемент 4 задержки, перемножитель 5, сумматор 6, сумматор 7, элемент 8 задержки, перемножитель 9, элемент 10 за.держки, вычитатель 11, перемножитель 12, узел 13 формирования коэффициентов сглаживания, коммутатор 14, блок 15 памяти, элемент 16 задержки, дели тель 17,. элемент 18 задержки, выходы 19 - 21 устройства. Логический узел содержит дешифраторы 22, блоки 23 элементов И, блоки 24 элементов ИЛИ. . Устройство работает следующим образом. На входы вычитателя 11 и элемента 10 задержки поступает код значения времени поступления очередного отсчета случайной величины. Значение,соответствующее прошлому отсчету, поступает с выхода элемента 10 на второй вход вычитателя 11, на выходе которого получается разность времен поступления. Это значение подается на перемножитель 12, где нормируется (умно- Дается на определенный коэффициент --) и на вход перемножителя 5, на другой вход этого перемножителя подается с выхода элемента 4 задержки сглаженное значение скорости на определенный момент времени. Произведение с выхода перемножителя 5 поступает на вход сумматора б, на второй вход которого подается сглаженное значение параметра с выхода элемента 8 задержки, в соответствии с формулой (1) получаем экстраполированное значение УЭП Л + Vn.,T(1) Далее сглаживание производится в соответствии с формулами: U V, V. „ Vn,, + ,(4) лл где 1п- , Vn сглаженные значения параметра соответственно на п-1 и п-ом шаге сглаживания; л л VTI-- . Vfl - сглаженные значения скорости изменения параметра на п-1 и п-ом шаге сглаживания; М - полученное случайное значение параметра; TO - произвольный период нормировки;Т - период обновления получаемых входных случайньк значений; А,В- коэффициенты сглаживания. Экстраполированное значение подается на вход вычитателя 1, на другой вход которого подается измеренное случайное значение. На выходе вычитателя 1 получается разность экстраполированного и случайного значений в соответствии с формулой (2). На вход элемента 16 и делителя 17 поступают значения среднеквадратичной ошибки измерения данного случайного параметра. На второй вход делителя 17 с ВЕЛХода элемента 16 поступает значение ошибки на момент (п-1). Значения с выхода перемножителя 12 и делителя 17 поступают на входы узла 13, ас выхода элемента 18 - значение управляющего сигнала для.коммутатора 14 на прошедший момент (п-1). Узел 13 выбирает соответствугацие значения коэффициентов А и В/Тр с помощью дешифраторов 22 и блоков 23 и 24. В соответствии с управляющим сигналом в коммутаторе 14 производится коммутация соответствующих выходов блока 15, где в соответствующих ячейках записаны значения коэффициентов сглаживания. Эти коэффициенты подаются на входы перемножителей 2 и 9, где вычисляются .соответственно |-дУэ„ и AaVgn. о В сумматоре 7 производится вычисление сглаженного значения по формуле (3), а в сумматоре 3 - по формуле (4). Результаты вычислений с выходов 19 - 21 выдаются на вход устройства. Применение изобретения позволяет повысить точность измерения. Формула изобретения 1. Сглаживсцощий фильтр, содержащий три перемножитёля, первый вычитатель, три сумматора, два элемента задержки, причем выход первого вычитателя соединен с первым входом первого перемножителя, выход первого перемножителя соединен с первым входом первого сумматора, выход которого через первый элемент задержки сое динен с первым входом второго перемножителя , выход которого соединен с первым входом второго сумматора, выход которого соединен с первым входом третьего сумматора, выход которого через второй элемент задержки соединен со вторым входом второго сумматора, выход второго сумматора Соединен с первым входом первого вычитателя, выход которого соединен с первым.входом третьего перемножителя, выход которого соединен со вторым входом третьего сумматора, отличающийся тем, что, с целью повышения точности работы устройства оно содержит третий, четвертый и пятый элементы згщержки, делитель,блок памяти, второй вычитатель, четвертый перемножитель, узел формирования коэффициентов сглаживания и коммутатор причем второй вход первого вычитател является первым входом фильтра, второй вход фильтра соединен с первым входом второго вычитатеяя и через третий элемент задержки со вторым j входом второго вычитателя, выход которого соединен со вторым входом вто рого перемножителя и с входом четвер того перемножителя, выход четвертого перемножителя соединен с первым входом узла формирования коэффициентов сглаживания, выход которого соединен с входом коммутатора и с входом четвертого элемента задержки, выход которого соединен со вторым входом узла формирования коэффициентов сглаживания, первый и второй выходы коммутатора соединены соответственно со Еторыми входами первого и третьего перемножителя, группа выходов блока памяти соединена с группой входов коммутатора, третий вход фильтра соединен с первым входом делителя и через пятый элемент задержки со вторым входом делителя, выход де1итёля соединен с третьим входом уз- ла формирования коэффициентов сглаживания, выходы первого, второго и третьего сумматоров являются соответственно первым, вторым и третьим выходами фильтра. 2. Фильтр,по п. 1, отлича ющ и и с я тем, что узел формирования коэффициентов сглаживания содержит два дешифратора, два блока элементов И и два блока элементов ИЛИ, причем вход первого дешифратора соединен с первым входом узла, выход первого дешифратора соединен с первым входом первого блока элементов И, второй вход которого соедине.н со вторым входом узла, выход первого блока элементов и соединен с входом первого блока элементов ИЛИ, выход которого соединен с первым входом второго блока элементов И, второй вход которого соединен с выходом второго дешифрато-, ра, вход которого является третьим входом узла, выход второго блока элементов И соединен с входом второго . блока элементов ИЛИ, выход которого является выходом узла. Источники информации, принятые во внимание при экспертизе 1.Патент США № 4117541, кл. 364-724, 1976. 2.Кузьмин С.3. Основы теории цифровой обработки радиолокационной информации. М., Советское радио, 1974, с. 383, рис. 9-10 (прототип).

Авторы

Даты

1981-09-30—Публикация

1980-01-25—Подача