1

Изобретение относится к вычислительной технике и может быть использовано при статистическом анализе случайных процессов.

Известно устройство для вычисления оценки математического ожидания, содержащее генератор импульсов, счетчик выборки, регистр, три элемента И и индикатор El

Наиболее близким к предлагаемому является вычислитель оценки математического ожидания, содержащий генератор импульсов, выход которого подключен к первому входу аналого-цифрового преобразователя, второй вход которого является первым входом вычислителя, два элемента И, сумматор и счетчик выборки Г21 .

Однако известные устройства не обеспечивают получение достоверной оценки математического ожидания.

Цель изобретения - повышение достоверности оценки математического ожидания.

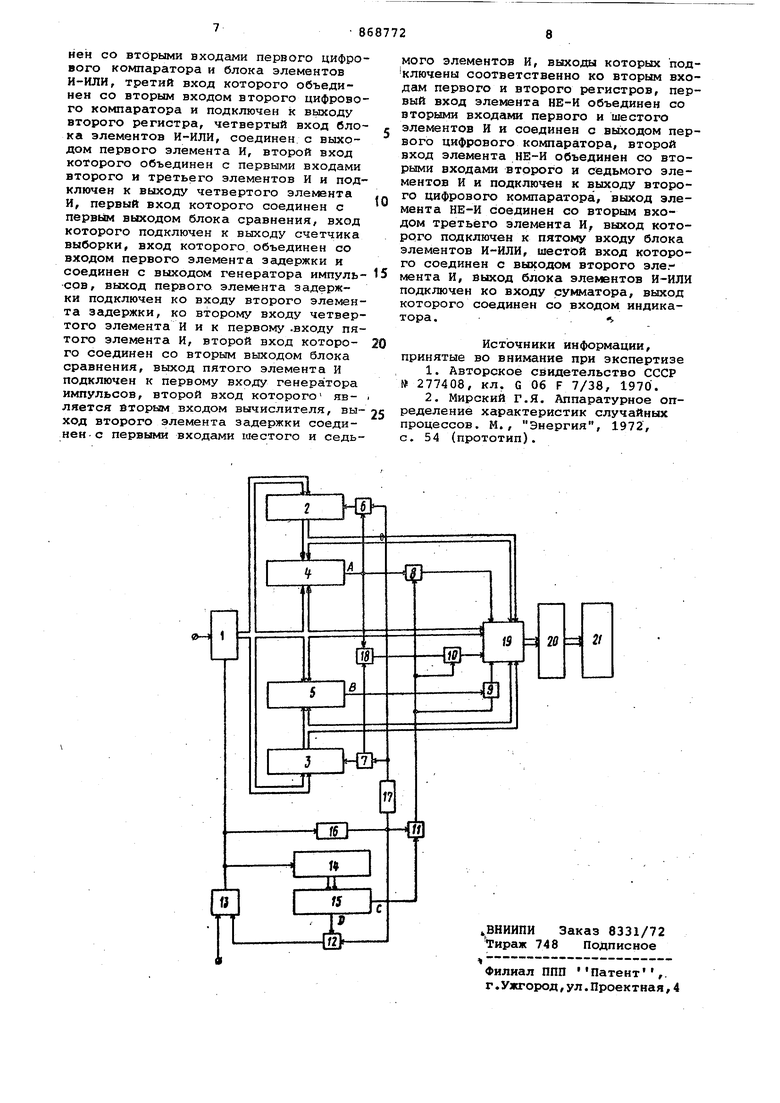

Поставленная цель достигается тем, что в вычислитель оценки матема,тического ожидания введены два регистра, два .цифровых компаратора, блок 1сравнения, два элемента задержки, блок элементов И-ИЛИ, элемент НЕ-И,

пять элементов И и блок индикации, при этом первые входы первого и второго цифровых компараторов блока элементов И-ИЛИ объединены с первыми входами первого и второго регистров и подключены к выходу аналого-цифрового, преобразователя, выход первого регистра соединен со вторыми входами первого цифрового компаратора и блока

10 элементов И-ИЛИ, третий вход которого объединен со вторым входом второго цифрового компаратора и подключен к выходу второго регистра, четвертый вход блока элементов И-ИЛИ соединен

15 с выходом первого элемента И, второй вход которого объединен с первыми входами второго и третьего элементов И и подключен к выходу четвертого элемента И, первый вход которого сое20динен с первым выходом блока сравнения, вход которого подключен к выходу счетчика выборки, вход которого объединен со входом первого элемента задержки и соединен с выходом генера25тора импульсов, выход первого элемен-. та задержки подключен ко входу второго элемента задержки, ко второму входу четвертого элемента И и к первому входу пятого элемента И, второй вход которого соединен со вторым выходом

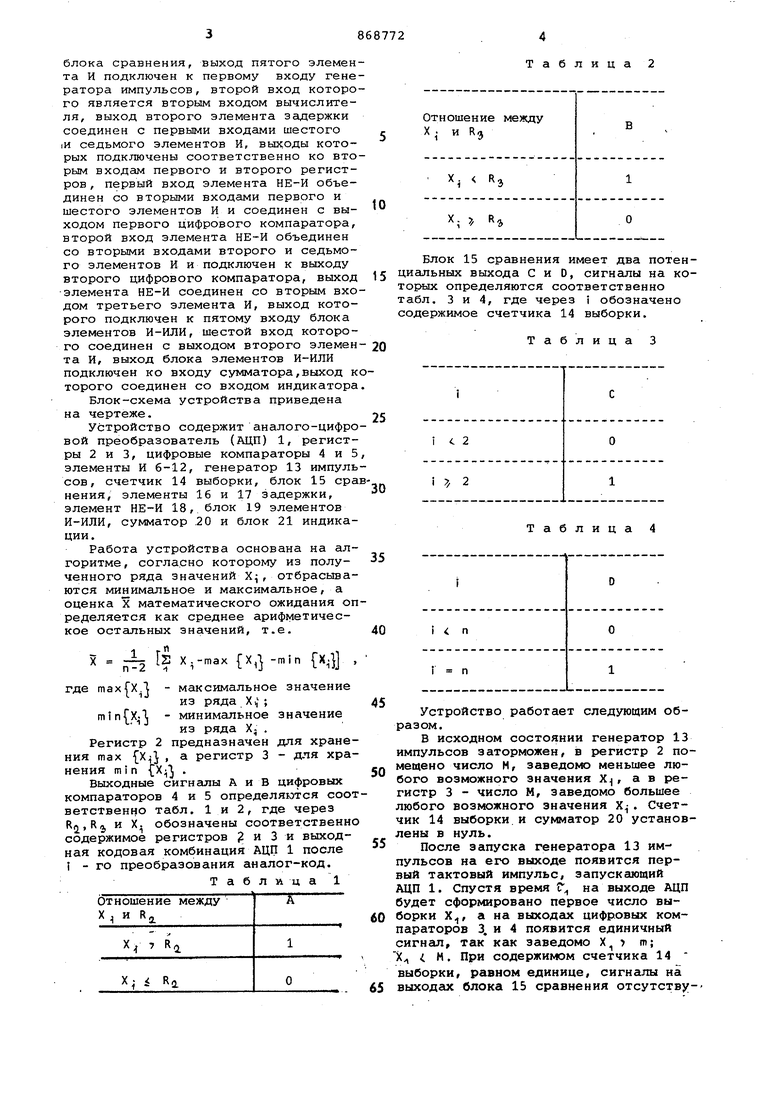

30 блока сравнения, выход пятого элемен та И подключен к первому входу гене ратора импульсов, второй вход которо го является вторым входом вычислителя, выход второго элемента задержки соединен с первыми входами шестого |И седьмого элементов И, выходы которых подключены соответственно ко вто рым входам первого и второго регистров, первый вход элемента НЕ-И объединен со вторыми входами первого и шестого элементов И и соединен с выходом первого цифрового компаратора, второй вход элемента НЕ-И объединен со вторыми входами второго и седьмого элементов И и подключен к выходу второго цифрового компаратора, выход элемента НЕ-И соединен со вторым вхо дом третьего элемента И, выход которого подключен к пятому входу блока элементов И-ИЛИ, шестой вход которого соединен с выходом второго элемен та И, выход блока элементов И-ИЛИ подключен ко входу сумматора,выход к торого соединен со входом индикатора Блок-схема устройства приведена на чертеже. Устройство содержит аналого-цифро вой преобразователь (АЦП) 1, регистры 2 и 3, цифровые компараторы 4 и 5 элементы И 6-12, генератор 13 импуль сов, счетчик 14 выборки, блок 15 срав нения, элементы 16 и 17 задержки, элемент НЕ-И 18, блок 19 элементов И-ИЛИ, сумматор .20 и блок 21 индикации. Работа устройства основана на алгоритме , согласно которому из полученного ряда значений х, отбрасываются минимальное и максимальное, а оценка X математического ожидания оп ределяется как среднее арифметическое остальных значений, т.е. 1Г2 {X,}-min Х, , где тахГХ.Я - максимальное значение из ряда Х,| ; - минимальное значение из ряда X, . Регистр 2 предназначен для хранения max , а регистр 3 - для хранения min . Выходные сигналы А и В цифровых компараторов 4 и 5 определяются соответственно табл. 1 и 2, где через Rn.Rj и X. обозначены соответственно содержимое регистров и 3 и выходная кодовая комбинация АЦП 1 после - го преобразования аналог-код. Таблица Отношение между Таблица 2 Отношение между X. и Rj Блок 15 сравнения имеет два потенциальных выхода С и D, сигналы на которых определяются соответственно табл. 3 и 4, где через i обозначено содержимое счетчика 14 выборки. Таблица 3 Таблица 4 Устройство работает следующим образом. В исходном состоянии генератор 13 импульсов заторможен, в регистр 2 помещено число Н, заведомо меньшее любого возможного значения Х, а в регистр 3 - число М, заведомо большее любого возможного значения х. Счетчик 14 выборки и сумматор 20 установлены в нуль. После запуска генератора 13 импульсов на его выходе появится первый тактовый импульс, запускающий АЦП 1. Спустя время Г на выходе АЦП будет сформировано первое число выборки Х, а на выходг1Х цифровых компараторов 3. и 4 появится единичный сигнал, так как заведомо Х т; Х 4 М. При содержимом счетчика 14 выборки, равном единице, сигнашы на выходгис блока 15 сравнения отсутствуют, ввиду чего тактовый импульр, залержанный элементом 16 задержки, не проходит через элементы И 11 и 12, поступая через элемент 17 задержки и элементы И б и 7 (поскольку А 1; В 1), на управляющие входы регистров 2 и 3, в результате формируется новое их содержимое: Кл R f Спустя некоторое время на выходе генератора 13 возникает второй тактовый импульс (напомним, что п 2). Этот импульс обусловливает появление на входе АЦП 1 второго числа выборки X,j. Возможные следующие три сочетания: XQ Xij X j) Х. В пе вом случае А О, В 1, и тактовый импульс, по-прежнему, не проходя через элементы И б и 7 (табл. 3 и 4), поступает теперь лишь на управляющий вход регистра 3 минимума, передавая в него число X f т.е. теперь R,) Х R J Х . Во втором случае А (Т, В О и, следовательно, содержимое регистров 2 и 3 не изменяется, в третьем случае А 1, В О и тактовый импульс проходит через элементы 17,16 и 6 на управляющий вход регист ра 2 максимума, т.е. получаем R п Х Ч Х. В любом случае в регистрах 2 и 3 оказываются соответственно большее и меньшее из чисел Х,Хг(, если они не равны, .и одно и то же число (Х Х в случае их равенства. После того, как на счетчик 14 выборки поступит третий тактовый импульс с выхода генератора 13, появит ся единичный сигнал на выходе с блока 15 сравнения. Благодаря этому тре тий (и все последующие) тактовый импульс, задержанный элементом 16 на время CQ , достаточное для того, чтобы на выходе АЦП 1 было получено оче редное число Х, и чтобы сформировались выходные сигналы А и В цифровых компараторов 4 и 5, пройдет через элемент И 11 и через тот из элементов И 8,9 и 10, на первом выходе которого окажется единичный сигнал. За тем, спустя время LJ задержки элемен та 17, этот импульс поступит на первые входы элементов И 6 и 7. При этом возможны следукндие три ситуации: , Х Rij, тогда А 1, В О, и тактовый импульс с выхода элемента И 11 пройдет через элемент И 8 на первый управляющий вход блока 19, в результате чего в сумматор 20 будет передано содержимое регистра 2 максимума; импульс с выхода элемента задержки 17 передает в регистр 2 зна чение Ко,, X.J 4Ла, Х,, - R, тогда А О, В i, и импульс с выхода элемента Л 11 передает в сумматор 20 содержи мое регистра 3 минимума, а импульс с выхода элемента 17 поместит в этот регистр значение Х. Ra i- X 2, R, тогда А О, в О, единичный сигнал появляется на выходе элемента НЕ-И 18, и импульс с выхода элемента И 11 передает в сумматор 20 число Х с выхода АЦП 1, содержимое регистров 2 и 3 не изменится. Каждый i - и тактовый импульс при 1 3 работает совершенно ангшогично третьему, до тех пор, пока не будет достигнуто равенство i п. При этом появится единичный сигнал на выходе блока 15, и п-й тактовый импульс, пройдя через элемент 16 задержки и элементы И 11 и 12, поступит на вход Стоп генератора 13 импульсов, прекращая работу схемы. На сумматоре 20 сформирована к этому времени величинаS X . - max {X.T, - min Х . Величину п удобно выбрать равной 2+2 (,2. . .), тогда число слагаемых, просуммированных сумматором 20, будет иметь форму 2 и деление содержимого сумматора на это число, необходимое для получения оценки (2), может быть достигнуто простым подключением J-X разрядов индикатора 21 к j+k-m разрядам сумматора (j 0,1,... m). При необходимости обрабатывать выборки произвольного объема деление на п - 2 можно выполнить, например, путем установки соответственного масштабного коэффициента АЦП 1. Предлагаемый вычислитель обладает более высокой помехоустойчивостью, т.е. обеспечивает получение более достоверной оценки математического ожидания при наличии помех, благодаря чему его применение в соответствующих системах позволяет повысить надежность и качество их функционирования. Формула изобретения Вычислитель оценки математического ожидания, содержащий генератор импульсов, выход которого подключен к первому входу аналого-цифрового преобразователя, второй вход которого является первым входом вычислителя, два элемента И, сумматор и счетчик выборки, отличающийся тем, что, с целью повышения достоверности оценки математического ожидания,, в вычислитель введены два регистра, два цифровых компаратора, блок сравнения, два элемента задержки, блок элементов И-ИЛИ, эле1«нт НЕ-И, пять элементов И и блок индикации, при этом первые входы первого и второго цифровых компараторов блока элементов И-ИЛИ объединены с первыми входами первого и второго регистров и подключены к выходу аналого-цифрового преобразователя, выход первого регистра соеди

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивный вычислитель оценки математического ожидания | 1981 |

|

SU982014A1 |

| ВЫЧИСЛИТЕЛЬ ОЦЕНКИ МАТЕМАТИЧЕСКОГО ОЖИДАНИЯ | 2002 |

|

RU2229158C1 |

| Вычислитель оценки математического ожидания | 1984 |

|

SU1190390A1 |

| Адаптивный статистический анализатор | 1987 |

|

SU1434453A1 |

| Устройство для выделения признаков при распознавании случайных сигналов | 1990 |

|

SU1797134A1 |

| Вычислитель оценки математического ожидания случайного процесса | 1980 |

|

SU932502A1 |

| Рекуррентный вычислитель оценки математического ожидания | 1978 |

|

SU746548A1 |

| АНАЛИЗАТОР НАПРЯЖЕНИЯ | 1990 |

|

RU2024880C1 |

| Вероятностный интегрирующий преобразователь аналог-код | 1987 |

|

SU1441476A1 |

| Устройство для определения среднего | 1978 |

|

SU748419A1 |

Авторы

Даты

1981-09-30—Публикация

1979-12-21—Подача