Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть использовано в блоках вычислительной техники, построенных на логических элементах.

Известен двухвходовый логический элемент И-НЕ [1 Ямпольский B.C., Основы автоматики и вычислительной техники. - М.: Просвещение, 1991 г., стр. 74, рис. 3.5], содержащий четыре транзистора, четыре резистора, один диод и источник питающего постоянного напряжения.

Недостаток его заключается в том, что у него малая нагрузочная способность. Электрический ток только одного из имеющихся транзисторов формирует электрический ток внешней нагрузки. Если бы удалось увеличить число транзисторов, формирующих ток нагрузки, то это привело бы к увеличению максимальной силы электрического тока внешней нагрузки логического элемента и в результате к повышению его нагрузочной способности.

Наиболее близким по технической сущности и достигаемому результату является выбранный в качестве прототипа логический элемент ИЛИ/ИЛИ-НЕ [Манаев Е.И. Основы радиоэлектроники. - М.: Радио и связь, 1985, стр. 342, рисунок 14.23], содержащий шесть транзисторов, пять резисторов и два источника постоянного напряжения.

Недостаток его заключается в малой нагрузочной способности. Электрический ток только одного из шести транзисторов формирует ток внешней нагрузки. Если бы удалось увеличить число транзисторов, формирующих электрический ток внешней нагрузки, то это бы привело к увеличению максимальной силы электрического тока нагрузки логического элемента и в результате к повышению нагрузочной способности. Приведенный логический элемент относится ЭСЛ-элементам (ЭСЛ - эмиттерно-связанная логика).

Задача, на решение которой направлено изобретение, состоит в повышении нагрузочной способности триггерного логического элемента И/И-НЕ.

Это достигается тем, что в триггерный логический элемент И/И-НЕ, содержащий источник питающего постоянного напряжения, минусовой вывод которого соединен с общей шиной и заземлен, последовательно между собой соединенные первый резистор, первый n-р-n транзистор и второй резистор, свободный вывод первого резистора подсоединен к выходу (плюсовой вывод) питающего источника, свободный вывод второго резистора заземлен, последовательно включенные третий резистор и второй n-р-n транзистор, свободный вывод третьего резистора подсоединен к общему выводу первого резистора и выхода источника питания, эмиттер второго транзистора подключен к общему выводу эмиттера первого транзистора и второго резистора, источник опорного напряжения, минусовой вывод которого заземлен, а плюсовой - соединен с базой второго транзистора, последовательно включенные третий n-р-n транзистор и четвертый резистор, соединенный с эмиттером третьего транзистора, последовательно включенные четвертый n-р-n транзистор и пятый резистор, подсоединенный к эмиттеру четвертого транзистора, также пятый и шестой тоже n-р-n транзисторы, эмиттеры которых соединены между собой, введены два дополнительных р-n-р транзистора, один дополнительный n-р-n двухэмиттерный транзистор и шесть дополнительных резисторов, последовательно между собой включены первый дополнительный резистор, первый дополнительный р-n-р транзистор и второй дополнительный резистор, свободный вывод первого дополнительного резистора подсоединен к общему выводу первого, третьего резисторов и выхода источника питающего напряжения, общий вывод коллектора первого дополнительного транзистора и второго дополнительного резистора подключен к базе третьего транзистора, база первого дополнительного транзистора соединена с общим выводом третьего резистора и коллектора второго транзистора, а также с коллектором третьего транзистора, свободный вывод второго дополнительного резистора соединен со свободным выводом четвертого резистора и их общий вывод образует относительно «земли» инвертирующий выход логического элемента, последовательно включены второй дополнительный р-n-р транзистор и третий дополнительный резистор, эмиттер второго дополнительного транзистора подсоединен к общему выводу первого дополнительного резистора и эмиттера первого дополнительного транзистора, база второго дополнительного транзистора соединена с общим выводом первого резистора и коллектора первого транзистора, а также с коллектором четвертого транзистора, общий вывод коллектора второго дополнительного транзистора и третьего дополнительного резистора подключен к базе четвертого транзистора, свободный вывод третьего дополнительного резистора соединен со свободным выводом пятого резистора и их общий вывод образует относительно «земли» неинвертирующий выход логического элемента, общий вывод эмиттеров пятого и шестого транзисторов заземлен, база пятого транзистора соединена с дополнительным четвертым резистором, свободный вывод которого подключен к общему выводу пятого, дополнительного третьего резисторов и неинвертирующего выхода логического элемента, коллектор пятого транзистора подсоединен к общему выводу четвертого, дополнительного второго резисторов и инвертирующего выхода логического элемента, база шестого транзистора соединена с дополнительным пятым резистором, свободный вывод которого подключен к общему выводу четвертого, дополнительного второго резисторов, коллектора пятого транзистора и инвертирующего выхода логического элемента, коллектор шестого транзистора подсоединен к общему выводу пятого, дополнительного третьего, дополнительного четвертого резисторов и неинвертирующего выхода логического элемента, выводы эмиттеров дополнительного n-р-n двухэмиттерного транзистора образуют относительно «земли» два входа логического элемента, к базе последнего транзистора подсоединен шестой дополнительный резистор, свободный вывод которого подключен к общему выводу первого, третьего, дополнительного первого резисторов и выхода питающего источника, коллектор этого последнего транзистора соединен с базой первого транзистора.

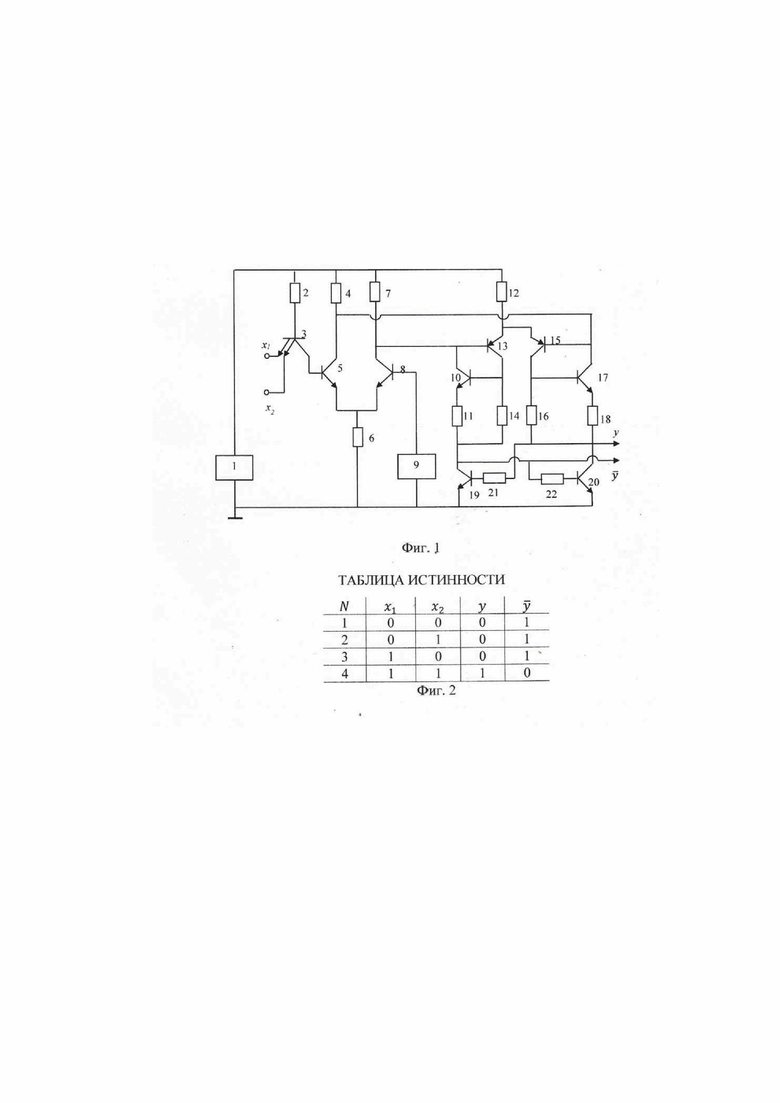

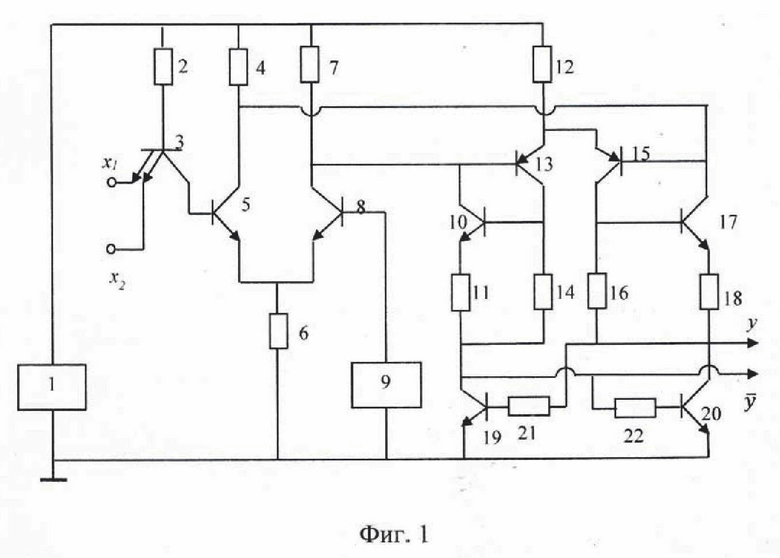

Сущность изобретения поясняется схемой триггерного логического элемента И/И-НЕ (фиг. 1) и таблицей истинности (фиг. 2).

В триггерном логическом элементе И/И-НЕ общая шина (минусовой вывод) источника 1 питающего постоянного напряжения заземлена. К выходу (плюсовой вывод) этого источника подсоединен один из выводов резистора 2, другой его вывод подключен к базе двухэмиттерного n-р-n транзистора 3. Два вывода эмиттеров этого транзистора образуют относительно «земли» два входа x1 и x2 логического элемента. Последовательно между собой включены резистор 4, n-р-n транзистор 5 и резистор 6. Свободный вывод резистора 4 подсоединен к общему выводу резистора 2 и выхода источника 1. База транзистора 5 подключена к коллектору транзистора 3, а свободный вывод резистора 6 заземлен.

Последовательно включены резистор 7 и n-р-n транзистор 8. Свободный вывод резистора 7 подсоединен к общему выводу резисторов 2, 4 и выхода питающего источника 1. Эмиттер транзистора 8 подключен к общему выводу резистора 6 и эмиттера транзистора 5. С базой транзистора 8 соединен выход (плюсовой вывод) источника 9 опорного напряжения, минусовой вывод этого источника заземлен.

Последовательно между собой включены n-р-n транзистор 10 и резистор 11. Коллектор транзистора 10 подсоединен к общему выводу резистора 7 и коллектора транзистора 8. Свободный вывод резистора 11 образует относительно «земли» инвертирующий выход у логического элемента. Последовательно включены резистор 12, р-n-р транзистор 13 и резистор 14. Свободный вывод резистора 12 соединен с общим выводом резисторов 2, 4, 7 и выхода источника 1. База транзистора 13 подключена к общему выводу резистора 7 и коллекторов транзисторов 8 и 10. Коллектор транзистора 13 соединен и с базой транзистора 10, и с одним из выводов резистора 14. Другой вывод резистора 14 подключен к общему выводу резистора 11 и инвертирующего выхода логического элемента  .

.

Последовательно включены р-n-р транзистор 15 и резистор 16. Эмиттер транзистора 15 подсоединен к общему выводу резистора 12 и эмиттера транзистора 13. База транзистора 15 подключена к общему выводу резистора 4 и коллектора транзистора 5. Свободный вывод резистора 16 образует относительно «земли» неинвертирующий выход у логического элемента. Последовательно включены n-р-n транзистор 17 и резистор 18. Коллектор транзистора 17 подсоединен к общему выводу резистора 4, коллектора транзистора 5 и базы транзистора 15. База транзистора 17 подключена к общему выводу эмиттера транзистора 15 и резистора 16. Свободный вывод резистора 18 соединен с общим выводом резистора 16 и неинвертирующего выхода y логического элемента.

Вывод эмиттера n-р-n транзистора 19 соединен с выводом эмиттера n-р-n транзистора 20 и их общий вывод заземлен. К базе транзистора 19 подсоединен один из выводов резистора 21, другой вывод этого резистора подключен к общему выводу резисторов 16, 18 и неинвертирующего выхода у логического элемента. Коллектор транзистора 19 соединен с общим выводом резисторов 11, 14 и инвертирующего выхода  логического элемента. К базе транзистора 20 подсоединен первый вывод резистора 22, второй его вывод подключен к общему выводу резисторов 11, 14, коллектора транзистора 19 и инвертирующего выхода у логического элемента. Коллектор транзистора 20 соединен с общим выводом резисторов 16,18, 21 и неинвертирующего выхода y логического элемента.

логического элемента. К базе транзистора 20 подсоединен первый вывод резистора 22, второй его вывод подключен к общему выводу резисторов 11, 14, коллектора транзистора 19 и инвертирующего выхода у логического элемента. Коллектор транзистора 20 соединен с общим выводом резисторов 16,18, 21 и неинвертирующего выхода y логического элемента.

На фиг. 1 часть схемы на транзисторах 5, 8 представляет собой переключатель тока, часть схемы на транзисторах 10, 13 является первым триггером на транзисторах противоположного типа проводимости и часть схемы на транзисторах 15, 17 является вторым триггером на транзисторах противоположного типа проводимости. Резистор 12 входит и в первый, и во второй триггеры и его можно назвать общеэмиттерным резистором. Резистор 4 входит и в переключатель тока на транзисторах 5, 8, и во второй триггер на транзисторах противоположного типа проводимости 15,17. Резистор 7 входит и в переключатель тока, и в первый триггер на транзисторах противоположного типа проводимости 10, 13.

Триггерный логический элемент И/И-НЕ работает следующим образом. В цифровой электронике используются входные и выходные электрические сигналы низкого и высокого уровней. Низкий уровень - уровень логического нуля соответствует значениям напряжения в районе нуля или ближе к нулю, высокий уровень - уровень логической единицы соответствует значениям напряжения в районе единиц вольт (нередко в районе четырех вольт).

Триггер на транзисторах 10, 13 противоположного типа проводимости имеет два состояния равновесия. В первом (условно) состоянии оба транзистора закрыты и не проводят электрический ток. Тогда, в том числе на резисторах 7 и 14, нулевые значения напряжения. Они прикладываются к базам транзисторов 10, 13 меньше пороговых напряжений этих транзисторов по абсолютной величине и в итоге поддерживают эти транзисторы в закрытом состоянии. Во втором (условно) состоянии транзисторы 10 и 13 открыты, их электрические токи создают напряжения, в том числе и на резисторах 7 и 14 по абсолютной величине и по значениям больше пороговых напряжений транзисторов и поддерживают транзисторы 10, 13 в открытом состоянии. Триггер на транзисторах противоположного типа проводимости, как и другие распространенные триггеры, переходит из первого состояния во второе и наоборот, когда управляющие входные напряжения по своим значениям превышают значения напряжений соответствующих порогов срабатывания триггера. Точно также работает второй триггер на транзисторах 15, 17 противоположного типа проводимости.

Работа логического элемента И/И-НЕ отражается таблицей истинности (фиг. 2), где x1 и x2 - условное отображение входных сигналов, у и  условное отображение сигналов на неинвертирующем и инвертирующем выходах логического элемента и N - номер строки по порядку. В соответствии со строками 1 -3 таблицы истинности на один или оба входа x1 и x2 логического элемента поступает напряжение уровня логического нуля. Тогда один или оба базо-эмиттерных р-n перехода транзистора 3 открыты и на них весьма малое значение напряжения, как на диодах в проводящим электрический ток состоянии. Базо-коллекторный р-n переход транзистора 3 тоже открыт, в итоге на базе транзистора 5 низкий уровень напряжения. За счет соответствующего значения напряжения источника 9 опорного напряжения обеспечивается требующееся значение силы электрического тока через транзистор 8. Этот ток создает на резисторе 6 напряжение, которое плюсом приложено к эмиттеру транзистора 5. Значением напряжения на резисторе 6 обеспечивается значение разности напряжений между базой и эмиттером транзистора 5 в районе порогового напряжения или близкое к нему значение. Тогда имеется малое значение силы коллекторного тока этого транзистора и малое напряжение на резисторе 4. Это малое напряжение не может обеспечить второе состояние второго триггера и включено между базой р-n-р транзистора 15 и через резистор 12 его эмиттером плюсом к эмиттеру и минусом к базе. Значением сопротивления резистора 7 обеспечивается открытое состояние n-р-n транзистора 13 и второе состояние первого триггера на транзисторах противоположного типа проводимости. Напряжение на резисторе 7 включено между базой и эмиттером р-n-р транзистора 13 минусом к базе и плюсом через резистор 12 к эмиттеру. Электрические токи транзисторов 10 и 13 триггера на транзисторах противоположного типа проводимости во втором состоянии создают на внешней нагрузке и на инвертирующем выходе

условное отображение сигналов на неинвертирующем и инвертирующем выходах логического элемента и N - номер строки по порядку. В соответствии со строками 1 -3 таблицы истинности на один или оба входа x1 и x2 логического элемента поступает напряжение уровня логического нуля. Тогда один или оба базо-эмиттерных р-n перехода транзистора 3 открыты и на них весьма малое значение напряжения, как на диодах в проводящим электрический ток состоянии. Базо-коллекторный р-n переход транзистора 3 тоже открыт, в итоге на базе транзистора 5 низкий уровень напряжения. За счет соответствующего значения напряжения источника 9 опорного напряжения обеспечивается требующееся значение силы электрического тока через транзистор 8. Этот ток создает на резисторе 6 напряжение, которое плюсом приложено к эмиттеру транзистора 5. Значением напряжения на резисторе 6 обеспечивается значение разности напряжений между базой и эмиттером транзистора 5 в районе порогового напряжения или близкое к нему значение. Тогда имеется малое значение силы коллекторного тока этого транзистора и малое напряжение на резисторе 4. Это малое напряжение не может обеспечить второе состояние второго триггера и включено между базой р-n-р транзистора 15 и через резистор 12 его эмиттером плюсом к эмиттеру и минусом к базе. Значением сопротивления резистора 7 обеспечивается открытое состояние n-р-n транзистора 13 и второе состояние первого триггера на транзисторах противоположного типа проводимости. Напряжение на резисторе 7 включено между базой и эмиттером р-n-р транзистора 13 минусом к базе и плюсом через резистор 12 к эмиттеру. Электрические токи транзисторов 10 и 13 триггера на транзисторах противоположного типа проводимости во втором состоянии создают на внешней нагрузке и на инвертирующем выходе  логического элемента напряжение уровня логической единицы. Электрический ток эмиттера транзистора 13 создает на резисторе 12 напряжение, которое минусом приложено к эмиттеру транзистора 15 и дополнительно способствует первому состоянию второго триггера на транзисторах противоположного типа проводимости 15, 17. Сила токов этих транзисторов равна нулю или почти равна нулю и создает на внешней нагрузке и на неинвертирующем выходе у логического элемента напряжение уровня логического нуля (фиг. 2).

логического элемента напряжение уровня логической единицы. Электрический ток эмиттера транзистора 13 создает на резисторе 12 напряжение, которое минусом приложено к эмиттеру транзистора 15 и дополнительно способствует первому состоянию второго триггера на транзисторах противоположного типа проводимости 15, 17. Сила токов этих транзисторов равна нулю или почти равна нулю и создает на внешней нагрузке и на неинвертирующем выходе у логического элемента напряжение уровня логического нуля (фиг. 2).

С инверсного выхода  логического элемента напряжение уровня логической единицы приложено к резистору 22 и в итоге поддерживает транзистор 20 в открытом состоянии. Тогда через этот транзистор разряжается ранее заряженная эквивалентная паразитная емкость (сумма выходной емкости логического элемента и входной емкости нагрузки). Малое сопротивление открытого транзистора 20 уменьшает постоянную времени разряда эквивалентной паразитной емкости, тем самым уменьшает время ее разряда и в результате заметно не ухудшается быстродействие схемы из-за имеющихся паразитных емкостей. С неинвертирующего выхода у логического элемента напряжение уровня логического нуля приложено к резистору 21, поэтому состояние транзистора 19 в худшем случае в районе его порогового напряжения. Сила тока этого транзистора весьма мала и электрический ток транзисторов 10, 13 почти полностью замыкается на внешнюю нагрузку, подключенную к инвертирующему выходу

логического элемента напряжение уровня логической единицы приложено к резистору 22 и в итоге поддерживает транзистор 20 в открытом состоянии. Тогда через этот транзистор разряжается ранее заряженная эквивалентная паразитная емкость (сумма выходной емкости логического элемента и входной емкости нагрузки). Малое сопротивление открытого транзистора 20 уменьшает постоянную времени разряда эквивалентной паразитной емкости, тем самым уменьшает время ее разряда и в результате заметно не ухудшается быстродействие схемы из-за имеющихся паразитных емкостей. С неинвертирующего выхода у логического элемента напряжение уровня логического нуля приложено к резистору 21, поэтому состояние транзистора 19 в худшем случае в районе его порогового напряжения. Сила тока этого транзистора весьма мала и электрический ток транзисторов 10, 13 почти полностью замыкается на внешнюю нагрузку, подключенную к инвертирующему выходу

В соответствии с четвертой строкой таблицы истинности (фиг. 2) на оба входа х1 и х2 логического элемента поступают напряжения уровня логической единицы. Оба базо-эмиттерных перехода транзистора 3 и его базо-коллекторный переход, как и ранее, открыты, тогда на базе транзистора 5 высокий уровень напряжения. Это приводит к повышению силы электрического тока транзистора 5 и повышению напряжения на резисторе 4, которое минусом приложено к базе р-n-р транзистора 15 и плюсом через резистор 12 к его эмиттеру. Такое напряжение поддерживает транзистор 15 в открытом состоянии, а второй триггер во втором состоянии. Электрические токи транзисторов 15, 17 второго триггера на транзисторах противоположного типа проводимости во втором состоянии создают на внешней нагрузке и неинвертирующем выходе у напряжение уровня логической единицы. До этого напряжения зарядится эквивалентная паразитная емкость на неинвертирующем выходе  Повышение силы электрического тока транзистора 5 приводит к уменьшению значения напряжения на базо-эмиттерном переходе транзистора 8, уменьшению силы коллекторного тока транзистора 8 и весьма малому значению напряжения на резисторе 7. Для краткости можно сказать, что напряжение на резисторе 7 настолько мало, что не оказывает влияния на работу схемы и не может перевести первый триггер на транзисторах противоположного типа проводимости во второе состояние, хотя минусом оно приложено к базе р-n-р транзистора 13. Эмиттерный ток транзистора 15 создает на резисторе 12 напряжение, которое плюсом через резистор 7 приложено к базе р-n-р транзистора 13 и минусом к его эмиттеру и тоже обеспечивает первое состояние первого триггера на транзисторах противоположного типа проводимости. Почти нулевые значения силы электрических токов транзисторов 10, 13 первого триггера на транзисторах противоположного типа проводимости в первом состоянии создают на внешней нагрузке и на инвертирующем выходе

Повышение силы электрического тока транзистора 5 приводит к уменьшению значения напряжения на базо-эмиттерном переходе транзистора 8, уменьшению силы коллекторного тока транзистора 8 и весьма малому значению напряжения на резисторе 7. Для краткости можно сказать, что напряжение на резисторе 7 настолько мало, что не оказывает влияния на работу схемы и не может перевести первый триггер на транзисторах противоположного типа проводимости во второе состояние, хотя минусом оно приложено к базе р-n-р транзистора 13. Эмиттерный ток транзистора 15 создает на резисторе 12 напряжение, которое плюсом через резистор 7 приложено к базе р-n-р транзистора 13 и минусом к его эмиттеру и тоже обеспечивает первое состояние первого триггера на транзисторах противоположного типа проводимости. Почти нулевые значения силы электрических токов транзисторов 10, 13 первого триггера на транзисторах противоположного типа проводимости в первом состоянии создают на внешней нагрузке и на инвертирующем выходе  логического элемента напряжение уровня логического нуля (фиг 2.).

логического элемента напряжение уровня логического нуля (фиг 2.).

С неинвертирующего выхода у напряжение уровня логической единицы приложено к резистору 21 и в итоге поддерживает транзистор 19 в открытом состоянии. Через этот транзистор разряжается ранее заряженная эквивалентная паразитная емкость. Малое сопротивление открытого транзистора 19 уменьшает постоянную времени разряда эквивалентной паразитной емкости, тем самым уменьшает время ее разряда и в результате заметно не ухудшается быстродействие схемы из-за имеющихся паразитных емкостей. С инвертирующего выхода  логического элемента напряжение уровня логического нуля приложено к резистору 22, поэтому состояние транзистора 20 в худшем случае в районе его порогового напряжения. Сила тока этого транзистора весьма мала и электрический ток транзисторов 15, 17 почти полностью замыкается на внешнюю нагрузку, подключенную к неинвертирующему выходу у логического элемента. При переходе одного или двух входных сигналов от уровня логического нуля к двум входным сигналам уровня логической единицы сила эмиттерного тока транзистора 5 возрастает, а сила эмиттерного тока транзистора 8 убывает. При переходе двух входных сигналов от уровня логической единицы к одному или двум входным сигналам уровня логического нуля сила эмиттерного тока транзистора 5 убывает, а сила эмиттерного тока транзистора 8 возрастает.

логического элемента напряжение уровня логического нуля приложено к резистору 22, поэтому состояние транзистора 20 в худшем случае в районе его порогового напряжения. Сила тока этого транзистора весьма мала и электрический ток транзисторов 15, 17 почти полностью замыкается на внешнюю нагрузку, подключенную к неинвертирующему выходу у логического элемента. При переходе одного или двух входных сигналов от уровня логического нуля к двум входным сигналам уровня логической единицы сила эмиттерного тока транзистора 5 возрастает, а сила эмиттерного тока транзистора 8 убывает. При переходе двух входных сигналов от уровня логической единицы к одному или двум входным сигналам уровня логического нуля сила эмиттерного тока транзистора 5 убывает, а сила эмиттерного тока транзистора 8 возрастает.

Приведенные прототип и триггерный логический элемент И/И-НЕ относятся к ЭСЛ-элементам (ЭСЛ - эмиттерно-связанная логика). Известно, что ЭСЛ-элементы имеют повышенное быстродействие [например, Гольденберг Л.М. Импульсные устройства. - М.: Радио и связь, 1981, стр. 57, раздел «Динамические характеристики», абзацы 1, 2, … 6].

Таким образом, в триггерном логическом элементе И/И-НЕ силы электрических токов внешних нагрузок равны сумме силы токов двух транзисторов 10, 13 и 15, 17, что повышает нагрузочную способность этого логического элемента. В прототипе электрический ток нагрузки формирует только один из транзисторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| ТРИГГЕРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ 2И-ИЛИ/2И-ИЛИ-НЕ | 2024 |

|

RU2829649C1 |

| ТРИГГЕРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НЕ/ИЛИ/И/ИЛИ-НЕ/И-НЕ | 2024 |

|

RU2839130C1 |

| Триггерный логический элемент И | 2022 |

|

RU2802370C1 |

| Триггерный логический элемент ИЛИ/ИЛИ-НЕ | 2022 |

|

RU2805495C2 |

| Триггерный логический элемент ИЛИ/ИЛИ-НЕ | 2021 |

|

RU2767177C1 |

| Триггерный логический элемент И/ИЛИ | 2022 |

|

RU2785277C1 |

| Триггерный логический элемент 2И-ИЛИ-НЕ | 2024 |

|

RU2826843C1 |

| Триггерный логический элемент И-НЕ/ИЛИ-НЕ | 2022 |

|

RU2792973C1 |

| Триггерный логический элемент 2И/ИЛИ | 2024 |

|

RU2826617C1 |

| Логический элемент | 1984 |

|

SU1261105A1 |

Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике и, в частности, может быть использовано в блоках вычислительной техники, построенных на логических элемента. Техническим результатом изобретения является повышение нагрузочной способности триггерного логического элемента И/И-НЕ. Триггерный логический элемент И/И-НЕ дополнительно содержит два дополнительных р-n-р-транзистора, один дополнительный n-р-n-двухэмиттерный транзистор и шесть дополнительных резисторов. Последовательно между собой включены первый дополнительный резистор, первый дополнительный р-n-р-транзистор и второй дополнительный резистор. Общий вывод коллектора первого дополнительного транзистора и второго дополнительного резистора подключен к базе третьего транзистора. База первого дополнительного транзистора соединена с общим выводом третьего резистора и коллекторами второго и третьего транзисторов. Последовательно включены второй дополнительный р-n-р-транзистор и третий дополнительный резистор. Эмиттер второго дополнительного транзистора подсоединен к общему выводу первого дополнительного резистора и эмиттера первого дополнительного транзистора. База второго дополнительного транзистора соединена с общим выводом первого резистора и коллекторов первого и четвертого транзисторов. Общий вывод коллектора второго дополнительного транзистора и третьего дополнительного резистора подключен к базе четвертого транзистора. Общий вывод эмиттеров пятого и шестого транзисторов заземлен. База пятого транзистора соединена с дополнительным четвертым резистором. База шестого транзистора соединена с дополнительным пятым резистором. Свободный вывод дополнительного пятого резистора подключен к коллектору пятого транзистора, свободным выводам четвертого и дополнительного второго резисторов и их общий вывод образует относительно «земли» инвертирующий выход логического элемента. Коллектор шестого транзистора подсоединен к свободным выводам пятого и дополнительных третьего и четвертого резисторов и их общий вывод образует относительно «земли» неинвертирующий выход логического элемента. Выводы эмиттеров дополнительного n-р-n-двухэмиттерного транзистора образуют относительно «земли» два входа логического элемента. К базе дополнительного n-р-n-двухэмиттерного транзистора подсоединен шестой дополнительный резистор. Свободный вывод шестого дополнительного резистора подключен к свободному выводу первого дополнительного резистора и общему выводу первого и третьего резисторов и выхода источника питающего напряжения. Коллектор дополнительного n-р-n-двухэмиттерного транзистора соединен с базой первого транзистора. 2 ил.

Триггерный логический элемент И/И-НЕ, содержащий источник питающего постоянного напряжения, минусовой вывод которого соединен с общей шиной и заземлен, последовательно между собой соединенные первый резистор, первый n-р-n-транзистор и второй резистор, свободный вывод первого резистора подсоединен к выходу (плюсовой вывод) питающего источника, свободный вывод второго резистора заземлен, последовательно включенные третий резистор и второй n-р-n-транзистор, свободный вывод третьего резистора подсоединен к общему выводу первого резистора и выхода источника питания, эмиттер второго транзистора подключен к общему выводу эмиттера первого транзистора и второго резистора, источник опорного напряжения, минусовой вывод которого заземлен, а плюсовой соединен с базой второго транзистора, последовательно включенные третий n-р-n-транзистор и четвертый резистор, соединенный с эмиттером третьего транзистора, последовательно включенные четвертый n-р-n-транзистор и пятый резистор, подсоединенный к эмиттеру четвертого транзистора, также пятый и шестой тоже n-р-n-транзисторы, эмиттеры которых соединены между собой, отличающийся тем, что в него введены два дополнительных р-n-р-транзистора, один дополнительный n-р-n-двухэмиттерный транзистор и шесть дополнительных резисторов, последовательно между собой включены первый дополнительный резистор, первый дополнительный р-n-р-транзистор и второй дополнительный резистор, свободный вывод первого дополнительного резистора подсоединен к общему выводу первого, третьего резисторов и выхода источника питающего напряжения, общий вывод коллектора первого дополнительного транзистора и второго дополнительного резистора подключен к базе третьего транзистора, база первого дополнительного транзистора соединена с общим выводом третьего резистора и коллектора второго транзистора, а также с коллектором третьего транзистора, свободный вывод второго дополнительного резистора соединен со свободным выводом четвертого резистора и их общий вывод образует относительно «земли» инвертирующий выход логического элемента, последовательно включены второй дополнительный р-n-р-транзистор и третий дополнительный резистор, эмиттер второго дополнительного транзистора подсоединен к общему выводу первого дополнительного резистора и эмиттера первого дополнительного транзистора, база второго дополнительного транзистора соединена с общим выводом первого резистора и коллектора первого транзистора, а также с коллектором четвертого транзистора, общий вывод коллектора второго дополнительного транзистора и третьего дополнительного резистора подключен к базе четвертого транзистора, свободный вывод третьего дополнительного резистора соединен со свободным выводом пятого резистора и их общий вывод образует относительно «земли» неинвертирующий выход логического элемента, общий вывод эмиттеров пятого и шестого транзисторов заземлен, база пятого транзистора соединена с дополнительным четвертым резистором, свободный вывод которого подключен к общему выводу пятого, дополнительного третьего резисторов и неинвертирующего выхода логического элемента, коллектор пятого транзистора подсоединен к общему выводу четвертого, дополнительного второго резисторов и инвертирующего выхода логического элемента, база шестого транзистора соединена с дополнительным пятым резистором, свободный вывод которого подключен к общему выводу четвертого, дополнительного второго резисторов, коллектора пятого транзистора и инвертирующего выхода логического элемента, коллектор шестого транзистора подсоединен к общему выводу пятого, дополнительного третьего, дополнительного четвертого резисторов и неинвертирующего выхода логического элемента, выводы эмиттеров дополнительного n-р-n-двухэмиттерного транзистора образуют относительно «земли» два входа логического элемента, к базе последнего транзистора подсоединен шестой дополнительный резистор, свободный вывод которого подключен к общему выводу первого, третьего, дополнительного первого резисторов и выхода питающего источника, коллектор этого последнего транзистора соединен с базой первого транзистора.

| Триггерный логический элемент И/И-НЕ | 2020 |

|

RU2727613C1 |

| RU 2760464 C1, 25.11.2021 | |||

| Триггерный логический элемент НЕ/ИЛИ/И/ИЛИ-НЕ/И-НЕ | 2021 |

|

RU2760206C1 |

| Интегральная микросхема И @ микропроцессора | 1980 |

|

SU938410A1 |

| US 3622810 A, 23.11.1971 | |||

| СПОСОБ ОПРЕДЕЛЕНИЯ ЗЕНИТНОГО И ВИЗИРНОГО УГЛОВ | 1997 |

|

RU2121573C1 |

| CN 106486963 A, 08.03.2017 | |||

| МАНАЕВ Е.И | |||

| Основы радиоэлектроники | |||

| М.: Радио и связь | |||

| Способ приготовления консистентных мазей | 1919 |

|

SU1990A1 |

| СПОСОБ ПОЛУЧЕНИЯ ТВЕРДЫХ ПРОДУКТОВ УПЛОТНЕНИЯ ФОРМАЛЬДЕГИДА С ФЕНОЛАМИ И ДРУГИМИ ВЕЩЕСТВАМИ | 1925 |

|

SU512A1 |

| Рис | |||

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

Авторы

Даты

2023-01-30—Публикация

2022-03-14—Подача