(54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ АДРЕСОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1553978A1 |

| Устройство для тестового контроля цифровых блоков | 1984 |

|

SU1251084A1 |

| Микропроцессор | 1982 |

|

SU1119021A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1059573A1 |

| Микропрограммное устройство управления | 1981 |

|

SU968813A1 |

| Устройство для тестового контроля цифровых блоков | 1987 |

|

SU1539782A2 |

| Микропрограммное устройство управления | 1982 |

|

SU1030801A1 |

| Микропрограммное устройство управления | 1984 |

|

SU1264172A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1280642A2 |

1

Изобретение относится к вычислительной технике и предназначено для построения микропрогра№шых устройств управления ЭВЯ.

Известно микропрограммное устройство управления, содержащее регистр микрокоманд, дешифраторы кодов условий, регистр адреса микрокоманды, в котором для организации условных переходов более чем по двум направлениям используется модифИ1 ация содержимого регистра ащреса микрокоманды результатом проверки условий 1 .

Недостатком такого устройства является низкое быстродействие.

Наиболее близким по технической сущности и достигаемому результату к предлагаемому является устройство, содержащее регистр микрокоманд, дешифраторы кодов условий, коммутатор и узел приоритета Г2 .

Недостатком такого устройства являются недостаточные функциональные возможности.

Цель изобретения - расширение функциональных возможностей устройства за счет возможности модификации любого модифицируемого разряда . адреса микрокоманды. :

Поставленная цель достигается тем, что в устройство для формирования адресов, содержащее входной регистр, выходной регистр, первую группу дешифраторов и группу схем сравнения, причем первая группа разрядных выходов входного регистра соединена со входами дешифраторов первой группы, выход каждого дешиф10ратора первой группы соединен с первым входом соответствующей схемы сравнения группы, вторые входы которых соединены с соответствующими входами условий устройства, вве15дены вторая группа дешифраторов и группа элементов ИЛИ, причем выход калсдой схемы сравнения группы соединен с управляющим входом соответствующего дешифратора второй группы,

20 вторая группа разрядных выходов входного регистра соединена с информационными входами дешифраторов второй группы,группа выходов каждого дешифратора второй группы соединена с соот25ветствующим входом каждого элемента ИЛИ группы,выходы элементов ИЛИ группы соединены с группой информационных входов выходного регистра.

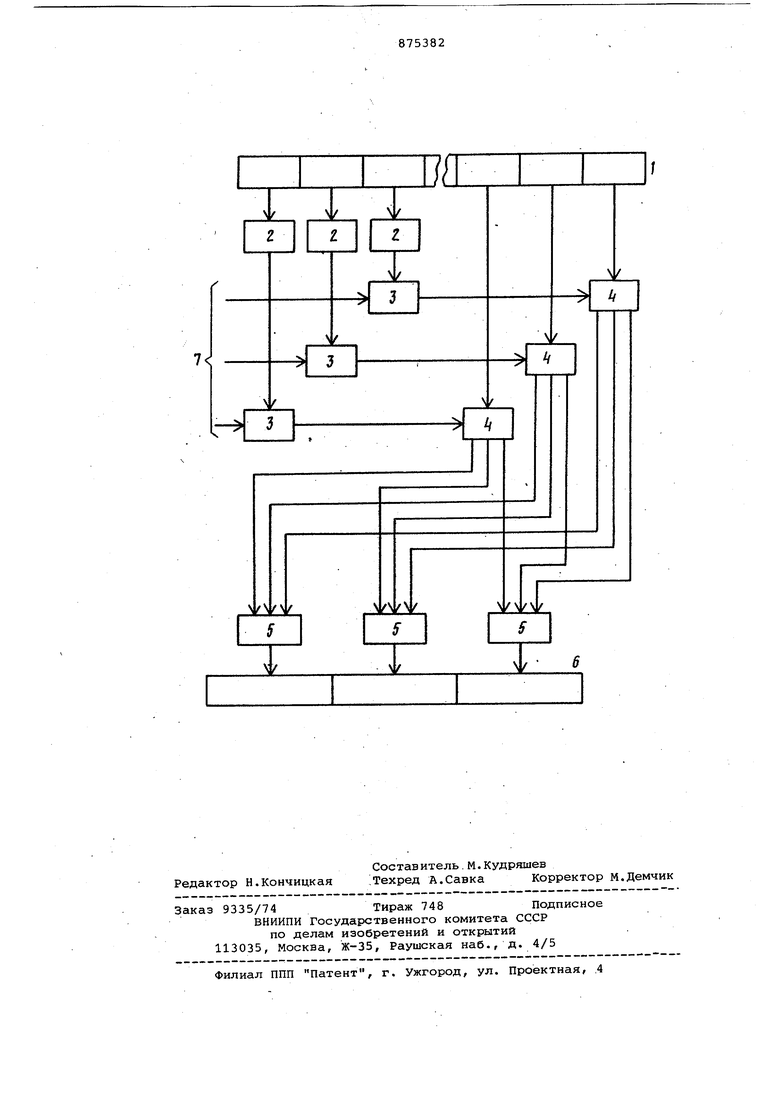

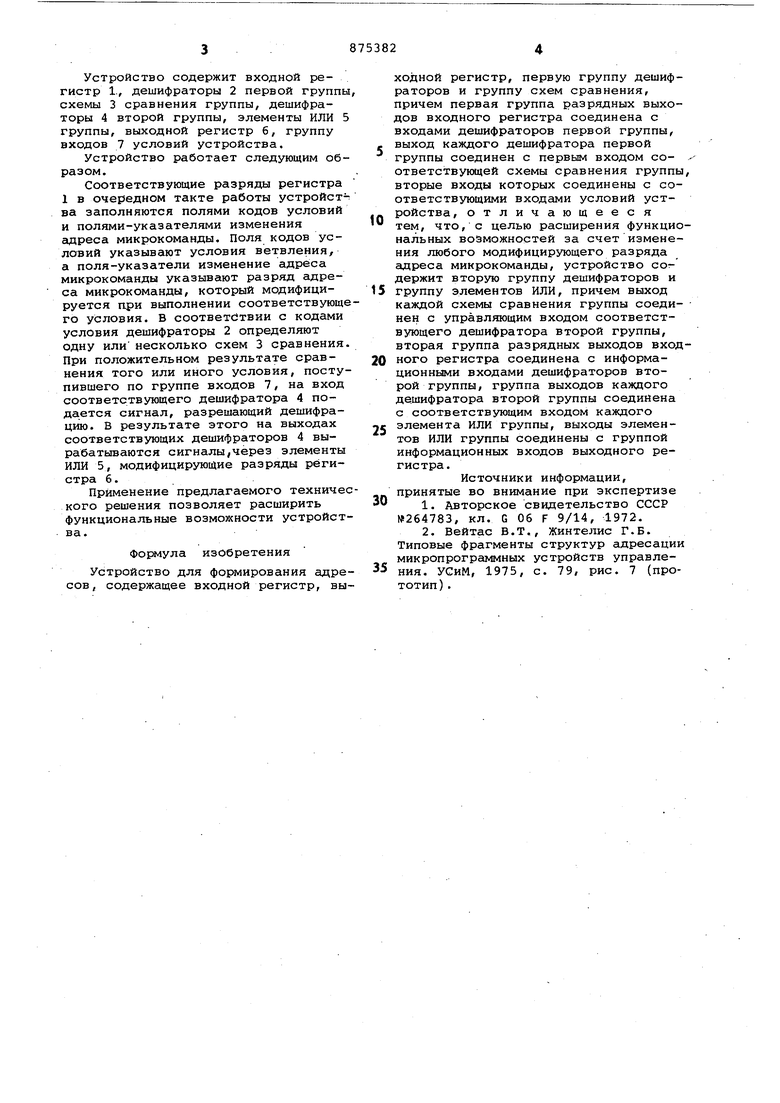

На чертеже представлена структур30ная схема устройства.

Устройство содержит входной регистр 1, дешифраторы 2 первой группы схемы 3 сравнения группы, дешифраторы 4 второй группы, элементы ИЛИ 5 группы, выходной регистр б, группу входов 7 условий устройства.

Устройство работает следующим образом.

Соответствующие разряды регистра 1 в очередном такте работы устройств ва заполняются полями кодов условий и полями-указателями изменения адреса микрокоманды. Поля кодов условий указывают условия ветвления, а поля-указатели изменение адреса микрокоманды указывают разряд адреса микрокоманды, который модифицируется при выполнении соответствующего условия. В соответствии с кодами условия дешифраторы 2 определяют одну или несколько схем 3 сравнения. При положительном результате сравнения того или иного условия, поступившего по группе входов 7, на вход соответствующего дешифратора 4 подается сигнал, разрешающий дешифрацию. В результате этого на выходах соответствующих дешифраторов 4 вырабатываются сигналы,через элементы ИЛИ 5, модифицирующие разряды регистра 6.

Применение предлагаемого технического решения позволяет расширить функциональные возможности устройства.

Формула изобретения

Устройство для формирования адресов, содержащее входной регистр, выходной регистр, первую группу дешифраторов и группу схем сравнения, причем первая группа разрядных выходов входного регистра соединена с входами дешифраторов первой группы, выход каждого дешифратора первой

группы соединен с первым входом со- .,ответствующей схемы сравнения группы, вторые входы которых соединены с соответствующими входами условий устройства, отличающееся

тем, что, с целью расширения функциональных возможностей за счет изменения любого модифицирующего разряда адреса микрокоманды, устройство согдержит вторую группу дешифраторов и

группу элементов ИЛИ, причем выход каждой схемь сравнения группы соединен с управляющим входом соответствующего дешифратора второй группы, вторая группа разрядных выходов входного регистра соединена с информационными входами дешифраторов второй группы, группа выходов каждого дешифратора второй группы соединена с соответствующим входом каждого

элемента ИЛИ группы, выходы элементов ИЛИ группы соединены с группой информационных входов выходного регистра.

Источники информации, принятые во внимание при экспертизе

Авторы

Даты

1981-10-23—Публикация

1980-03-12—Подача