(54) УСТРОЙСТВО ДЛЯ ПРОГРАММНОГО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1988 |

|

SU1529236A1 |

| Многоканальный преобразователь угла поворота вала в код | 1983 |

|

SU1144190A1 |

| Вычислительное устройство с микропрограммным управлением | 1970 |

|

SU439816A1 |

| Программируемый контроллер | 1987 |

|

SU1442976A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1288704A1 |

| Устройство для сопряжения центрального процессора с группой арифметических процессоров | 1984 |

|

SU1254495A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

| Устройство для контроля памяти | 1983 |

|

SU1280459A1 |

| Устройство для анализа вызванных потенциалов головного мозга | 1990 |

|

SU1804787A1 |

| Многопроцессорная система | 1987 |

|

SU1464168A1 |

1

Изобретение относится к автоматике и вычислительной технике и предназначено для программной реализации большого числа логических и счетных функций в системах управления производственными механизмами, технологическими процессами и другим оборудованием с разветвленной логикой управления.

Известно устройство для программного управления., содержгидее счетчик адресов, память программ, дешифратор кодов операций, блок логической обработки информации, оперативную память для хранения промежуточных регзультатов вычислений,.блок входов, включающий адресный коммутатор входов, блок входов, включающий адресный коммутатор выходов и устройства для хранения состояния выходов между обращениями. программы к ним .

Эти контролеры имеют ограниченное применение, так как предназначены только для замены релейно-контактных систем.

Наиболее близким техническим решением к изобретению/ является устройство для прО1 раммного управления, содержащее счетчик, выход и вход которого соединены через первый блок

памяти и подключены к адресной шине, .соединенной с первыми.входами входного и выходного коммутаторов и второго блока пемяти соответственно через третий блок памяти и непосредственно, а вторые входы обоих коммутаторов и второго блока Пё1МЯТИ

соединены с одним входом логического блока и через дешифратор - с другим

10 выходом третьего блока памяти,причем другой вход логического блока подключен к выходу входного коммутатора,а выход - к третьим входгш второго блока памяти и выходного коммутатора Г2.

15

Недостатками указанного устройства являются введение только логических операций, что приводит при введении реле времени и счетчиков сигналов к дополнительным аппаратурным затратам, и невозможность организации циклических программ, так как выбор номера входа и выхода производится с помощью адресной части команды,что при большом числе входов,выходов приводит к увеличению адресной части кбманды, и, как следствие этого, к уменьшению числа типов команд,что ведет к сокращению области применения устройства.

Цель изобретения - расширение области применения устройства за счет реализаций циклических программ.

Указанная цель достигается тем, что в известном устройстве для программного управления, содержащем счетчик, выход и вход которого соединены через первый блок памяти и подключены к адресной шине, соединенной с первыми входами входного и выходного коммутаторов и второго блока памяти соответственно через третий блок памяти .и непосредственно, а вторые входы обоих коммутаторов и второго блока памяти соединены с одним входом логического блока и через дешифратор - с другим выходом третьего блока памяти,причем другой вход логического блока подключен к выходу входного коммутатора, а выход - к третьим входам второго блока памяти и выходного коммутатора, дополнительный выход логического блока соединен с адресной шиной.

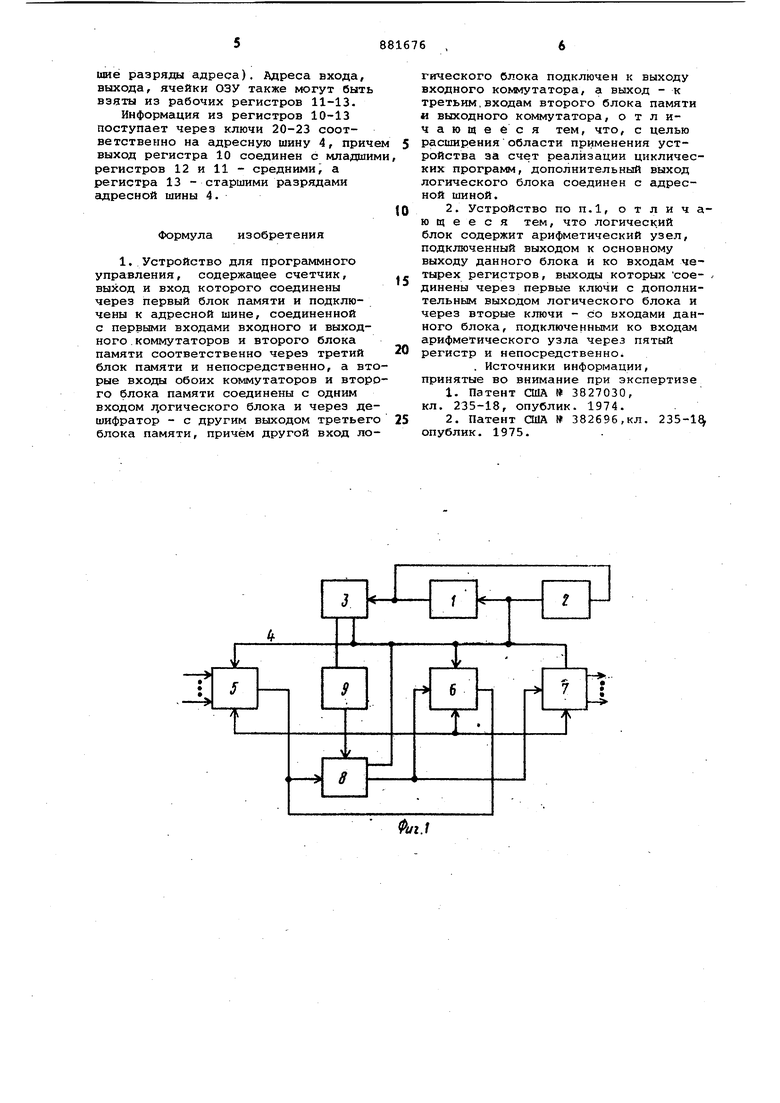

Указанная цель достигается также тем, что логический блок содержит арифметический узел, подключенный входом к основному выходу данного блока и ко входам четырех регистров выходы которых соединены через первые ключи с дополнительным выходом логического блока и через вторые ключи - со входами данного блока, подключенными ко входам арифметического узла через пятый регистр и непосредственно.

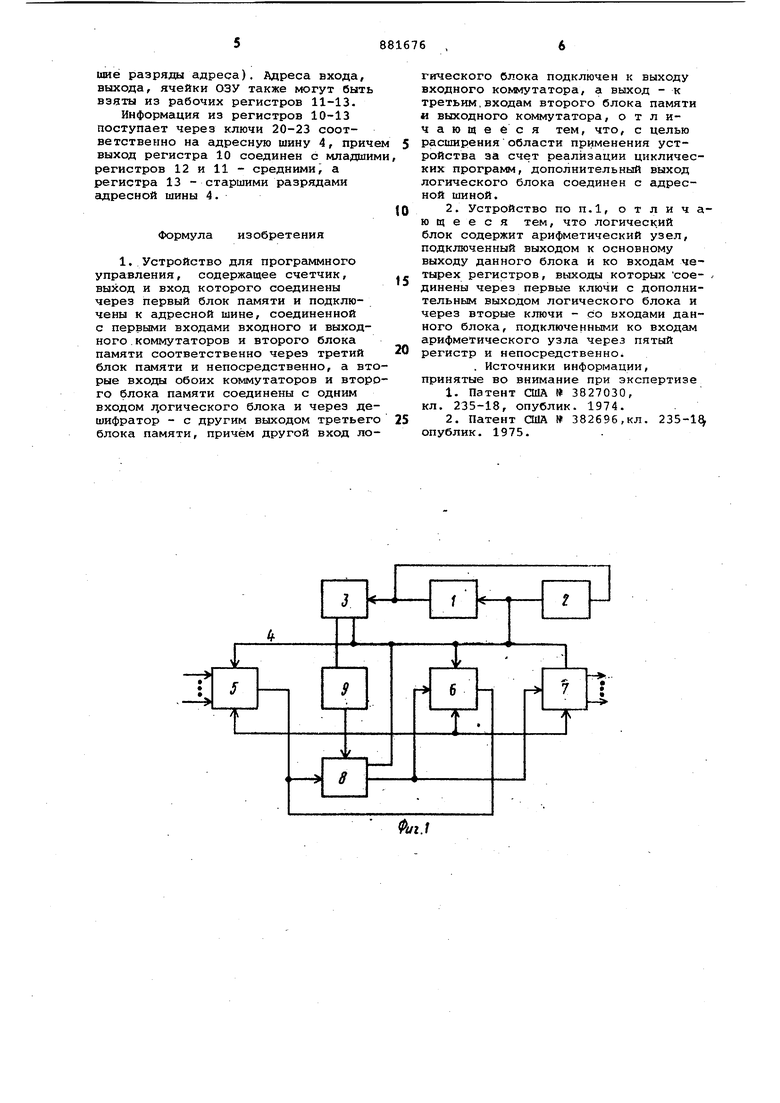

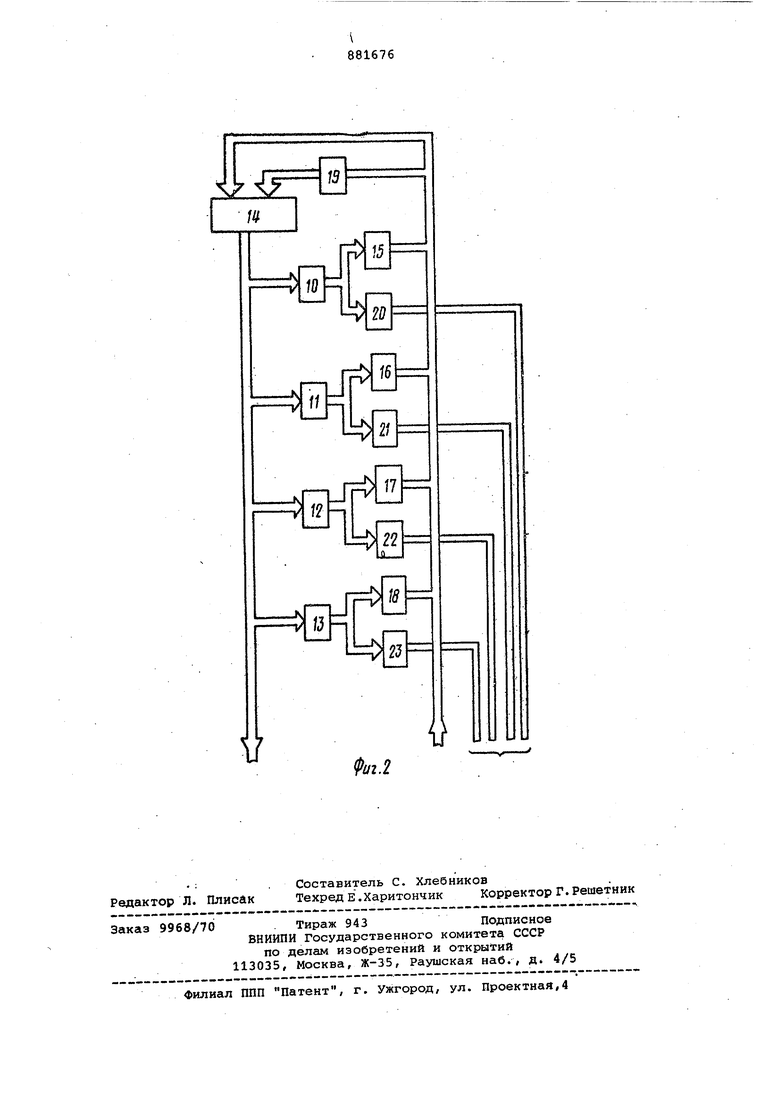

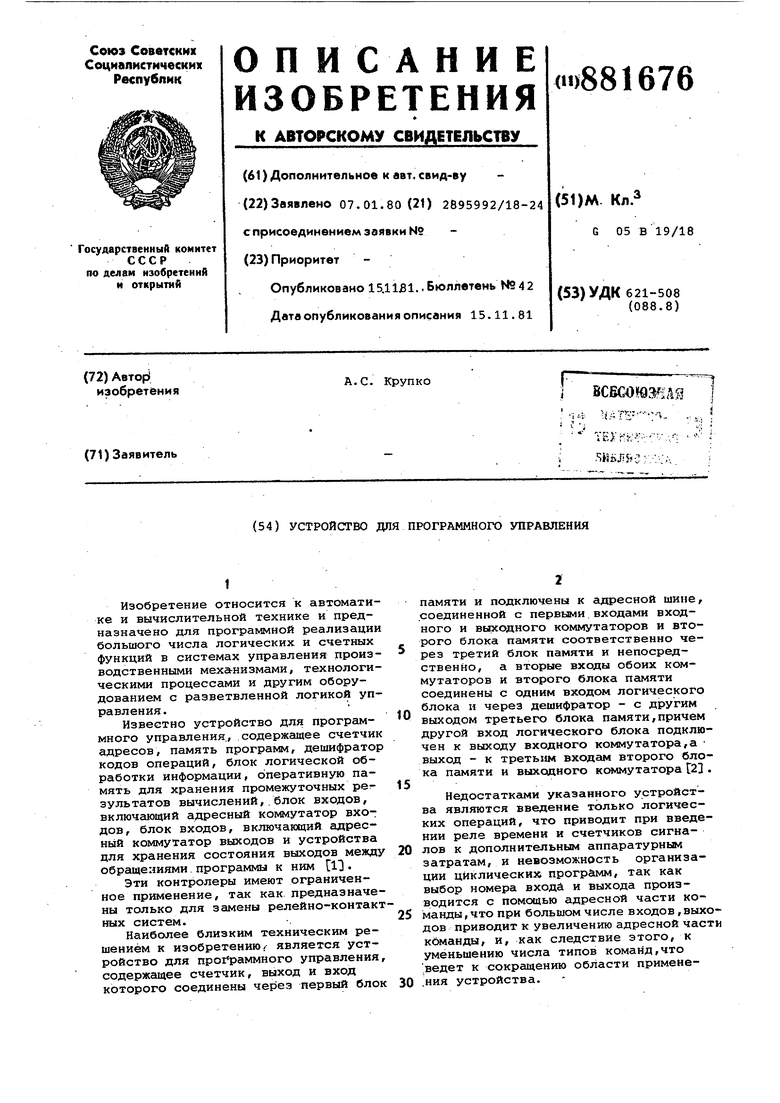

На фиг. 1 показана функциональная схема устройства на фиг. 2 функциональная схема логического блока.

Устройство содержит счетчик команд СК 1, первый блок памяти стек 2, третий блок памяти - постоянное запоминающее устройство (ПЗУ) 3 адресную шину 4, входной коммутатор - блок входов 5, второй блок памяти - оперативное запоминающее устройство (ОЗУ) 6, выходной коммутатор - блок выходов 7, логический блок 8 и дешифратор кодов операций (ДШКОп) 9. Логический блок 8 содержит четыре первых рабочих регистра РА, РГ, РВ, РБ соответственно 1013, арифметический узел - арифметикологическое устройство (АЛУ).выполненное на интегральной микросхеме К155 ИПЗ 14, первые ключи 15-18, пятый дополнительный регистр (РД) 19, вторые дополнительные ключи 20-23.

Устройство работает следующим образом.

Каждый цикл выполнения команд состоит из пяти тактов. В начале первого такта в счетчик команд 1 прибавляется единица и из ПЗУ 3 выбирается код операций команды. По .заднему фронту импульса первого такта код операции команды записывается в дакОп 9 и анализируется там. В случае двухбайтной команды по переднему фронту третьего такта в счетчик команд 1 прибавляется еще одна единица, и на выходе ПЗУ 3 появляется код адресной части команды,который производит выборку нужного входа. Информация о состоянии входа какоголибо из ключей 15-18 поступает на вх АЛУ 14 во время четвертого и пятого тактов.АЛУ 14,под воздействием управляющих сигналов из ДШКОп 9 выполняет операцию прямой передачи информации с первого входа на выход, откуда и-формация по заднему фронту четвертог тактового импульса записывается в регистр РА 10.

При командах, выполняющих операции над двумя операндами, первый операнд записывается по заднему фронту первого тактового импульса в РД 19, а второй поступает непосредственно на первый вход АЛУ 14, которое выполняет необходимую операцию над информацией на своих входах.

Принцип работы устройства заключается в последовательном опросе входных сигналов, их логической обработки и выдаче сигналов в выходные устройства, которые обеспечивают хранение сигнала до следующего цикла работы.

Блок входов 5 предназначен для сопряжения входных сигналов с уровнем логических сигналов логического блока 8, гальванической развязки между ними и выбора опрашиваемого входа

Блок выходов 7 служит для усиления мощности выходных логических сигналов до уровня, необходимого для срабатывания исполнительным устройств, гальванической развязки между логическими и силовыми сигналами, для выбора адресуемого выхода и для хранения состояния выходов между обращениям и к ним.

Логический блок 8 служит для логической обработки входных и получения выходных сигналов, для опроса входных каналов и посылки информации в выходные каналы по программе, записанной в постоянной памяти.

Счетчик команд 1 служит для последовательного опроса ячеек постоянного запоминающего устройства (ПЗУ) 3. Команда, выбираемая из ПЗУ 3,может быть одно- или двухбайтной.В случае однобайтной команды производятся операции над содержимым рабочих регистров 10-13. В случае двухбайтной команды первый байт является кодом операции и направляется в ДШКОп 9, второй байт является адресной частью и подается на блоки входов 5, выходов 7, в ОЗУ 6 для выбора канала входа - выхода или ячейки ОЗУ Для расширения возможностей адресации входов, выходов, янеек ОЗУ может использоваться регистр 11 (старшиё разряды адреса). Адреса входа, выхода, ячейки ОЗУ также могут быть взяты из рабочих регистров 11-13. Информация из регистров 10-13 поступает через ключи 20-23 соответственно на адресную шину 4, прич выход регистра 10 соединен с младши регистров 12 и 11 - средними, а регистра 13 - старшими разрядами адресной шины 4, Формула изобретения 1. Устройство для nporpeiMMHoro управления, содержащее счетчик, выход и вход которого соединены через первый блок памяти и подключены к адресной шине, соединенной с первыми входами входного и выходного .коммутаторов и второго блока памяти соответственно через третий блок памяти и непосредственно, а вт рые входы обоих коммутаторов и втор го блока памяти соединены с одним входом ;oгичecкoгo блока и через де шифратор - с другим выходом третьег блока памяти, причём другой вход ло гического блока подключен к выходу входного коммутатора., а выход - к третьим,входам второго блока памяти и выходного коммутатора, отличающееся тем, что, с целью расширения области применения устройства за счет реализации циклических программ, дополнительный выход логического блока соединен с адресной шиной. 2. Устройство ПОП.1, отличающееся тем, что логический блок содержит арифметический узел, подключенный выходом к основному выходу данного блока и ко входам четырех регистров, выходы которых соединены через первые ключи с дополнительным выходом логического блока и через вторые ключи - со входами данного блока, подключенными ко входам арифметического узла через пятый регистр и непосредственно. . Источники информации, принятые во внимание при экспертизе 1.Патент США 3827030, кл. 235-18, опублик. 1974. 2.Патент США 382696,кл. 235-1 опублик. 1975.

J

r

li

fe.2

Авторы

Даты

1981-11-15—Публикация

1980-01-07—Подача