Изобретение относится к вычислительной технике и может быть исполь- овано в многопроцессорных вьтисли- 4ельных системах с общей многомодульной памятью,

; Целью изобретения является упроще- устройства.

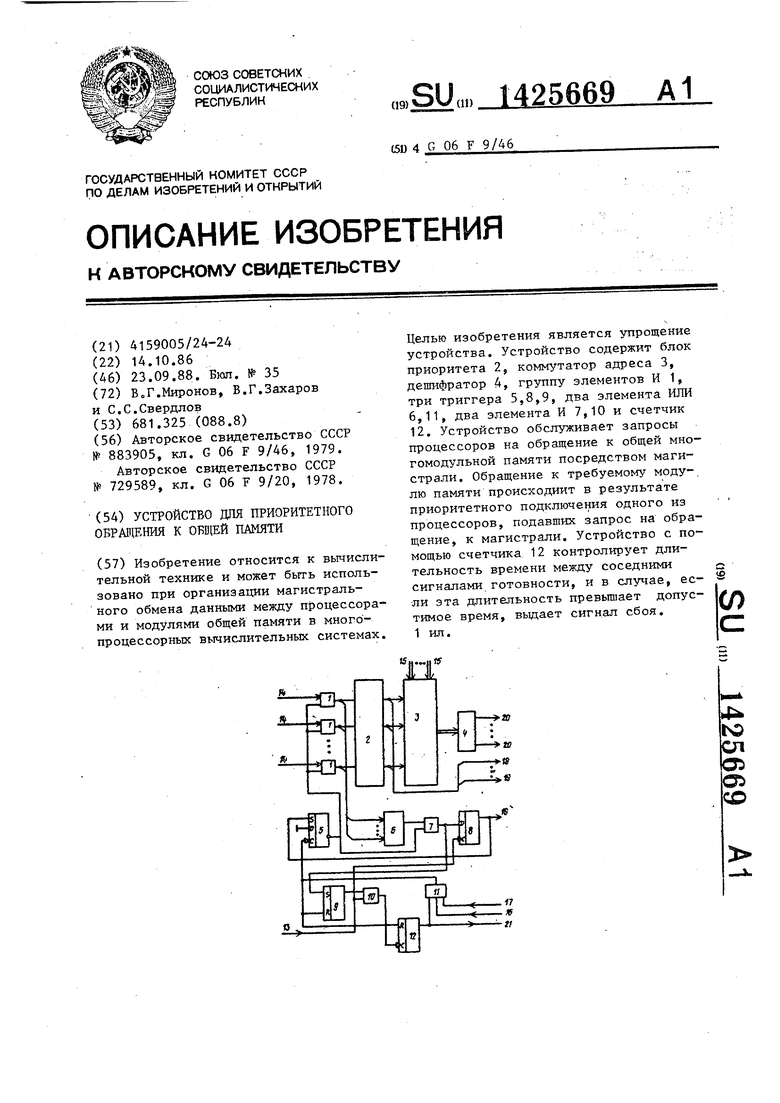

; На чертеже изображена функциональ- схема устройства. Устройство содержит группу элемен- ifoB И 1, блок 2 приоритета, коммута- iJop 3 адреса, дешифратор 4, первьй триггер 5, первый элемент ИЛИ 6, пер- 1ьй элемент И 7, третий триггер 8, второй триггер 9, второй элемент И 10, второй элемент ИЛИ 11, счетчик 12, вход 13 сигнализации, входы 14 з|апросов, адресные входы 15, входы 16 и 17 сигналов начальной установки и готовности памяти, выход 18 общего сигнала обращения, выходы 19 сигналов подтверждения запросов, выходы 20 обращения, выходы 21 сигнала сбоя.

По входу 13 в устройство подаются с|игналы синхронизации для работы счетчика 12 и триггера 8. По входам 14 на первые входы группы элементов И| поступают сигналы запросов на обра- щЬние к общей памяти от процессоров. Пр информационным входам 15 на коммутатор 3 адреса поступают коды номеров модулей памяти от процессоров вместе с сигналами запросов. По входу 16 в устройство поступает сигнал началь- нрй установки от процессоров. По вхо- Д 17 в устройство поступает сигнал готовности о.т рабочего модуля памяти. По выходу 18 с триггера 8 вьщается в памяти сигнал обращения, Ло выходам 19 из блока 2 вьщаются сигналы подтверждения запроса для инфорМаци- ойного подключения к магистралям процессоров и для снятия собственного запроса. По выходам 20 с де1|1ифратора А выдаются сигналы обращения к модулям памяти для запуска их в работу. По выходу 21 с выхода счетчика 12 выдается сигнал сбоя в случае, если время ожидания сигнала готовности превышает допустимое. Сигнал готовности является обобщенным сигналом памяти и образуется путем логического сложения индивидуальных сигналов готовности от каждого модуля памяти. Триггер 5 задает режим работы устрой™ ства, триггер 8 служит для формирования общего сигнала обращения, а триггер 9 задает режим работы счетчика 12

0

5

0

5

Устройство работает следугацим образом.

После прихода сигнала начальной установки по входу 16 триггер 5 устанавливается в нулевое состояние и от- крьшает группу элементов И 1 и элемент И 7. В результате этого устройство готово для приема и обработки сигналов запроса. При необходимости обращения к общей памяти процессор выдает в устройство сигнал запроса и адрес требуемого модуля памяти соответственно на входы 14 и 15. В случае появления на входах 14 указанных сигналов (в виде логических единиц) в любой комбинации они проходят через группу элементов И 1 и поступают на входы блока 2 и элемента ИЛИ 6. Соответственно самому приоритетному запросу блок 2 по соответствующему выходу выдает сигнал подтверждения запроса, который поступает на самый приоритетный процессор, подавший запрос. Кроме того, по этому сигналу коммутатор 3 пропускает на вход дешифратора 4 соответствующий адрес модуля памяти, который продешифруется в сигнал обращения к адресному.модулю.

Кроме того, как указывалось ранее, наличие хотя бы одного сигнала запроса с помощью элементов ИЛИ. 6, И 7 . обеспечивает сигнал в виде логической единицы на D-входе триггера 8 и S-входе триггера 9, В результате этого триггер 8 по ближайшему синхроимпульсу устанавливается в 1, образуя на выходе-18 обобщенньй сигнал обращения и одновременно установив в 1 триггер 5. После этого внешние запросы заблокированы, а триггер 8 подготовлен к сбросу по следующему синхроимпульсу, приходящему на вход 13.

Обслзгживаемый процессор, получив ответный сигнал подтверждения запро5 са, подключается к информационной магистрали, а затем снимает свой запрос. Кроме того, триггер 9, установившись в 1, посредством элемента И 10 включает в работу счетчик 12,

0 на счетньй вход которого через элемент И 10 проходят синхроимпульсы с входа 13, Счетчик рассчитан на оп- ределенньй интервал времени, обычно превосходящий реальньй интервал вре5 мани между соседними сигналами готовности. В случае отсутствия очередного сигнала готовности или его существенной задержки счетчик своим выходным сигналом запускает новьй цикл ра0

5

0

боты устройства и вьщает на выход 21 сигнал сбоя ЗУ, который может быть заведен на систему прерывания одного из процессоров.

Если очередной сигнал готовности приходит вовремя, то он дает начало очередному циклу устройства, одновременно сбрасывая с помощью элемента ИЛИ 11 триггер 9 и счетчик 12.

Форм у л а изобретения Устройство для приоритетного обра

щения к общей памяти, содержащее блок приоритета, выходы которого соединены с выходами подтверждения запросов устройства и с управляющими входами коммутатора адреса, выходы которого соединены с входами дешифратора, выходы которого являются выхо дами обращения устройства, входы запросов устройства соединены с первыми входами соответствующих элементов И группы, вькоды которых соединены с входами блока приоритета, информационные входы коммутатора адреса являются адресными входами устройства, отличающееся тем, что, с целью упрощения устройства, оно содержит два элемента ИЛИ, два элемента

0

5

5

0

И, три триггера и счетчик, пртгем вторые входы элементов И группы соединены с.инверсным выходом первого триггера и первым входом первого элемента И, а выходы элементов И группы соединены с входами первого элемента ИЛИ, выход которого соединен с вторым входом первого элемента И, выход которого соединен с S-входом второго триггера и П-входом третьего триггера, выход которого соединен с выходом общего сигнала обращения устройства и с S-входом первого триггера, С-вход третьего триггера соединен с входом синхронизации устройства и первым входом второго элемента И, второй вход которого соединен с единичным выходом второго триггера, а выход - соединен со счетным входом счетчика, выход которого соединен с вькодом сигнала сбоя устройства и с первым входом второго элемента ИЛИ, второй вход которого соединен с входом начальной установки устройства, третий вход второго элемента ИЛИ сое динен с входом сигнала готовности памяти устройства, а выход соединен с входом сброса счетчика, входом сброса второго триггера и с С-входом первого триггера, D-вход которого соединен с потенциалом земля устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропроцессорное устройство обработки данных | 1982 |

|

SU1291999A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Устройство для обмена данными в вычислительной сети | 1988 |

|

SU1599864A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1984 |

|

SU1332326A1 |

| Устройство для приоритетного обращения к общей многомодульной памяти | 1988 |

|

SU1539786A1 |

| Устройство для приоритетного обращения процессоров к общей памяти | 1979 |

|

SU883905A2 |

| Устройство для обмена информацией | 1983 |

|

SU1198528A1 |

| УСТРОЙСТВО ОБМЕНА ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ | 1991 |

|

RU2020571C1 |

| Устройство микропроцессорного управления и обработки информации | 1979 |

|

SU947867A1 |

| Устройство для сопряжения | 1980 |

|

SU926645A2 |

Изобретение относится к вьиисли- тельной технике и может быть использовано при организации магистрального обмена данными между процессорами и модулями общей памяти в многопроцессорных вьгчислительных системах. Целью изобретения является упрощение устройства. Устройство содержит блок приоритета 2, коммутатор адреса 3, дешифратор 4, группу элементов И 1, три триггера 5,8,9, два элемента ИЛИ 6,11, два элемента И 7,10 и счетчик 12. Устройство обслуживает запросы процессоров на обращение к общей мно гомодульной памяти посредством магистрали. Обращение к требуемому модулю памяти происходиит в результате приоритетного подключения одного из процессоров, подавших запрос на обра щение, к магистрали. Устройство с по мощью счетчика 12 контролирует длительность времени между соседними сигналами готовности, и в случае, ее ли эта длительность превышает допус тимое время, выдает сигнал сбоя. 1 ил. ГГ - ф (Л 4:: Ю Р О5 о: со

| Устройство для приоритетного обращения процессоров к общей памяти | 1979 |

|

SU883905A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для формирования адреса | 1978 |

|

SU729589A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-09-23—Публикация

1986-10-14—Подача