Изобретение относится к вычислительной технике, в частности к устройствам для прерывания программ, и может быть использовано при построении вычислительных систем обработки данных. Известно устройство для управления обслуживания запросов в порядке поступления, содержащее блок управления, шифратор, регистр, элемент ИЛИ, кангипы, а в каждом канале блок очередности Tl. Наиболее близким к предлагаемому по технической сущности и достигаемому результату является многоканаль ное устройство приоритетных прерываний с автоматической выработкой кода приоритетной заявки, содержащее блок управления, элемент ИЛИ, шифратор, регистр, каналы, а в канале блок очередности, коммутатор и элемент ИЛИ 2. Однако известные устройства обладают низкой надежностью. Цель изобретения - повышение надежности устррйства. Поставленная цель достигается тем, что в многоканальное устройство приоритетных прерываний, содержащее первый элемент ИЛИ, шифратор, регист п-каналов, а в каждом канале узел очередности, причем первая группа выходов узла очередности каждого канала соединена с соответствующей группой входов шифратора, группа выходов шифратора соединена с группой информационных входов регистра, группа разрядочных выходов регистра является группой информационных входов устройства, первая группа входов узла очередности каждого канала является соответствукидей группой информационных входов устройства, выход первого элемента ИЛИ является первым выходом устройства, введено группу элементов И, группу элементов ИЛИ, второй элемент ИЛИ, а в каждом канале блок местного управления и счетчик, причем вторая rpynjna. входов узла очерёдности каждого i-ro (...n);( канала, кроме п-ГО-, соединена со второй группой выходов узла очередности (i+1) канала, вторая группа входов узла очередности п-го канала соединена со второй группой выходов первого канала, третья группа входов узла очередности каждого i-го канала кроме первого соединена с третьей группой выходов урла очередности (i+i)-ro канала третья группа входов

узла очередности первого,канала соединена с третьей группой выходов узла очередности п-го канала, первый вход узла очередности каждого канала соединен с первым выходом блока местного управления своего канала, выход каждого i-ro элемента И группы кроме п-го, соединен со вторыми входами узлов очередности 1-го канала и с третьим входом узла очередности первого канала соединен со вторым входом узла очередности п-го канала и с выходом п-го элемента И группы, четвертый вход узла очередности каждого i го канала, кроме первого, соединен со вторым выходом блока местного управления (i-l)-ro канала, четвертый вход узла очередности первого канала соединен со вторым выходом блока местного управления п-го канала, первый выход уала очередности каждого 1-го канала, кроме первого, соединен с первым входом (i-l)-ro элемент И группы, первый выход узла очередности первого канала соединен с первым входом п-го элемента И группы, второй выход узла очередности каждого 1-го канала соединен со вторым входом 1-го элемента И группы, третий выход узла очередности каждого канала соединен с первым входом блока местного управления своего канала и с соответствующим входом первого элемента ИЛИ, второй блока местного угфавления каждого i-ro канала, кроме первого, соединен с третьим №лхолом блока местного управления (t-l)-ro канала, втоцрй вход блока местного управления первого канала является входом считывания устройства, выход каждого j-ro .(...(п-1) элемента ИЛИ группы соединен с третьим входом блока местного управления соответствующего канала, четвертый выход блока местного управления каждого канала соединен с соответствующим входом второго элемента ИЛИ, пятый выход блока местного управления каждого канала соединен с первым управляющим входом счетчика своего канала, второй управляющий вход счетчика каждого )--го канала соединен с выходом i-ro элемента И группы первый вход каждого j-ro элемента ИЛИ группы соединен с выходом (j+1) элемента ИЛИ группы,второй .вход каждого j-го элемента ИЛИ группы соединен с шестым выходом блока местного управления последукядего канала, группа выходов -счетчика каждого канала соединена с группой входов блока местного управления своего канала выход второго элемента ИЛИ является вторым выходом устройства.

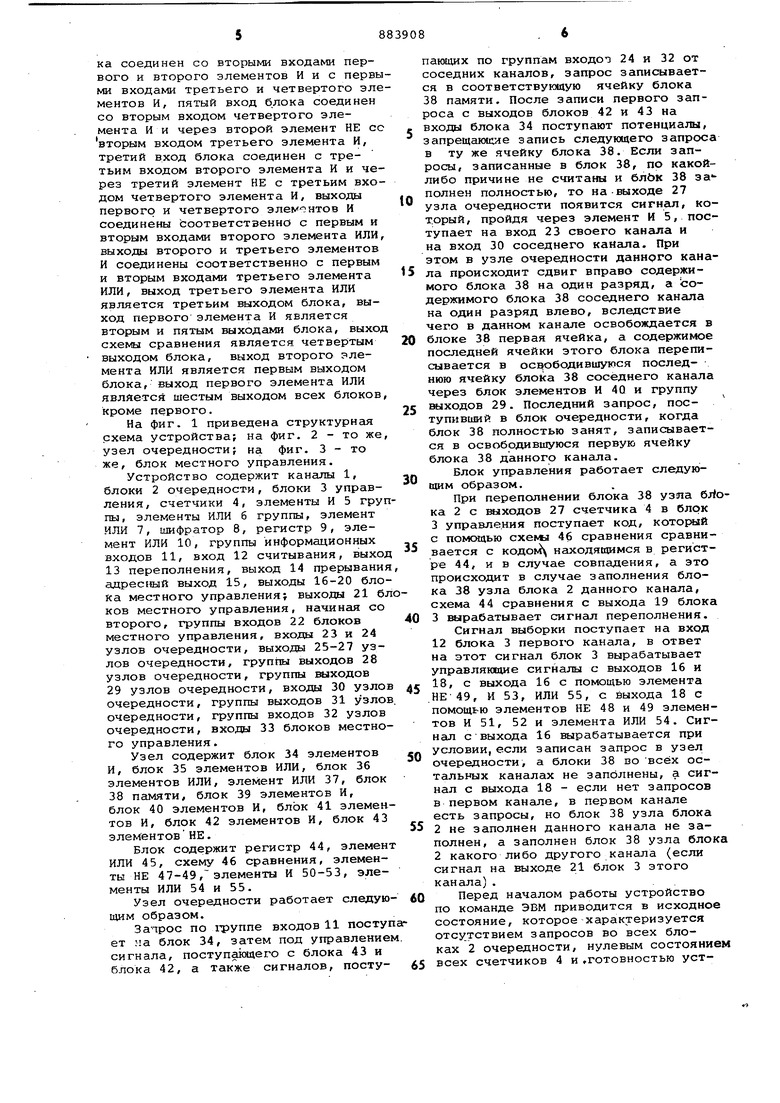

При этом, узел очередности содержит блок элементов НЕ, блок памяти, два блока элементов ИЛИ, элемент ИЛИпять блоков элементов И, причем первая группа входов первого блока элементов И является первой группой входов узла, вторая группа входов первого блока элементов И соединена с группой выходов второго блока элементов И, первая группа выходов блока памяти соединена с группами входов . третьего и четвертого блоков элементов И, вторая группа выходов блока памяти соединена с группой входов пятого блока элементов И, третья группа выходов блока памяти соединена с группой входов второго блока элементов И, группа выходов второго блока элементов И соединена с группой входов блока элементов НЕ, группа выходов которого соединена с третьей группой входов первого блока элементов И первая и вторая группы выходов первого блока элементов И соединены соответственно с первымигруппами входов первого и вторюго блоков элементов ИЛИ, третья группа выходов первого блока элекюнтов И соединена с первой группой входов блока памяти, вторая и третья группы входов которого соединены с группами выходов соответственно первого н второго блоков элементов ИЛИ, вторая группа входов узла соединена с группой входов элемента ИЛИ и со второй группой входов второго блока элементов ИЛИ, вторая группа входов первого блока элементов ИЛИ соединена с третьей группой входов узла, выход блока элементов НЕ является первым выходом узла, первый вход узла соединен с входом четвертого блока элементов И и с входом элемента ИЛИ, первый управляющий вход блока памяти является третьим входом узла, второй управляющий вход блока памяти соединен с выходом элемент.а ИЛИ, группы выходов третьего и четвертого блоков элементов И являются соответственно второй и первой группами выходов узла, четвертый вход узла соединен с входом третьего блока элементов И, первый и второй выходы второго блока элементов И являются соответственно вторлм и третьим выходами узла, второй вход узла соединен с входом пятого блока элементов И, группа выходов пятого блока элементов И является третьей группой выходов узла.

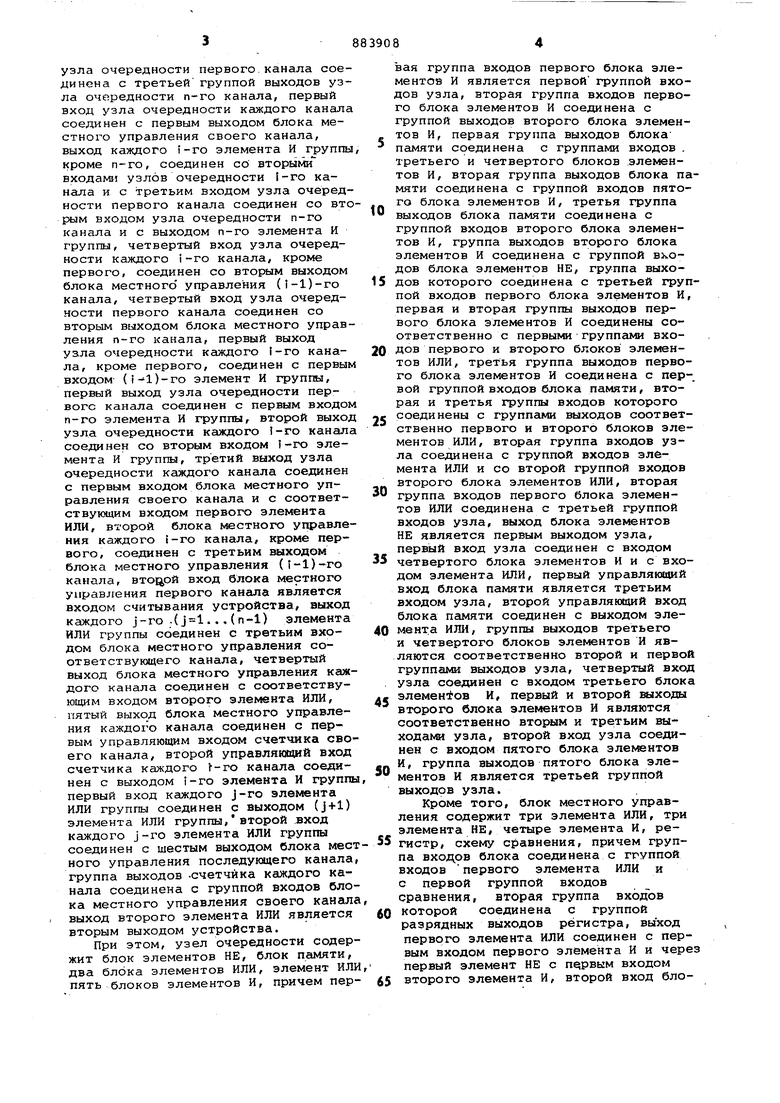

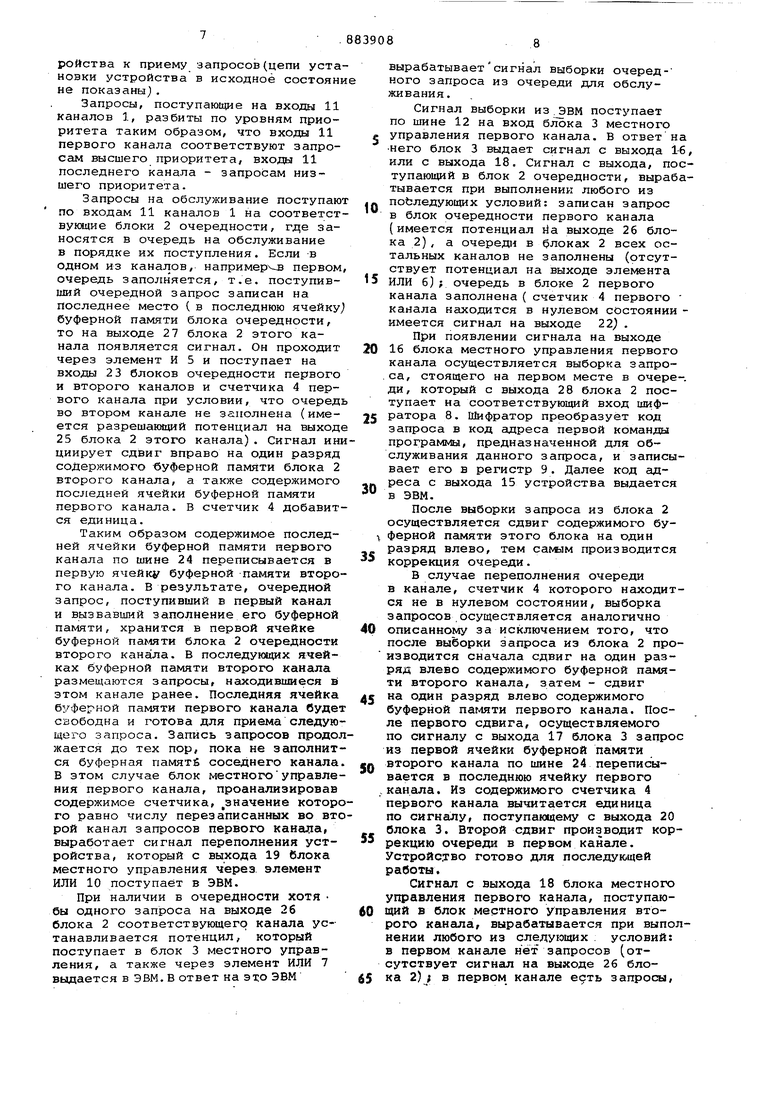

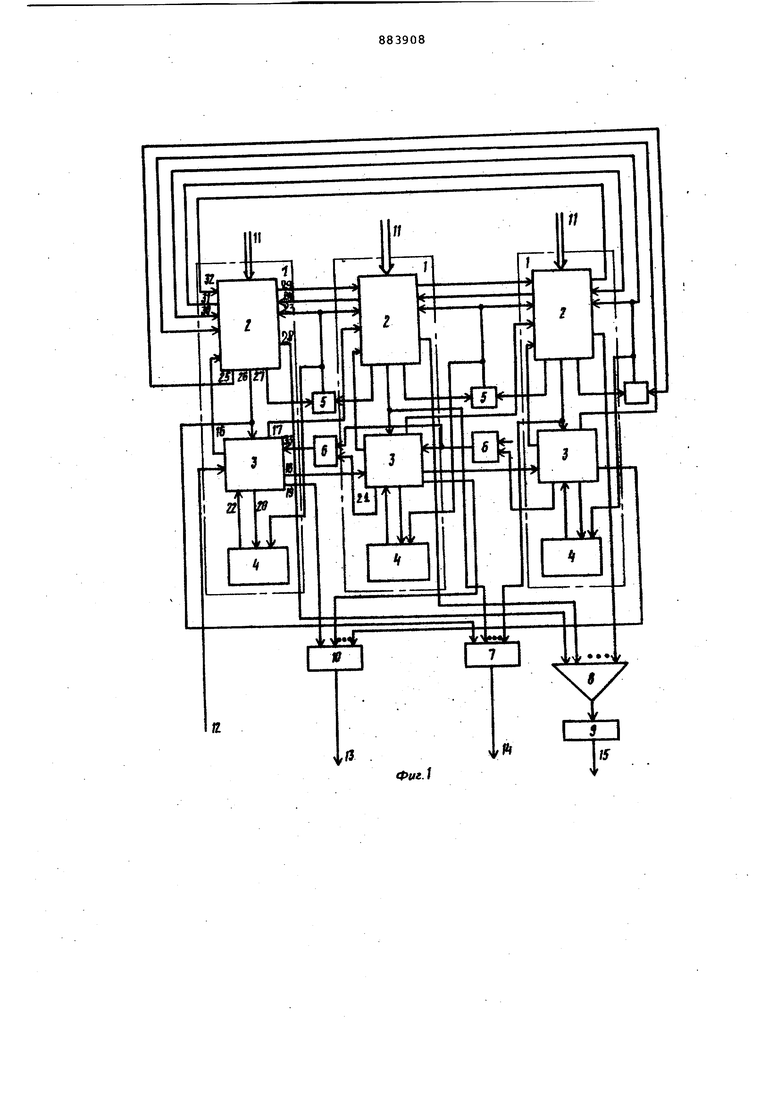

Кроме того, блок местного управления содержит три элемента ИЛИ, три элемента НЕ, четыре элемента И, регистр, схему сравнения, причем группа входов блока соединена с группой входов первого элемента ИЛИ и с первой группой входов сравнения, вторая группа входов которой соединена с группой разрядных выходов регистра, выход первого элемента ИЛИ соединен с первым входом первого элемента И и чере первый элемент НЕ с первым входом второго элемента И, второй вход блока соединен со вторыми входами первого и второго элементов И и с первы ми входами третьего и четвертого эле ментов И, пятый вход блока соединен со вторым входом четвертого элемента И и через второй элемент НЕ се вторым входом третьего элемента И, третий вход блока соединен с третьим входом второго элемента И и через третий элемент НЕ с третьим вхо дом четвертого элемента И, выходы первого и четвертого элем- нтов И соединены соответственно с первым и вторым входами второго ИЛИ выходы второго и третьего элементов И соединены соответственно с первым и вторым входами третьего элемента ИЛИ, выход третьего элемента ИЛИ является третьим выходом блока, выход первого элемента И является вторым и пятым выходами блока, выход схемы сравнения является четвертым выходом блока, выход второго элемента ИЛИ является первым выходом блока, выход первого элемента ИЛИ является шестым выходом всех блоков кроме первого. На фиг. 1 приведена структурная схема устройства; на фиг. 2 - то же узел очередности; на фиг. 3 - то же, блок местного управления. Устройство содержит каналы 1, блоки 2 очередности, блоки 3 управления, счетчики 4, элементы И 5 гру пы, элементы ИЛИ б групги, элемент ИЛИ 7, шифратор 8, регистр 9, элемент ИЛИ 10, группы информационных входов 11, вход 12 считывания, выхо 13 переполнения, выход 14 прерывани адресный выход 15, выходы 16-20 бло ка местного управления; выходы 21 б ков местного управления, начиная со второго, группы входов 22 блоков местного управления, входы 23 и 24 узлов очередности, выходы 25-27 узлов очередности, группы выходов 28 узлов очередности, группы идходов 29 узлов очередности, входы 30 узло очередности, группы выходов 31 узло очередности, группы входов 32 узлов очередности, входы 33 блоков местно го управления. Узел содержит блок 34 элементов И, блок 35 элементов ИЛИ, блок 36 элементов ИЛИ, элемент ИЛИ 37, блок 38 Пс1Мяти, блок 39 элементов И, блок 40 элементов И, блок 41 элемен тов И, блок 42 элементов И, блок 43 элементов НЕ. Блок содержит регистр 44, элемен ИЛИ 45, схему 46 сравнения, элементы НЕ 47-49, элементы И 50-53, элементы ИЛИ 54 и 55. Узел очередности работает следую щим образом. Запрос по 1-руппе входов 11 поступ ет ма блок 34, затем под управление сигнала, поступакядего с блока 43 и блока 42, а сигналов, поступающих по группам входот 24 и 32 от соседних каналов, запрос записывается в соответствующую ячейку блока 38 памяти. После записи первого запроса с выходов блоков 42 и 43 на входы блока 34 поступают потенциалы, запрещаювие запись следующего запроса в ту же ячейку блока 38. Если запросы, записанные в блок 38, по какойлибо причине не считаны и блЬк 38 за полнен полностью, то на выходе 27 узла очередности появится сигнал, который, пройдя через элемент К 5, поступает на вход 23 своего канала и на вход 30 соседнего канала. При этом в узле очередности данирго канала происходит сдвиг вправо содержимого блока 38 на один разряд, а содержимого блока 38 соседнего канала на один разряд влево, вследствие чего в данном кангше освобождается в блоке 38 первая ячейка, а содержимое последней ячейки этого блока переписывается в освободившуюся послед- нюю ячейку блоКа 38 соседнего канала через блок элементов И 40 и группу выходов 29. Последний запрос, поступивший в блок очередности, когда блок 38 полностью занят, записывается в освободившуюся первую ячейку блока 38 данного канала. Блок управления работает следующим образом. При переполнении блока 38 узла 6jioка 2 с выходов 27 счетчика 4 в блок 3 управле.ния поступает код, который с помощью схемл 46 сравнения сравнивается с кодог находящимся в регистре 44, ив случае совпадения, а это происходит в случае заполнения блока 38 узла блока 2 данного канала, схема 44 сравнения с выхода 19 блока 3 вырабатывает сигнал переполнения. Сигнал выборки поступает на вход 12 блока 3 nepBoio канала, в ответ на этот сигнал блок 3 вырабатывает управляющие сигналы с выходов 16 и 18, с выхода 16 с помощью элемента НЕ49, И 53, ИЛИ 55, с выхода 18 с помощью элементов НЕ 48 и 49 элементов И 51, 52 и элемента ИЛИ 54. Сигнал с выхода 16 вырабатывается при условии, если записан запрос в узел очередности, а блоки 38 во всех остальных каналах не заполнены, а сигнал с выхода 18 - если нет запросов в первом канале, в первом канале есть запросы, но блок 38 узла блока 2 не заполнен данного канала не заполнен, а заполнен блок 38 узла блока 2 какого либо другого канала (если сигнал на выходе 21 блок 3 этого канала). Перед началом работы устройство по команде ЭВМ приводится в исходное состояние, которое характеризуется отсутствием запросов во всех блоках 2 очередности, нулевым состоянием всех счетчиков 4 и ,готовностью устройства к приему запросов(цепи установки устройства в исходное состояни не показаны).

Запросы, поступающие на входы 11 каналов 1, разбиты по уровням приоритета таким образом, что входы 11 первого канала соответствуют запросам высшего приоритета, входы 11 последнего канала - запросам низшего приоритета.

Запросы на обслуживание поступают по входам 11 каналов 1 на соответствующие блоки 2 очередности, где заносятся в очередь на обслуживание в порядке их поступления. Если в одном из каналов, например -э первом, очередь заполняется, т.е. поступивший очередной запрос записан на последнее место ( в последнюю ячейку буферной памяти блока очередности, то на выходе 27 блока 2 этого канала появляется сигнал. Он проходит через элемент И 5 и поступает на входы 23 блоков очередности первого и второго каналов и счетчика 4 первого канала при условии, что очередь во втором канале не заполнена (имеется разрешаюйдий потенциал на выходе 25 блока 2 этого канала). Сигнал инициирует сдвиг вправо на один разряд содержимого 5уферной памяти блока 2 второго канала, а также содержимого последней ячейки буферной памяти первого канала. В счетчик 4 добавится единица.

Таким образом содержимое последней ячейки буферной памяти первого канала по шине 24 переписывается в первую ячейку буферной памяти второго канала. В результате, очередной запрос, поступивший в первый канал и вызвавший заполнение его буферной памяти, хранится в первой ячейке буферной памяти блока 2 очередности второго канала. В последующих ячейках буферной памяти второго канала размещаются запросы. Находившиеся в этом канале ранее. Последняя ячейка буферной памяти первого канала будет свободна и готова для приема следующего запроса. Запись запросов продолжается до тех пор, пока не заполнится буферная памяти соседнего канала. В этом случае блок местногоуправления первого канала, проанализировав содержимое счетчика, значение которого равно числу перезаписанных во второй канал запросов первого канала, выработает сигнал переполнения устройства, который с выхода 19 блока местного управления через, элемент ИЛИ 10 поступает в ЭВМ.

При наличии в очередности хотя бы одного запроса на выходе 26 блока 2 соответствующего канала устанавливается потенцил, который поступает в блок 3 местного управления, а также через элемент ИЛИ 7 выдается в ЭВМ. В ответ на это ЭВМ

вырабатываетсигнал выборки очередного запроса из очереди для обслуживания.

Сигнал выборки из .ВМ поступает по шине 12 на вход блока 3 местного управления первого канала. В ответ на него блок 3 выдает сигнал с выхода 1-6 или с выхода 18. Сигнал с выхода, поступающий в блок 2 очередности, вырабатывается при выполнении любого из последующих условий: записан запрос в блок очередности первого канала (имеется потенциал ria выходе 26 блока 2) , а очереди в блоках 2 всех остальных каналов не заполнены (отсутствует потенциал на выходе элемента ИЛИ 6); очередь в блоке 2 первого канала заполнена ( счетчик 4 первого канала находится в нулевом состоянии имеется сигнал на выходе 22).

При появлении сигнала на выходе 16 блока местного управления первого канала осуществляется выборка запро. са, стоящего на первом месте в очереди, который с выхода 2В блока 2 поступает на соответствующий вход шифратора 8. Шифратор преобразует код запроса в код адреса первой команды программы, предназначенной для обслуживания данного запроса, и записывает его в регистр 9. Далее код адреса с выхода 15 устройства выдается в ЭВМ.

После выборки запроса из блока 2 осуществляется сдвиг содержимого буферной памяти этого блока на один разряд влево, тем самым производится коррекция очереди.

В случае переполнения очереди в канале, счетчик 4 которого находится не в нулевом состоянии, выборка запросов осуществляется аналогично описанному за исключением того, что после выборки запроса из блока 2 производится сначала сдвиг на один разряд влево содержимого буферной памяти второго канала, затем - сдвиг на один разряд влево содержимого буферной памяти первого канала. После первого сдвига, осуществляемого по сигналу с выхода 17 блока 3 запрос из первой ячейки буферной памяти второго канала по шине 24 переписывается в последнюю ячейку первого .канала. Из содержимого счетчика 4 первого канала вычитается единица по сигналу, поступающему с выхода 20 блока 3. Второй сдвиг производит коррекцию очереди в первом канале. Устройство готово для последующей работы.

Сигнал с выхода 18 блока местного управления первого канала, поступающий в блок местного управления второго канала, вырабатывается при выполнении любого из следующих . условий: в первом канапе нет запросов (отсутствует сигнал на выходе 26 блока 2) ; в первом канале есть запросы. ,но очередь не заполнена ( есть сигнал на выхсле 26 блока 2, нет сигнала на выходе 22 счетчика А) , а очередь 1В одной из каналов устройства заполнена (есть сигнал на выходе 21 блока 3 1-го канала ,N). Сигнал выборки 18 поступает в блок местного управления второго канала. Работа второго и последующих каналов в этом случае аналогична описанному. Применение изобретения позволяет уменьшить вероятность потери запросов и таим образом повысить надежность устройства. Формула изобретения 1. Многоканальное устройство приоритетных прерываний, содержащее первый элемент ИЛИ, шифратор, регист п-каналов, а в каждом канале узел очередности, причем первая группа выходов узла очередности КЗЕЖДОГО канала соединена с соответствующей группой входов шифратора, группа выходов шифратора соединена с группой информационных входов регистра, груп па разрядных выходов регистра являет ся группой информационных входов уст ройства, первс1Я группа входов узла очередности каждого канала является соответствующей группой информационных входов устройства, выход первого элемента ИЛИ является первым выходом устройства, отличающееся тем, что, с целью повышения надежности , устройство содержит группу элементов И, группу элементов ИЛИ, второй элемент ИЛИ,: а в каждом кана ле блок местного управления и счетчик, причем вторая группа входов узла очередности каждого i-ro (... канала, кроме п-го, соединена со второй группой выходов узла очередности ( 14-1) канала, вторая группа входов узла очередности п-го канала соединена со второй группой выходов первого канала, третья группа входов узла очередности каждого i-ro канал кроме первого соединена с третьей группой выходов узла очередности (i+l)ro канала,третья группа входов узла очередности первого канала соединена с третьей группой выходов узла очередности п-го канала, первый вход узла очередности каждого канал соединен с первым выходом блока местного управления своего канала. выход каждого i-ro элемента И группы, кроме п-го, соединен со вторыми входами узлов очередности i-ro кана ла и с третьим входом узла очередно ти первого канала соединен со вторы входом узла очередности п-го канала и с выходом пгго элемента И группы, четвертый вход узла очередности каж дого i-ro канала, кроме первого, соединен со вторым выходом блока местного управления (1-1)-го кансша четвертый вход узла очередности первого канала соединен со вторим выходом блока местного управления п-го канала, первый выход узла очередности каждого i-ro канала, кроме первого, соединен с первым входом (i-l)-ro элемента И группы, первый выход узла очередности первого канала соединен с первым входом п-го элемента И группы, второй выход узла Охередности каждого ч-го канала соединен со вторым входом I-го элемента И группы, третий выход узла очередности каждого канала соединен с первым входом блока местного управления своего канала и с соответствукицим входом первого элемента ИЛИ, второй вход местного управления каждого i-ro канала, кроме первого, соединен с третьим выходом блока местного управления (l-l)-ro канала, .второй вход блока местного управления первого канала является входом считы-вания устройства, выход каждого j-ro (. .. (п-1)) элемента ИЛИ группы соединен с третьим входом блока местного управления соответствующего канала, четвертый выход блока местного управления каждого канала соединен с соответствующим входом второго элемента ИЛИ, пятый выход блока местного управления каждого канала соединен с первым управляющим входом счетчика своего канала, второй управляющий вход счетчика каждого i-ro канала соединен с выходом I-го элемента И группы, первый вход Кс1ждого j-ro элемента ИЛИ -групгы соединен с выходом (j+1) элемента ИЛИ группы, второй вход каждого j-ro элемента ИЛИ группы соединен с шестым выходом блока местного управления последукадего канала, группа выходов счетчика каждого канала соединена с группой входов блока местного управления своего канала, выход второго элемента ИЛИ является вторым выходом устройства. 2. Устройство по п.1, отличающееся тем, что узел очередности содержит блок элементов НЕ, блок памяти, два блока элементов ИЛИ, элемент ИЛИ, пять- блоков элементов И, причем первая группа входов первого блока элементов И является первой группой входов уз-, ла, вторая группа входов первого блока элементов И соединена с группой выходов второго блока элементов И, первая группа -выходов блока памяти соединена с группами входов третьего и четвертого блоков элементов И, вторая группа выходов блока памяти соединена с группой входов пятого блока элементов И, третья группа выходов блока памяти соединена с группой входов второго блока элементов И, группа вэ1ходов второго блока элементов И соединена с группой входов блока элементов НЕ, группа выходов которого соединена с третьей группой входов первого блока элементов И, первая и вторая группы выходов первого блока элементов И соединены соответственно с первыми груп пами входов первого и второго блоков элементов ИЛИ, третья группа выходов первого блока элементов И соединена с первой группой вхоДОБ блока памяти, вторая и трет1 я группы входов которого соединены с группамр выходов соответственно пер вого и второго блоков элементов ИЛИ вторая группа входов узла соединена с группой входов элемента ИЛИ и со второй группой входов второго блока элементов ИЛИ, вторая группа входов первого блока элементов ИЛИ соедине на с третьей группой входов узла, выход блока элераюнтов НЕ является . первым выходом узла, первый вход уз ла соединен с входом четвертого блока элементов И и с входом элемен та ИЛИ, первый управлякнций вход блока памяти является третьим входом узла, второй управляющи-й вход блока памяти соединен с выходом эле мента ИЛИ, группы выходов третьего и четвертого блоков элементов И являются соответственно второй и первой группгили выходов узла, четвертый вход узла соединен с входом третьего блока элементов И, первый и второй выход второго блока элемен тов И являются соответственно вторым и третьим выходами узла, второй вход узла соэдинен с входом пятого блока элементов И, группа выходов п того блока элементов И является тре ей группой выходов узла. 3. Устройство по п.1, о т л и чающееся тем, что блок мест ного управления содержит три элемента ИЛИ, три элемента КЕ, четыре элемента И, регистр, схему сравнения, причем группа входов блока соединена с группой входов первого элемента ИЛИ и с первой группой входов схемы сравнения, вторая группа входов которой соединена с группой разрядных. кдходов регистра, выход первого элемента ИЛИ соединен с первым входом первого элемента И и через первый элемент НЕ с первым входом второго элемента И, второй вход блока соединен со вторыми входами первого и второго элементов И и с первыми входами Третьего и четвертого элементов И, пятый вход блока соединен со вторым входом четвертого элемента И и через второй элемент НЕ со вторым входом третьего элемента И, третий вход блока соединен с третьим входом второго элемента И и через третий элемент НЕ с третьим входом четвертого элемента И, выходы первого и четвертого элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выходы второго Н третьего элементов И соединены соответственно с первым и вторым входами третьего элемента ИЛИ, выход третьего элемента ИЛИ является третьим выходом блока, выход первого элемента И является вторым и пятым выходами блока, выход cxeNbi сравнения является четвертым выходом блока, выход второго элемента ИЛИ является первым выходом блока, выход первого элемента ИЛИ являтеся шестым выходом всех блоков, кроме первого. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 206891, кл. G 06 F 9/18, 1966. 2.Авторское свидетельство СССР № 548859, кл, G Об F 9/18, 1974 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Комбинированный канал | 1986 |

|

SU1405067A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1405063A2 |

| Многоканальное устройство для обмена информацией | 1984 |

|

SU1359781A1 |

| Устройство внешних каналов | 1988 |

|

SU1695313A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

| Многоканальное устройство динамического приоритета | 1981 |

|

SU970371A1 |

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство управления микропрограммной ЭВМ | 1989 |

|

SU1691840A1 |

Авторы

Даты

1981-11-23—Публикация

1980-01-21—Подача