05 00 СО 4

оэ

00

Изобретение относится к вычислительной технике и может быть использовано для контроля и диагностики неисправностей оперативной памяти конвейерного типа для высокопроизводительных вычислительных машин

Цель изобретения - упрощение устройст ва и повышение достоверности контроля

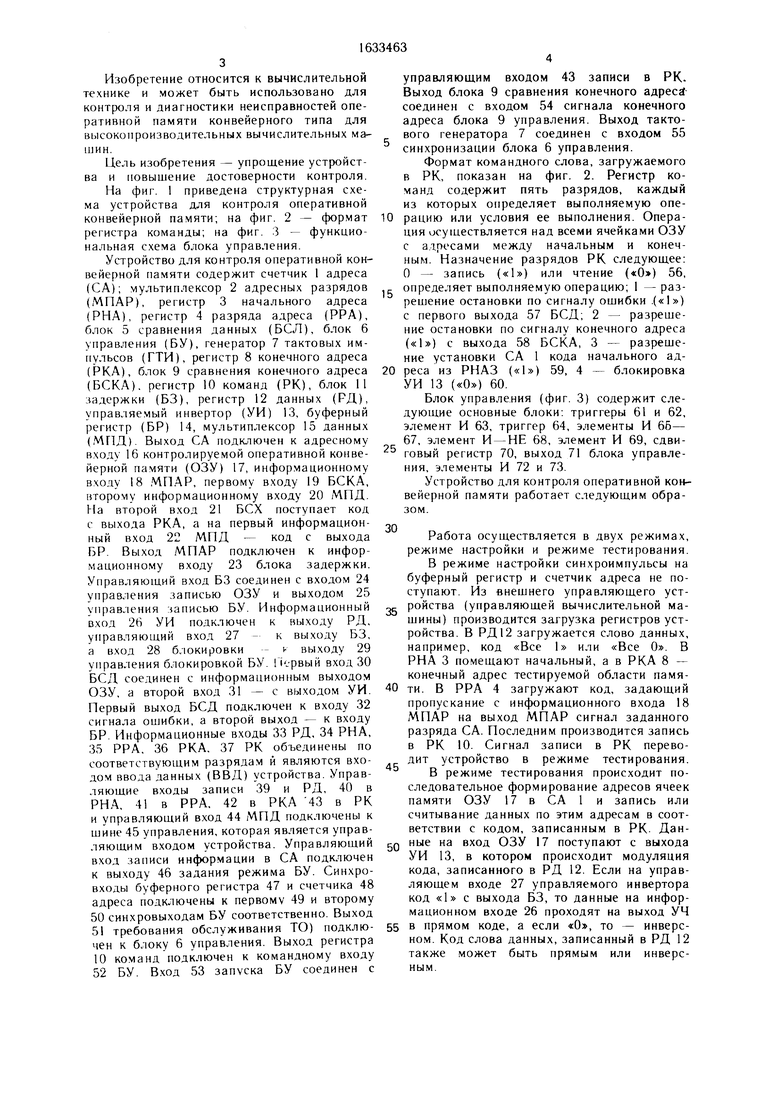

На фиг 1 приведена структурная схема устройства для контроля оперативной

управляющим входом 43 записи в РК. Выход блока 9 сравнения конечного адреса соединен с входом 54 сигнала конечного адреса блока 9 управления Выход тактового генератора 7 соединен с входом 55 синхронизации блока 6 управления

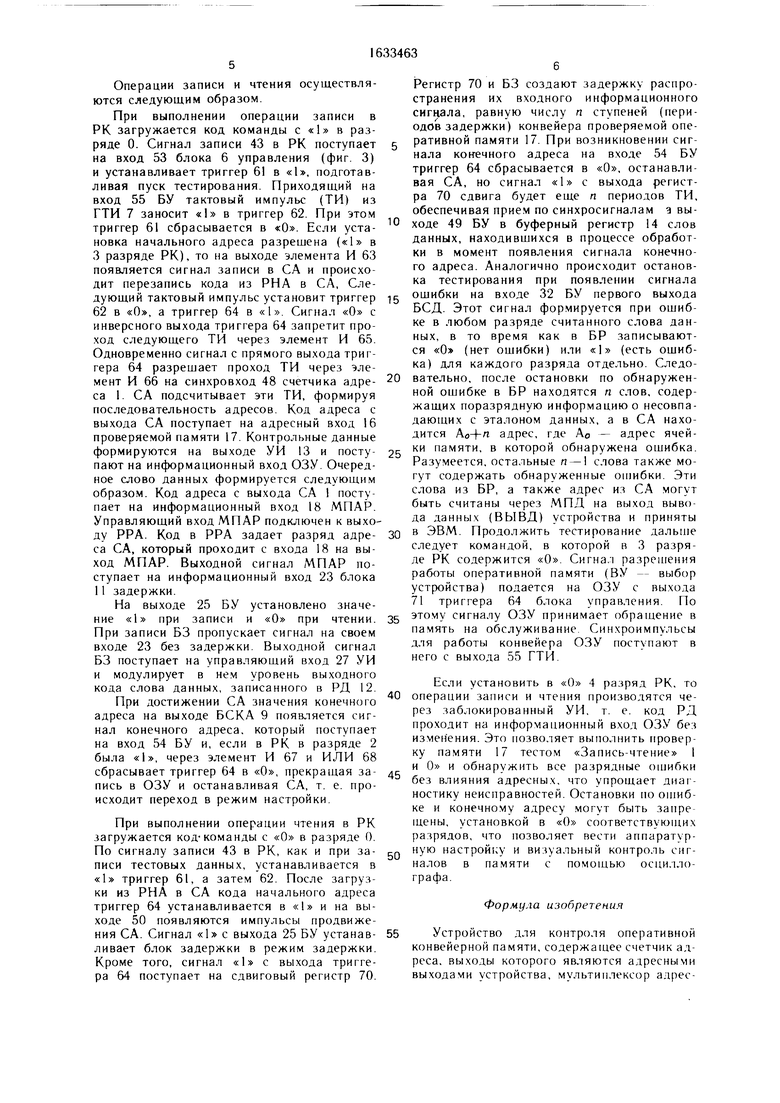

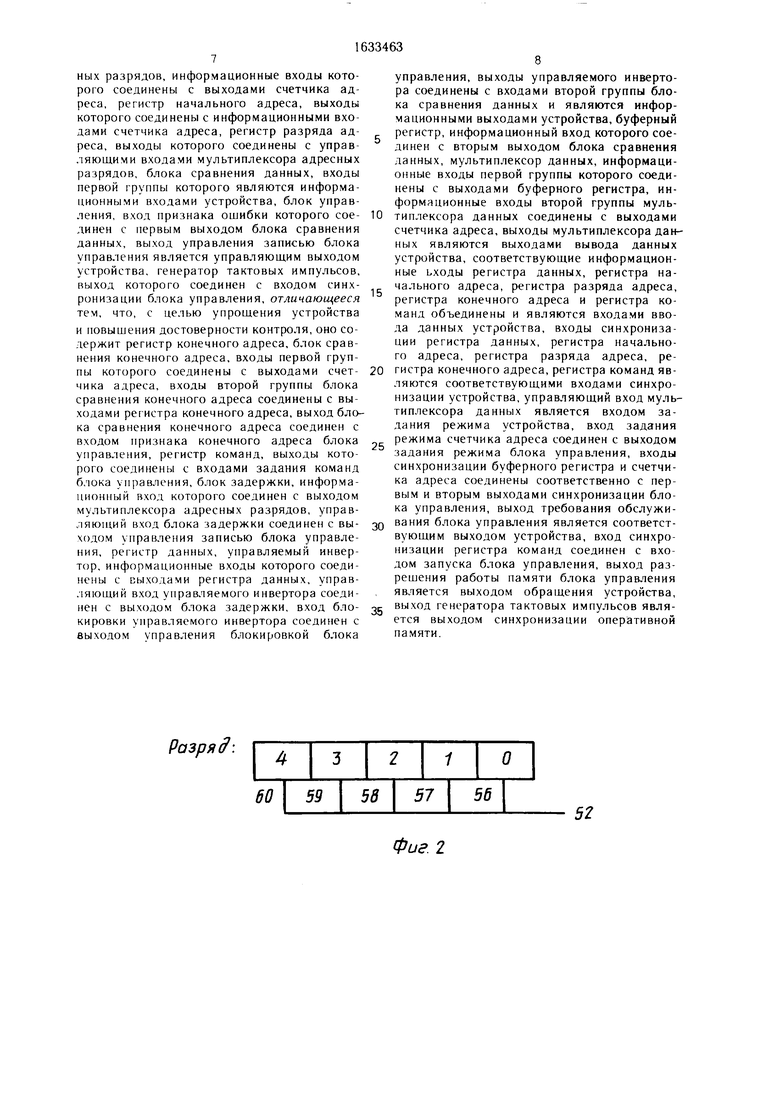

Формат командного слова, загружаемого в РК, показан на фиг 2 Регистр команд содержит пять разрядов, каждый из которых определяет выполняемую опеконвейерной памяти, на фиг 2 - формат 10 рацию или условия ее выполнения Опера- регистра команды, на фиг 3 - функциоция осуществляется над всеми ячейками ОЗУ нальная схема блока управления

Устройство для контроля оперативной конвейерной памяти содержит счетчик 1 адреса

с агресами между начальным и конечным Назначение разрядов РК следующее О - запись («1) или чтение («0) 56,

(СА), мультиплексор 2 адресных разрядовопределяет выполняемую операцию, 1 -раз(МПАР), регистр 3 начального адресарешение остановки по сигналу ошибки («1)

(РНА), регистр 4 разряда адреса (РРА),с первого выхода 57 БСД, 2 - разрешеблок 5 сравнения данных (БСЛ), блок 6 правления (БУ), генератор 7 тактовых импульсов (ГТИ), регистр 8 конечного адреса (РКА), блок 9 сравнения конечного адреса 20 реса из РНАЗ («1) 59, 4 - блокировка (БСКА), регистр 10 команд (РК), блок 11УИ 13 («О) 60

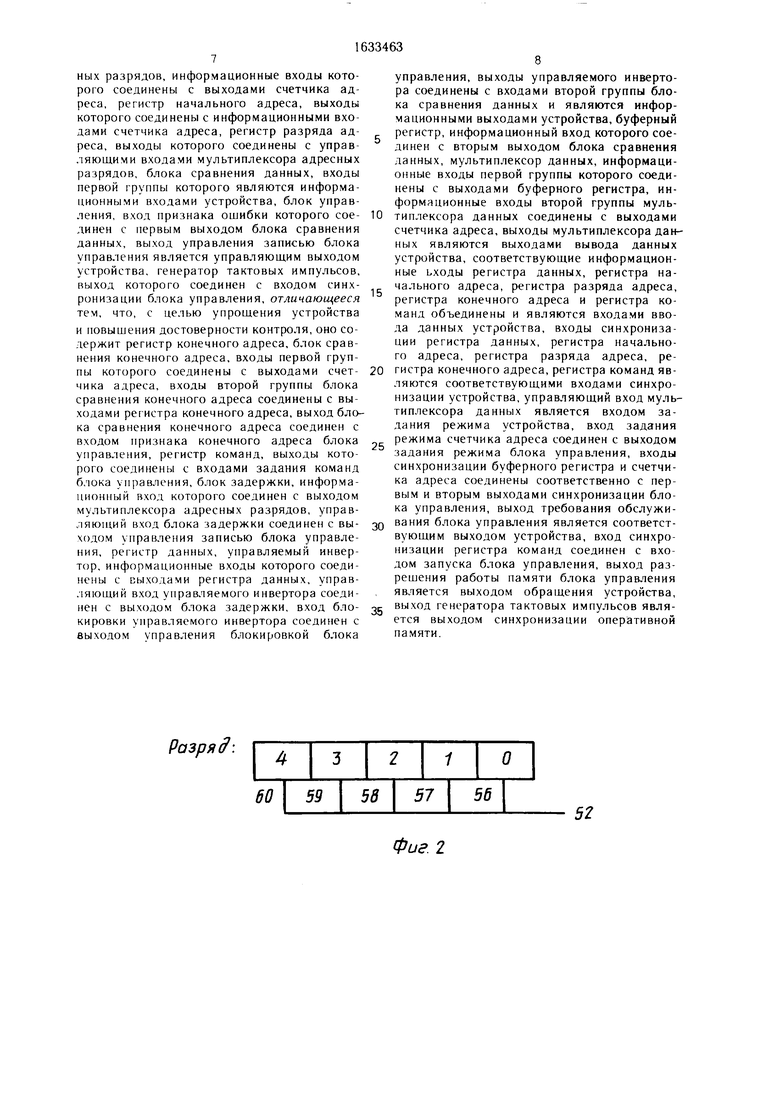

Блок управления (фиг 3) содержит следующие основные блоки триггеры 61 и 62, элемент И 63, триггер 64, элементы И 65- 67, элемент И - НЕ 68, элемент И 69, сдвиговый регистр 70, выход 71 блока управление остановки по сигналу конечного адреса («1) с выхода 58 БСКА, 3 - разрешение установки СА 1 кода начального ад адержки (БЗ), регистр 12 данных (РД), управляемый инвертор (УИ) 13, буферный регистр (БР) 14, мультиплексор 15 данных (МИД) Выход СА подключен к адресному входу 16 контролируемой оперативной конве- 25 йерной памяти (ОЗУ) 17, информационному вхочу 18 МПАР, первому входу 19 БСКА, второму информационному входу 20 МПД На второй вход 21 БСХ поступает код с выхода РКА, а на первый информацион- ный вход 22 МПД - код с выхода БР Выход МПАР подключен к информационному входу 23 блока задержки Управляющий вход БЗ соединен с входом 24 управления записью ОЗУ и выходом 25

ния, элементы И 72 и 73

Устройство для контроля оперативной конвейерной памяти работает следующим образом

Работа осуществляется в двух режимах, режиме настройки и режиме тестирования В режиме настройки синхроимпульсы на буферный регистр и счетчик адреса не поступают Из внешнего управляющего уст правления записью БУ Информационный - ройства (управляющей вычислительной ма- вход 2Ь УИ подключен к выходу РД,шины) производится загрузка регистров устройства В РД12 загружается слово данных, например, код «Все 1 или «Все О В РНА 3 помещают начальный, а в РКА 8 - конечный адрес тестируемой области памяуправляющий вход 27 - к выходу БЗ, а вход 28 блокировкиУ выходу 29

управления блокировкой БУ крвыи вход 30 БСД соединен с информационным выходом

ОЗУ, а второй вход 31 - с выходом УИ40 ти В РРА 4 загружают код, задающий

Первый выход БСД подключен к входу 32пропускание с информационного входа 18

сигнала ошибки, а второй выход - к входуМПАР на выход МПАР сигнал заданного

БР Информационные входы 33 РД, 34 РНА,разряда СА Последним производится запись

35 РРА, 36 РКА, 37 РК объединены пов РК 10 Сигнал записи в РК перевосоответствующим разрядам и являются вхо-дит устройство в режиме тестирования

дом ввода данных (ВВД) устройства Управляющие входы записи 39 и РД, 40 в РНА, 41 в РРА. 42 в РКА 43 в РК и управляющий вход 44 МПД подключены к шине 45 управления, которая является управляющим входом устройства Управляющий вход записи информации в СА подключен к выходу 46 задания режима БУ Синхро- входы буферного регистра 47 и счетчика 48 адреса подключены к первому 49 и второму 50 синхровыходам БУ соответственно Выход

В режиме тестирования происходит последовательное формирование адресов ячеек памяти ОЗУ 17 в СА 1 и запись или считывание данных по этим адресам в соответствии с кодом, записанным в РК Дан- 50 ные на вход ОЗУ 17 поступают с выхода УИ 13, в котором происходит модуляция кода, записанного в РД 12 Если на управляющем входе 27 управляемого инвертора код «1 с выхода БЗ, то данные на информационном входе 26 проходят на выход УЧ

51требования обслуживания ТО) подклю-55 в прямом коде, а если «О, то - инверс- чен к блоку 6 управления Выход регистраном Код слова данных, записанный в РД 12 10 команд подключен к командному входутакже может быть прямым или инверс52БУ Вход 53 запуска БУ соединен сным

управляющим входом 43 записи в РК. Выход блока 9 сравнения конечного адреса соединен с входом 54 сигнала конечного адреса блока 9 управления Выход тактового генератора 7 соединен с входом 55 синхронизации блока 6 управления

Формат командного слова, загружаемого в РК, показан на фиг 2 Регистр команд содержит пять разрядов, каждый из которых определяет выполняемую операцию или условия ее выполнения Опера- ция осуществляется над всеми ячейками ОЗУ

реса из РНАЗ («1) 59, 4 - блокировка УИ 13 («О) 60

ние остановки по сигналу конечного адреса («1) с выхода 58 БСКА, 3 - разрешение установки СА 1 кода начального адБлок управления (фиг 3) содержит следующие основные блоки триггеры 61 и 62, элемент И 63, триггер 64, элементы И 65- 67, элемент И - НЕ 68, элемент И 69, сдвиговый регистр 70, выход 71 блока управления, элементы И 72 и 73

Устройство для контроля оперативной конвейерной памяти работает следующим образом

дит устройство в режиме тестирования

В режиме тестирования происходит последовательное формирование адресов ячеек памяти ОЗУ 17 в СА 1 и запись или считывание данных по этим адресам в соответствии с кодом, записанным в РК Дан- ные на вход ОЗУ 17 поступают с выхода УИ 13, в котором происходит модуляция кода, записанного в РД 12 Если на управляющем входе 27 управляемого инвертора код «1 с выхода БЗ, то данные на информационном входе 26 проходят на выход УЧ

Операции записи и чтения осуществляются следующим образом

При выполнении операции записи в РК загружается код команды с «1 в разряде 0. Сигнал записи 43 в РК поступает на вход 53 блока 6 управления (фиг 3) и устанавливает триггер 61 в «1, подготавливая пуск тестирования Приходящий на вход 55 БУ тактовый импульс (ТИ) из ГТИ 7 заносит «1 в триггер 62 При этом триггер 61 сбрасывается в «О. Если установка начального адреса разрешена («1 в 3 разряде РК), то на выходе элемента И 63 появляется сигнал записи в СА и происходит перезапись кода из РНА в СА, Следующий тактовый импульс установит триггер 62 в «О, а триггер 64 в «1 Сигнал «О с инверсного выхода триггера 64 запретит проход следующего ТИ через элемент И 65 Одновременно сигнал с прямого выхода триггера 64 разрешает проход ТИ через элемент И 66 на синхровход 48 счетчика адре- са 1 СА подсчитывает эти ТИ, формируя последовательность адресов Код адреса с выхода СА поступает на адресный вход 16 проверяемой памяти 17 Контрольные данные формируются на выходе УИ 13 и посту- пают на информационный вход ОЗУ Очередное слово данных формируется следующим образом. Код адреса с выхода СА 1 поступает на информационный вход 18 МПАР Управляющий вход МПАР подключен к выходу РРА. Код в РРА задает разряд адре- са СА, который проходит с входа 18 на выход МПАР. Выходной сигнал МПАР поступает на информационный вход 23 блока 11 задержки

На выходе 25 БУ установлено значение «1 при записи и «О при чтении При записи БЗ пропускает сигнал на своем входе 23 без задержки Выходной сигнал БЗ поступает на управляющий вход 27 УИ и модулирует в нем уровень выходного кода слова данных, записанного в РД 12

При достижении СА значения конечного адреса на выходе БСКА 9 появляется сигнал конечного адреса, который поступает на вход 54 БУ и, если в РК. в разряде 2 была «1, через элемент И 67 и ИЛИ 68 сбрасывает триггер 64 в «О, прекращая за- пись в ОЗУ и останавливая СА, т е происходит переход в режим настройки

При выполнении операции чтения в РК загружается код-команды с «О в разряде О По сигналу записи 43 в РК, как и при за- писи тестовых данных, устанавливается в «1 триггер 61, а затем 62 После загруз- ки из РНА в СА кода начального адреса триггер 64 устанавливается в «1 и на выходе 50 появляются импульсы продвижения СА Сигнал «1 с выхода 25 БУ устанав- ливает блок задержки в режим задержки Кроме того, сигнал «1 с выхода триггера 64 поступает на сдвиговый регистр 70

Регистр 70 и БЗ создают задержку распространения их входного информационного сигнзла, равную числу п ступеней (периодов задержки) конвейера проверяемой оперативной памяти 17 При возникновении сигнала конечного адреса на входе 54 БУ триггер 64 сбрасывается в «О, останавливая СА, но сигнал «1 с выхода регистра 70 сдвига будет еще п периодов ТИ, обеспечивая прием по синхросигналам а выходе 49 БУ в буферный регистр 14 слов данных, находившихся в процессе обработки в момент появления сигнала конечного адреса. Аналогично происходит остановка тестирования при появлении сигнала ошибки на входе 32 БУ первого выхода БСД Этот сигнал формируется при ошибке в любом разряде считанного слова данных, в то время как в БР записываются «О (нет ошибки) или «1 (есть ошибка) для каждого разряда отдельно Следовательно, после остановки по обнаруженной ошибке в БР находятся п слов, содержащих поразрядную информацию о несовпадающих с эталоном данных, а в СА находится адрес, где А0 - адрес ячейки памяти, в которой обнаружена ошибка Разумеется, остальные п - 1 слова также могут содержать обнаруженные ошибки Эти слова из БР, а также адрес и СА могут быть считаны через МПД на выход выво да данных (ВЫВД) устройства и приняты в ЭВМ Продолжить тестирование дальше следует командой, в которой в 3 разряде РК содержится «О Сигна i разрешения работы оперативной памяти (ВУ - выбор устройства) подается на ОЗУ с выхода 71 триггера 64 блока управления По этому сигналу ОЗУ принимает обращение в память на обслуживание Синхроимпульсы для работы конвейера ОЗУ поступают в него с выхода 55 ГТИ

Если установить в «О 4 разряд РК, то операции записи и чтения производятся через заблокированный УИ, т е код РД проходит на информационный вход ОЗУ без изменения. Это позволяет выполнить проверку памяти 17 тестом «Запись-чтение I и 0 и обнаружить все разрядные ошибки без влияния адресных, что упрощает диагностику неисправностей Остановки по ошибке и конечному адресу могут быть запре щены, установкой в «О соответствующих разрядов, что позволяет вести аппаратурную настройку и визуальный контроль сигналов в памяти с помощью осциллографа

Формула изобретения

Устройство для контроля оперативной конвейерной памяти, содержащее счетчик адреса, выходы которого являются адресными выходами устройства, мультиплексор адресных разрядов, информационные входы которого соединены с выходами счетчика адреса, регистр начального адреса, выходы которого соединены с информационными входами счетчика адреса, регистр разряда адреса, выходы которого соединены с управляющими входами мультиплексора адресных разрядов, блока сравнения данных, входы первой группы которого являются информационными входами устройства, блок управуправления, выходы управляемого инвертора соединены с входами второй группы блока сравнения данных и являются информационными выходами устройства, буферный регистр, информационный вход которого соединен с вторым выходом блока сравнения данных, мультиплексор данных, информационные входы первой группы которого соединены с выходами буферного регистра, информационные входы второй группы мульных являются выходами вывода данных устройства, соответствующие информационные ьходы регистра данных, регистра на- входом синх-чального адреса, регистра разряда адреса,

,,,„„,.„регистра конечного адреса и регистра команд объединены и являются входами ввода данных устройства, входы синхронизации регистра данных, регистра начального адреса, регистра разряда адреса, реления, вход признака ошибки которого сое- 10 типлексора данных соединены с выходами динен с первым выходом блока сравнения счетчика адреса, выходы мультиплексора дан- данных, выход управления записью блока управления является управляющим выходом устройства, генератор тактовых импульсов, выход которого соединен с ронизации блока управления, отличающееся тем, что, с целью упрощения устройства и повышения достоверности контроля, оно содержит регистр конечного адреса, блок сравнения конечного адреса, входы первой группы которого соединены с выходами счет- 20 гистра конечного адреса, регистра команд яв- чика адреса, входы второй группы блокаляются соответствующими входами синхросравнения конечного адреса соединены с вы-низации устройства, управляющий вход мульходами регистра конечного адреса, выход бло- типлексора данных является входом за- ка сравнения конечного адреса соединен сдания режима устройства, вход задания

входом признака конечного адреса блока 2с Режима счетчика адреса соединен с выходом управления, регистр команд, выходы кото-задания режима блока управления, входы

рого соединены с входами задания команд синхронизации буферного регистра и счетчи- блока правления, блок задержки, информа-ка адреса соединены соответственно с перционный вход которого соединен с выходомвым и вторым выходами синхронизации бломультиплексора адресных разрядов, управ-ка управления, выход требования обслужиляющий вход блока задержки соединен с вы- зо вания блока управления является соответст- ходом правления записью блока управле-вующим выходом устройства, вход синхроуправления, выходы управляемого инвертора соединены с входами второй группы блока сравнения данных и являются информационными выходами устройства, буферный регистр, информационный вход которого соединен с вторым выходом блока сравнения данных, мультиплексор данных, информационные входы первой группы которого соединены с выходами буферного регистра, информационные входы второй группы мультиплексора данных соединены с выходами счетчика адреса, выходы мультиплексора дан- гистра конечного адреса, регистра команд яв- ляются соответствующими входами синхро

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство тестового контроля логических узлов | 1990 |

|

SU1837295A1 |

| Устройство для контроля цифровых узлов | 1986 |

|

SU1357959A1 |

| Устройство управления процессора | 1988 |

|

SU1670686A1 |

| Микропрограммное устройство для управления и обмена данными | 1983 |

|

SU1129601A1 |

| Устройство синтаксически управляемого перевода | 1989 |

|

SU1651298A1 |

| Многоразрядный генератор испытательных последовательностей | 1983 |

|

SU1133589A1 |

| Мультимикропрограммная управляющая система | 1983 |

|

SU1133594A1 |

| Устройство для обмена информацией | 1982 |

|

SU1118992A1 |

| Процессор быстрых дискретных преобразований | 1989 |

|

SU1725227A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

Изобретение относится к вычислительной технике и может быть использовано для контроля и диагностики неисправностей оперативной памяти конвейерного типа для высокопроизводительных вычислительных машин. Цель изобретения - упрощение устройства и повышение достоверности контроля. Устройство содержит счетчик I адреса, мультиплексор 2 адресных разрядов, регистр 3 начального адреса, регистр 4 разряда адреса, блок 5 сравнения данных, блок 6 управления,генератор 7 тактовых импульсов, регистр 8 конечного адреса, блок 9 сравнения конечного адреса, регистр 10 команд, блок 11 задержки, регистр 12 данных, управляемый инвертор 13, буферный регистр 14, мультиплексор 15 данных, адресные входы 16 контролируемой оперативной буферной памяти 17. Устройство имеет малые ап- па-ратные затраты, повышает достоверность контроля благодаря программной настройке на различные тесты, области адресов и условия работы и позволяет работать с конвейерной памятью. 3 ил. 1C (Л

ния, регистр данных, управляемый инвертор, информационные входы которого соединены с выходами регистра данных, управляющий вход управляемого инвертора соединизации регистра команд соединен с входом запуска блока управления, выход разрешения работы памяти блока управления является выходом обращения устройства,

пен с выходом блока задержки, вход бло- 35 вычод генератора тактовых импульсов явля- кировки управляемого инвертора соединен сется выходом синхронизации оперативной

выходом управления блокировкой блокапамяти.

Разряд:

низации регистра команд соединен с входом запуска блока управления, выход разрешения работы памяти блока управления является выходом обращения устройства,

Фиг. 2

| Устройство для контроля адресных цепей блоков памяти | 1984 |

|

SU1200347A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля оперативной памяти | 1984 |

|

SU1226535A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1991-03-07—Публикация

1989-03-27—Подача