1

Изобретение относится к автоматике и вычислительной технике и может быть использовано в вычислительных устройствах и устройствах дискретной автоматики для вычисления экспоненциальной функции у е

Известно устройство для вычисления экспоненциальной функции,содержащее накопительные регистры, выходы которых соединены со своими входами через соответствующие однородные суг4маторы-вычитатели,блок управления, блок памяти, блок определения знака псевдочастотного,блок повторения итераций, блок, сброса, блок анализа сходимости и вентили.

Недостатком такого устройства для вычисления экспоненциальной функции является сложность его реализации.

Наиболее близким к предлагаемому является устройство для вычисления экспоненциальной функций, содержащее два регистра сдвига, сумматор,первый выход которого соединен через первый регистр сдвига с его первым входом, первый триггер, вход установки и прямой выход которого соединены соответственно со :входной шиной устройства и с первым входом первого элемента И, выход которого соединен

со вторым входом сумматора, второй выход которого соединен с первым входом второго элемента И, второй вход которого соединен со входом сброса первого триггера и с шиной сброса устройства L21Недостаток известного устройства заключается в сложности его реализации.

10

Цель изобретения - упрощение устройства для вычисления экспоненциальной зависимости.

Поставленная цель достигается тем, что в устройство, содержащее два

15 регистра сдвига, сумматор, первый триггер и два элемента И, причем первый выход сумматора через первый регистр сдвига подключен к первому входу сумматора, второй вход которого

20 соединен с в лходом первого элемента И, первый вход которого соединен с прямым выходом первого триггера, вход сброса которого является входом сброса устройства и первым входом

25 второго элемента И, второй вход которого соединен со вторым выходом сумматора, установленный вход первого триггера соединен с информационным входом устройства, введены 30 второй триггер, третий элемент И,

элемент ИЛИ и элемент задержки,причем второй вход первого элемента И соединен с выходом элемента ИЛИ и через второй регистр сдвига с первым входом третьего элемента И и входом сброса второго триггера,инверсный выход которого соединен череэ элемент задержки со вторым входом третьего элемента И, входы элемента ИЛИ соединены с выходом третьiero элемента И и прямым выходом второго триггера, установочный вход которого соединен с выходом второго элемента И.

Такое техническое решение устройства для вычисления экспоненциальной функции позволяет по сравнению с известным исключить из состава устройства второй сумматор и счётчик.

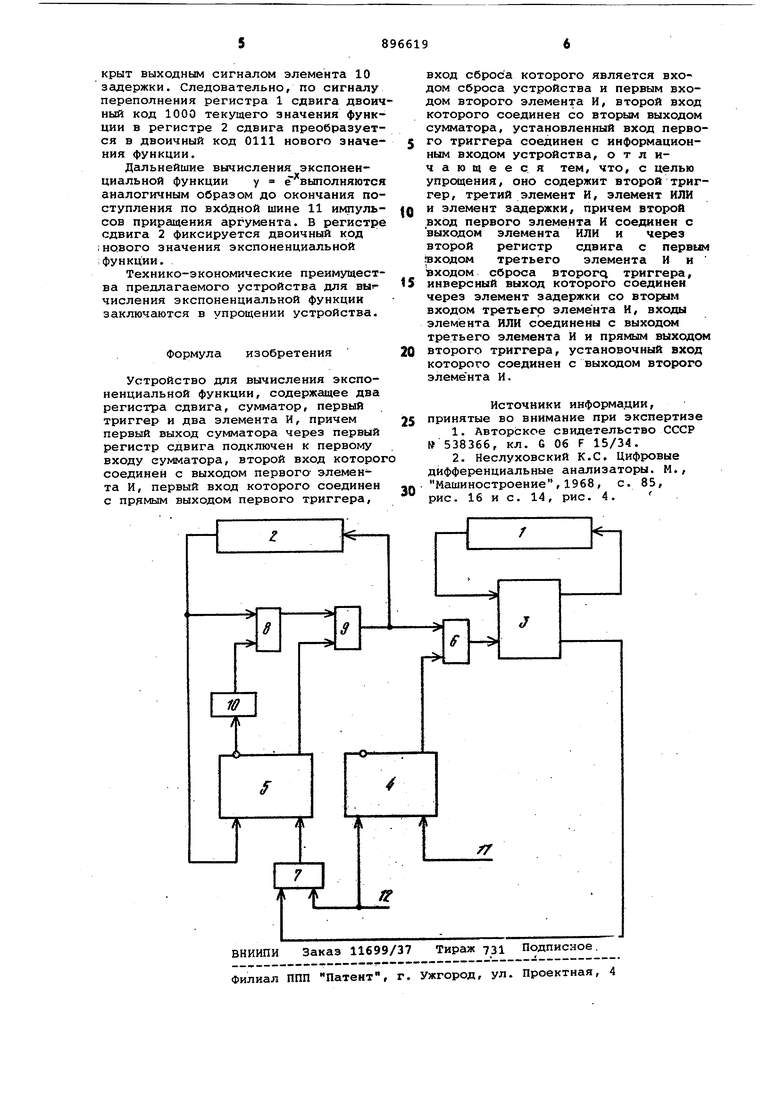

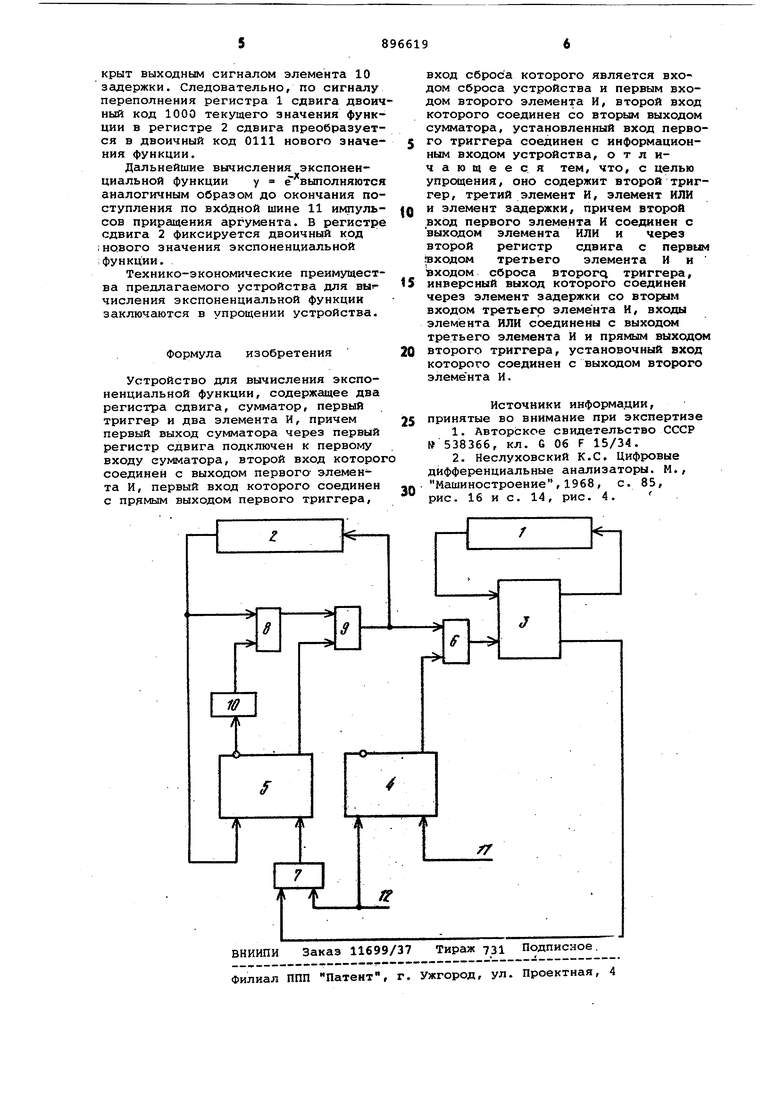

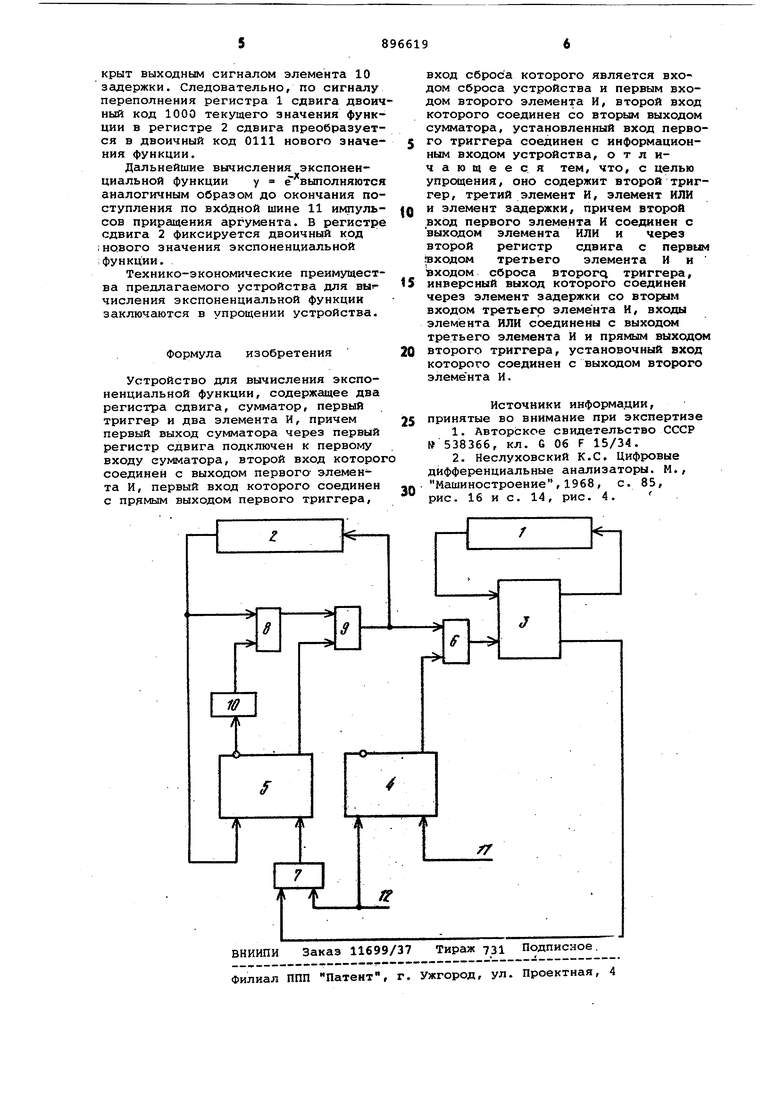

На чертеже изображена структурная схема устройства для вычисления экспоненциальной функции.

Устройство для вычисления экспоне1 1циальной функции содержит два регистра 1 и 2, сдвига, сумматор 3, два триггера 4 и 5, три элемента И 6, 7 и 8, элемент ИЛИ 9, элемент 10 задержки, вход 11 устройства и вход 12 сброса.

Устройство для вычисления экспоненциальной функции работает следующим образом.

В исходном состоянии регистр 1 сдвига очищен, триггеры 4 и 5 находятся- в нулевом состоянии. На вход 12 сброса поступает последовательность импульсов частоты f/n, где f частота тактовых импульсов; п - количество разрядов регистров 1 и 2 сдвига.

В регистр 2 сдвига записывается двоичный код начального значения функции у . На вход 11 устройства подается последовательность импульсов , представляющая собой поток прирсцдений аргумента.

Первый входной импульс, поступающий по входу 11, устанавливает триггер 4 в единичное состояние, в котором сигнап его прямого выхода открывает элемент И 6, подключая второй вход сумматора 3 к выходу элемента ИЛИ 9. Двоичный код начального значения функции сдвигается с выхода регистра 2 через элемент И 8, открытый сигналом инверсного выхода триггера 5, элемент ИЛИ 9 и элемент И 6 на второй вход сумматора 3, на первом выходе которого формируется последовательный двоичный код суммы, сдвигаемый в регистр 1, начиная с 4пaдшиx разрядов.

Двоичный код начального значения функции сдвигается с выхода регистра 2 на его вход без изменения через элементы И 8, ИЛИ 9 при нулевом сос-т тоянйи триггера 5.

Спустя п тактов триггер 4 сбрасывается в нулевое состояние, в котором сигнал прямого выхода триггера 4 закрывает элемент И 6.

Второй входной импульс, посту- пающий ко входу 11, вновь устанавливает триггер 4 в единичное состояние, в котором сигнал его прямого выхода открывает элемент И 6,

В этом случае на первый вход сумматора 3 с выхода регистра 1 рдвинутый, начиная с младших разрядов,двоичный код суммы предыдущего шага вычислений, а на второй вход сумматора 3 с выхода элемента ИЛИ 9 через элемент И 6 поступает двоичный код текущего значения функции.

В результате суммирования, выполняемого сумматором 3, может произойти переполнение регистра 1 сдвига,в который записывается только п разрядов суммы, а сигнал переполнения в виде переноса из п-го разряда поступает со второго выхода сумматора 3 через элемент И 7 на вход триггера 5, устанавливая его в единичное состояние.

В единичном состоянии триггер 5 находится до появления с выхода регистра 2 первой, начиная с глладшего разряда, единицы двоичного кода текущего значения функции. Если с выхода регистра 2 сдвига в младших разрядах появляются нулевые сигналы, то на вход регистра 2 сдвига и второй вход элемента И 6 поступают через элемент ИЛИ- 7 единичные сигналы прямого выхода триггера 5. Сигнал первой единицы двоичного кода текущего значения функции, действующий на выходе регистра 2 сдвига, сбрасывает триггер 5 в нулевое состояние , в котором на его прямом выходе устанавливается нулевой .сигнал.

Элемент 10 задержки обеспечивает стирание первой единицы двоичного кода текущего значения функции,так как поддерживает нулевой сигнал предыдущего состояния триггера 5 на втором входе элемента И В, который остается в закрытом состоянии до окончания действия сигнала первой единища на выходе регистра 2 сдвига.

Таким образом, двоичный код текущего значения функции в регистре сдвига 2 уменьшается на единицу младшего разряда по сигналу переполнения регистра 1 сдвига. Например, если в регистре сдвига 2 был код 1000, то по сигналу переполнения регистра 1 сдвига, который устанавливает триггер 5 в единичное состояние, в трех младших разрядах регистра сдвига 2 записываются единичные сигналы прямого выхода триггера 5, действующие через элемент ИЛИ 9 на входе регистра сдвига 2, а единичный сигнал четвертого разряда стирается элементом и 8, который за

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления элементарных функций | 1984 |

|

SU1168930A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1270770A1 |

| Устройство для контроля экспоненциальных процессов | 1986 |

|

SU1310781A1 |

| Устройство для контроля экспоненциальных процессов | 1990 |

|

SU1732331A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1985 |

|

SU1335989A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Устройство для вычисления экспоненциальной функции | 1982 |

|

SU1057944A2 |

| Устройство для вычисления показателя экспоненциальной функции | 1986 |

|

SU1335990A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1982 |

|

SU1043677A1 |

| Устройство для вычисления показателя экспоненциальной функции | 1983 |

|

SU1129611A1 |

Авторы

Даты

1982-01-07—Публикация

1980-04-29—Подача