(54) МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Адаптивное устройство микропрограммного управления | 1984 |

|

SU1290317A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1115054A1 |

| Микропрограммное устройствоупРАВлЕНия | 1979 |

|

SU830386A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1091158A1 |

| Устройство микропрограммного управления | 1988 |

|

SU1667070A1 |

| Микропрограммное устройство управления модуля вычислительной системы | 1983 |

|

SU1108447A1 |

| Микропрограммный процессор с контролем | 1981 |

|

SU985791A1 |

| Микропрограммное устройство управления | 1981 |

|

SU962943A1 |

| Микропрограммное устройство управления | 1980 |

|

SU959080A1 |

| Устройство для микропрограммногоупРАВлЕНия C КОНТРОлЕМ | 1979 |

|

SU809183A1 |

. . i- -;

Изобретение относится, к вьгчиспитепь. ной технике и может быть использовано .при построении самоконтропируемых устройств управления микропрограммных; ЭВМ и других систем. ,

Известно устройство микропрограммного управления, содержащее два запоминак щих блока, регистры, логические элементы , элементы задержки, дешифра торы, счетчики адресов микрокоманд,ю

генератор тактовых импульсов Cll

Недостатком этого устройства является низкая достоверность функционирования, обусловленная Отсутствием контроля правильности его функционирования. .is

Известно также микропрограммное устройство управления, содержащее два запоминающих блока, регистры, логическ -. элементы И, ИЛИ. элементы задержки, дешифраторы, два счетчика микрокоманд 20 и счетчик адреса, генератор тактовых им11ульсов t2D.

Недостатком этого устройства является низкая оперативность контроля правильности его функционирования, обусловленная организацией контроля правильно ти выполнения микропрограммы на уровне линейных последовательностей.

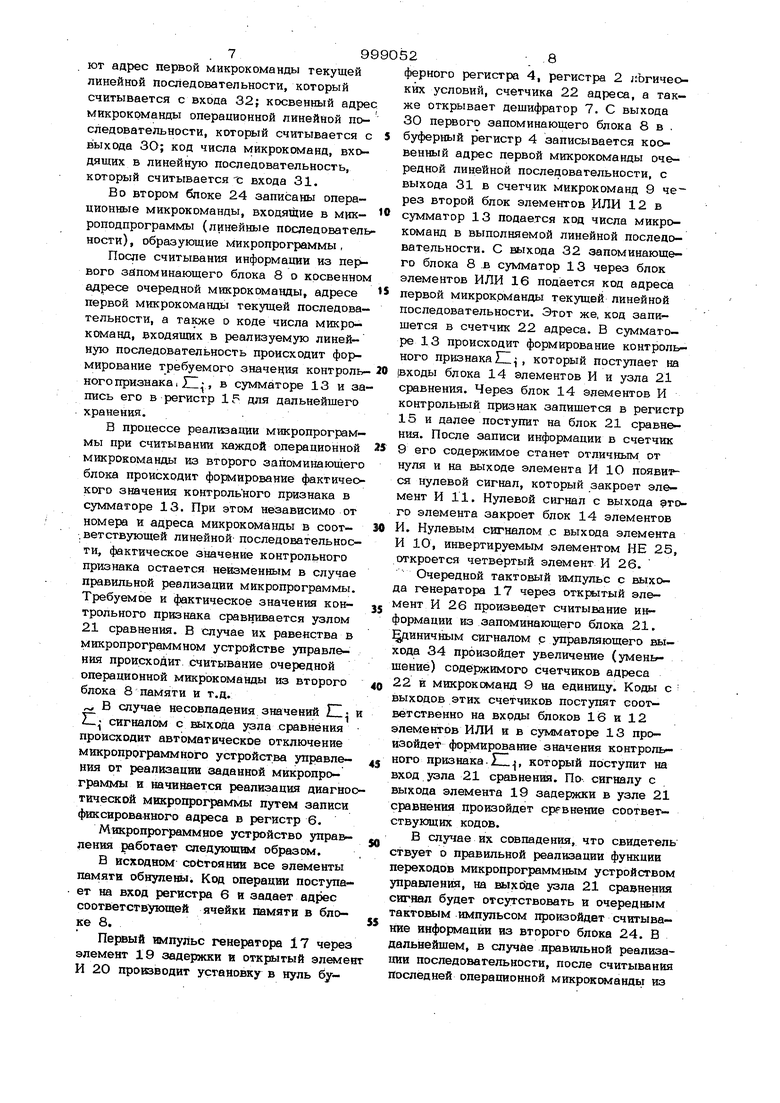

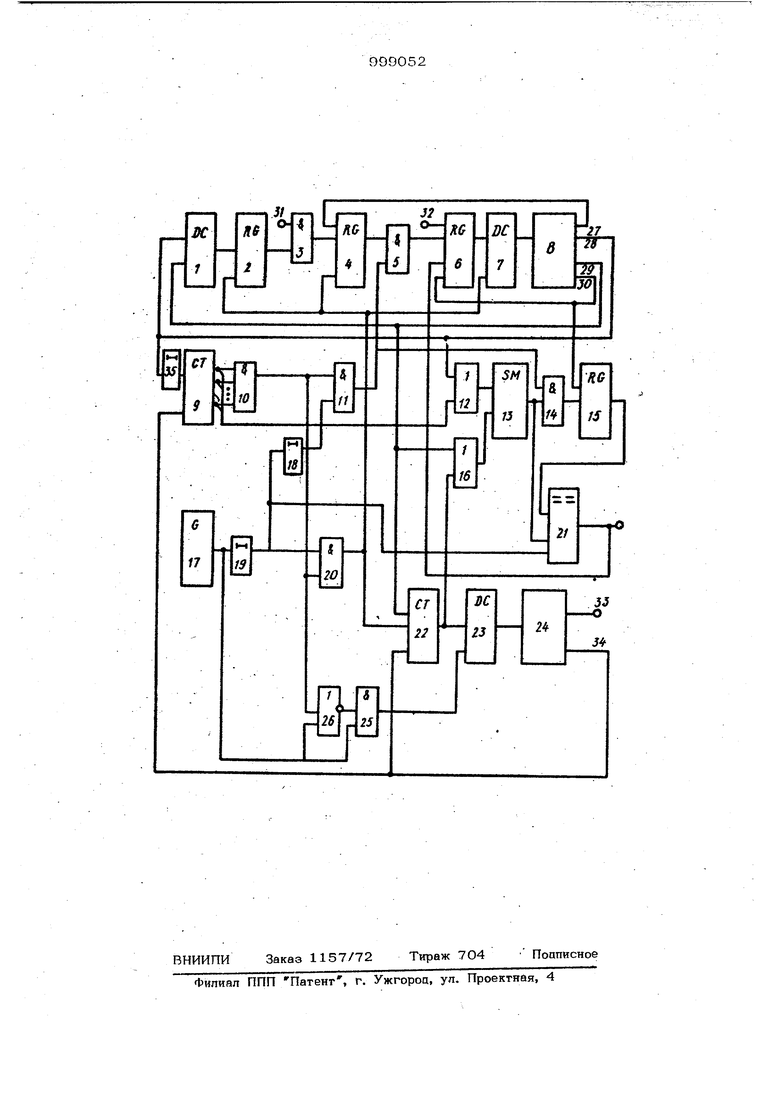

Наиболее близким по технической сущности и достигаемому положительному эффекту к предлагаемому изобретению является микропрограммное устройство управления, содержащее генератор импульсов, последовательно соединенные блок элементов И, регистр адреса, первый дешифратор и первый запоминающий блок, першлй выход которого соединен с первым входом буферного регистра, вто% рой выход - с первыми входамнС.счетчика микрокоманд и дешифратора логических условий, выход которого соединен с первым входом регистра логических условий, выход счетчика микрокоманд через последовательно соединенные первый и второй элементы И соединен с вторым второго блока элементов И, третий выход первого запоминающего блока соединен с вторым.вхЬдом дeшифpaтbila логических условий и первым входом счетчика адреса,выход которого соединен с первым входом второго дешифратора,а вход установки нуля соединен с вторыми входам первого дешифратора и регистра логичеоких условий, выход которого соединен с первым входом первого блока элементов И, а также с третьим входом буферного регистра и выходом третьего элемента И первый вход которого соединен с выходом первого элемента И, а через первый эле- .мент НЕ соединен с первым входом четве того элемента И, выход которого соедине с вторым вь ходом второго дешифратора.. выход которого соединен с входом второго запоминающего блока, первый выход которого соединен с выходом устройства, а второй выход - соединен с вторыми входами счетчиков мгссрокоманд и адреса, второй вход третьего элемента И через второй элемент задержки соединен с вторым входом четвертого элемента И и вь:ходом генератора импульсов, а через первый элемент задержки - с вторым входом второго элемента И, четвертый выход первого запоминающего блока соединен со входом Установки в нуль регистра адреса t 3 . Недостатком этого устройства явпяется низкая достоверность фyнкциoниpoвaния обусловленная отсутствием контроля правильности выполнения данной микрокоманды микропрограммы. В указанном устройст ве отказ в любом из ф икциональных блоков может привести к иская ению выполняемой микропрограммы. Целью изобретения является увеличение разрешающей способности контроля за счет фиксации ошибок в момент их возникновения. Поставленная.цель достигается тем, что в микропрограммное устройство управления, содержащее первый и второй блоки памяти, первый и второй дешифраторы адреса, дешифратор логических условий, счетчик адреса, счетчик микрокоманд, регистр логических условий, регистр адреса, буферный регистр, генератор импульсов, первый и второй элементы задержки, элемент НЕ, первый и второй блоки элементов И, первый, второй, третий и четвертый элементы,И, причем вход кода операции устройства соединен с первым информационным входом регистра адреса, выход которого соединен с информационным входом первого дешифратора адреса, выход первого дешифратора адреса соединен с входом первого блока памяти, адресный выход которого соединен с первым информационным входом буферного регис.тра, выход числа микрокоманд первого блока памяти соединен с первым информационным входом дешифратора логических условий, выход которого соединен с информационным входом регистра логических условий, выход начального адреса первого бпока памяти соединен с Ьторым информационным входом дешифратора логических услойий и информационным входом счетчика адреса, выход которого соединен с информационным входом второго дешифратора адреса, управляющий выход первого блока памяти соединен с установочньш входом регистра адреса, выход второго дешифратора адреса соединён с входом второго блока памяти, информационный выход которого является выходом микроопераций устройства,управляющий выход второго блока памяти соединен с счетными- входами счетчика адреса и счетчика микрокоманд, выходы которого соединены с входами первого элемента И, выход первого элемента И соединен с первым входом второго элемента И, первым входом третьего элемента И, и через элемент НЕ с первым входом четвертого элемента И, генератор импульсов соединен с вторым входом четвертого элемента И и через первый элемент задержки с входом второго элемента задержки и вторым входом третьего элемента И, выход которого соединен с управляющим входом первого дешифратора адреса и с установочными входами счетчика с адреq, буферного регистра и регистра логических условий, выход второго элемента задержки соединен с вторым входом второго элемента И,, выход которого соединен с первым входом первого блока элементов И, выход четвертого элемента --И соединен с управляющим входсад вто.рого дешифратора адреса, выход регистра логических условий соединен с первым входом второго блока элементов И, выход которого соединен с вторым информационным входом буферного регистра, выход буферного регистра соединен с вторым входом первого блока элементов И, выход которого соединен с вторым информационным входом регистра адреса, второй вход второго блока элементов И является входом логических условий устройства, дополнительно введены сумматор, регистр признака, блок сравнения, первый и второй блоки элементов ИЛИ,третий блок элементов И и третий элемент задержки, причем выход числа микрокоманд первого блока памяти соединен с первым входом первого блока элементов И и с входом треть его эпемента задержки, выход которого соединен с информационным входом счетчика микрокоманд, выходы счетчика микрокоманд соединены с втогыми входами первого блока элементов ИЛИ, выход которого соединен с первым входом сумматора, выход начального адреса первого блока памяти и выход счетчика адреса соединены соответственно с первым и вторым входами второго блока элементов ИЛИ, выход которого соединен с вторым входом сумматора, управляющий выход первого блока памяти соединен с установочнь(М входом регистра признака, выход которого соединен с первым информационным входом блока сравнения, выход второго элемента И соединен с первым входом третьего блока элементов И, выход, которого соединен с информационным входом регистра признака, выход сумматора соединен с вторым входом третьего блока элементов И и вторым информационным входом блока сравнения, выход которого является выходом сигнала ошибки устройства и соединен с установочным входом регистра адреса, выход первого элемента задержки соединен с управляющим входом блока сравнения. Сущность изобретения состоит в повышении достоверности функционирования микропрограммного устройства управления путем использования естественной информационной избыточности за счет организации контроля правильности реализации функций.переходов путем сравнения требуемого значения контрольного признака линейной последовательности микрокоманд с его фактическим значением в каждом такте считывания операционных микрокоманд, однозначно определяемом состоянием счетчиков адреса и микрокоманд. Формирование требуемого контрольного признака происходит путем суммирования кода числа N ( N- - количество микрокоманд в линейной последовательности Ц и кода числа А (А - адрес первой мик- линейной последоварокга анды в тельности). Таким образом, для микропрограммы, состоящей из i различных линейных последовательностей, формируется j различ ных контрольных признаков. Каждый контрольный признак П: позволяет индентифишгровать соответствующую линейную последовательность с точностью до значения суммы ее параметров. 99 2i Формирование фактического кoнtpoпьнo o признака в нродессесчитывания операционных микрокоманд из вто рого зчп,ом.инающего блока происходит путем суммирования содёржгалбго счетчиков адресов и микрокоманд При том независго-(о от адреса считываемой микрокоманды YjyeLj и количества уже реализованных микрокоманд в лкнейной последоватеяьвостй, знаяеййе обожав 5ь1ть величиной постоянной и npniipaBiiHiiHow функционировании микропр6грш«1много устройства упрайления шолжно выполняться условие Выполнение, этого условия свщетедьст вует о правильности реализайии в микро программном устройстве управле«Ця фущсций переходов. В противном случае условие (1) не выполняется. Следоаатепьно, предлагаемая процедура контроля основана на использовании для проверки функционирования естественной информационной избыточности, что позволяет ввойить в устройство минимальный объем средств проверки. На чертеже представлена функии&нап ная схема микропрограммного устройства управления. Устройство содержит дешифратор 1 логических условий, регистр 2 логических условий, второй блок 3 элементов И, .буферный регистр 4, первый блок 5 элементов И, адресный регистр 6, первый дешифратор 7 адреса, первый блок 8 памяти, счетчик 9 микрокоманд, первый элемент И 1О, второй элемент И 11, первый блок 12 элементов ИЛИ, сумматор 13, третий блок 14 элементов И, регистр 15 признака, второй блок 16 элементов ИЛИ, генератора 17 импулtrсов и второй элемент 18 задержки, Перувый элемент 19 задержки, третий эле- мент И 2О, блок 21 сравнения, счетчик 22 адреса, второй дешифратор 23 адрег са, второй блок 24 памяти, элемент НЕ 25 и четвертый элемент И 26, адресный выход 27, выход 28 числа микрокоманд, иыход 29 начального адреса и управляк щий выход 30 первого блока 8, вход 31 логических условий устройства, вход 32 кода операций устройства, информационный 33 и управляющий выходы 34 второго блока 24, соответственно, третий элемент 35 задержки. В первый блок 8 памяти записываются адресные микрокоманды, которые включа799ют адрес первой микрокоманды текущей линейной последовательности, который считывается с входа 32; косвенный адрес микрокоманды операционной линейной последовательности, который считывается с выхода ЗО; код числа к икрокоманд, входящих в линейную последовательность, который считываетсяс входа 31. Во втором блоке 24 записаны операционные микрокоманды, входящие в микроподпрограммы (линейные последователь ности), образующие микропрограммы, После считывания информации из первого запоминающего блока 8 о косвенном адресе очередной микрокоманды, адресе первой микрокоманды текущей последова- тельности, а также о коде числа микрокоманд, входящих в реализуемую линейную последовательность происходит формирование требуемого значения контрольного признака. rZ|, в сумматоре 13 и за пись его в регистр 15 для дальнейшего хранения. В процессе реализации микропрограм- мы при считывании каждой операционной микрокоманды из второго запоминающего блока происходит фор«1ирование фактического значения контрольного признака в сумматоре 13. При этом независимо от номера и адреса микрокоманды в соответствующей линейной последовательности, фактическое значение контрольного признака остается неизменным в случае правильной реализации микропрограммы. Требуемое и фактическое значения контрольного признака сравнивается узлом 21 сравнения. В случае их равенства в микропрограммном устройстве управления происходит, считывание очередной операционной микрокоманды из второго блока 8 памяти и т.д. В случае несовпадения значений EIj и сигналом с выхода узла сравнения происходит автоматическое отключение микропрограммного устройства управления от реализации заданной микропрограммы и начитается реализация диагнос тической микропрограммы путем записи фиксированного адреса в регистр 6. Микропрограммное устройство управления работает следующим образом. В исходном состоянии все элементы памяти обнулены. Код операции поступает на вход регистра 6 и задает адрес соответствующей ячейки памяти в блоке 8. Первый импульс генератора 17 через элемент 19 задержки и открытый элеме И 20 производит установку в нуль бу2.8 ферного регистра 4, регистра 2 :bгичeoкйх условий, счетчика 22 адреса, а также открывает дешифратор 7. С выхода 30 первого запоминающего блока 8 в . буферный регистр 4 записывается косвенный адрес первой микрокоманды очередной линейной последовательности, с выхода 31 в счетчик микрокоманд 9 через второй блок элементов ИЛИ 12 в сумматор 13 подается код числа микрокоманд в выполняемой линейной последовательности. С выхода 32 запоминающего блока 8 .в сумматор 13 через блок элементов ИЛИ 16 подается код адреса первой микрокоманды текущей линейной последовательности. Этот же, код запишется в счетчик 22 адреса. В сумматоре 13 происходит формирование контрольного признака Щ, который поступает на входы блока 14 элементов И и узла 21 сравнения. Через блок 14 элементов И контрольный признак запишется в регистр 15 и далее поступит на блок 21 сравнения. После записи информации в счетчик 9 его содержимое станет отличным от нуля и на выходе элемента И 10 появирся нулевой сигнал, который закроет элемент И 11. Нулевой сигнал с выхода этого элемента закроет блок 14 элементов И. Нулевым сигналом с выхода элемента И 1О, инвертируемым элементом НЕ 25, откроется четвертый элемент И 26. Очередной тактовый импульс с выхода генератора 17 через открытый эле 6 произведет считывание информации из запоминающего блока 21. Циничным сигналом с управляющего выхода 34 произойдет увеличение (уменьшение) содержимого счетчиков адреса 22 и микрокоманд 9 на единицу. Коды с выходов этих счетчиков поступят соответственно на входы блоков 16 и 12 элементов ИЛИ и в сумматоре 13 произойдет формирование значения контрольного признака-HI , который поступит на вход узла 21 сравнения. По сигналу с выхода элемента 19 задержки в узле 21 сравнения произойдет cpfвнение соответствующих кодов. В случае их совпадения, что свидетель ствует о правильной реализации функции переходов микропрограммным устройством управления, на узла 21 сравнения сигнал будет отсутствовать и очередным тактоШ)1М импульсом произойдет считывание информации из второго блока 24. В дальнейшем, в случае правильной реализации последовательности, после считывания последней операционной микрокс ланды из второго бпока 24 произойдет обнуление счетчика 9 микрокоманд и на выходе элемента И 10 появится единичный сигнал, который откроет элемент И 11. Тактовым импульсом с выхода ге,нэратора 17, npt ходящим через элементы 19 и 18 задержки и элемент И 11, произойдёт запись адреса следующей адресной микрокоманды линейной последовательности через открытый блок 5 элементов И в адресный регистр 6. Тактовым импульсом свыхода генератора 17 через элемент 19 вадержки и элемент И 2О произойдет обнуление счетчика 22 аареса, регистров 2 и 4 а такж запуск дешифратора 7. При-.етитьшайии информации из блока 8 сигналом с выхода 30 произойдет обнуление региотра 15 и подготовка его для записи очередного значения контрольного признака Пд. В дальнейшем работа устройства будет протекать аналогично описанной выше... Рассмотрим работу микропрограммного устройства управления при возникновении отказов во время считывания микрокоманд

Отказы такого рода могут возникнуть либо в счетчике 9, либо в счетчике 22, непосредственно участвующих в реЬлиза- ции функций переходов. При возникновении. отказов в указанных фиксирует вы&1оках блок 21 сравнен полнение условия Ц. Г . и на его вы ходе появляется единичный сигнал, который поступает на вход адресного регистра 6, прекращая выполнение заданной микропрограммы и задавая фиксированный адрес первой микрокоманды диагностической Тйгикропрограммы. Кроме того, в микропрограммном устройстве управления организуется кон роль правильности функционирования таких узлов схемы контроля как сумматор 13, регистр 15, Отказ в любом из этих блоков приводит к выполнению условия и обуславливает возможность самоконтроля средств проверки микропрограммного устройства управления. Таким образом, в предлагаемом микро программном устройстве управления осуществляется контроль правильности peaлизаини функции переходов, что позволяет повысить достоверность функционирсьвания микропрограммного устройства управления. Кроме того, в предлагаемом устройстве средства контроля обладают некоторыми возможностями для самопроверки. Использование предлагаемого изобр тения позволяет строить самоконтролиру-

ра, выкоа числа микрокоманд первого блока памяти соединен с первым информационным входом дешифратора логических условий, выход которого соединен с юшие микропрограммные устройства с высокой достоверностью функционирова1яия. Формула изобретения Микропрограммное устройство управления, содержащее первый и второй блоки памяти, первый и второй дешифраторы адреса, дешифратор логических условий, счетчик адреса, счетчик микрокоманд, регистр логических условий, регистр адреса, буферный регистр, генератор импульсов, первый и второй элементы задер жки, элемент НЕ, первый и второй блоки элементов И, первый и второй, третий н четвертый элементы И, причем вход кода операции устройства соединен с первым информационным входом регистра адреса вь1ход которого соединен с информацио ным входом первого деши(|фатор& адреса, выход первого дешифратора адреса соединен с в ходом первого блока памяти, адресный выход которого соединен с первым информационным входом буферного регистинформационным входом регистра логичеоких условий, начального адреса первого блока памяти соединен с вторым информационным входом дешифратора логических условий и информационным входом счетчика адреса, выход которого соединен с информационным входом второго дешифратора адреса, управляющий выход первого блока памяти соединен с установочным входом регистра адреса, выход второго дешифратора адреса соединен с входом второго блока памяти, информа ЦИОННЫЙ выход которого является .микроопераций устройства, управл а ющий выход второго блока памяти сое{динен с счетными входами счетчика адре са и счетчика микрокоманд, выходы которого соединены с входами первого элемента И, выход первого элемента И сое--: двнен с перимми входами второго, треть-i его и четвертого элементов И, выход |1 нератора импульсов - с вторым входа четвертого алаи(ента И и через первый элемент задержки - с входом второго элемента задержки и вторым входом третьего элемента И, выход которого со&- динен с управляющим входом первого дешифратора адреса и с установочными входами счетчика адреса, буферного регистра и регистра логических условий. выход второго элемента задержки соединен с вторым входом второго элемента И, выход которого соединен с первым входом первого блока элементов И, выхо четвертого элемента И соединен через элемент НЕ с управляющим входом второго дешифратора адреса, выход регистра логических условий соединен с первым входом второго блока элементов И, вы-ход которого соединен с вторым инфоркмадионным входом буферного регистра, второй вход второго блока элементов И является входом логических условий устройства, отличающееся тем, что, с целью увеличения разрешающей способности контроля за счет фиксации ошибок в момент их возтпсновеиия, в него введены сумматор, регистр признака блок сраваения, первый и второй блоки элементов ИЛИ, третий блок элементов И, третий элемент задержки, причем выход числа микрокоманд первого блока памяти соединен с первым входом первого блока элементов И и с входом третьего элемента задержки, выход которого соединен с информационным входом счетчик микроК1 1анд, выходы счетчика микрокоманд соединены с вторыми входами первого блока элементов ИЛИ, выход которо го соединен с первым входом сумматора выход начального адреса первого блока 9 212 памяти и выход счетчика адреса соединены соответственно с первым и вторым входами второго блока элементов ИЛИ, выход которого соединен с вторым входом сумматора, управляющий выход первого блока памяти соединен с установочным входом регистра признака, выход которого соединен с первым информационным входом блока сравнения, выход второго элемента И соединен с первым входом третьего блока элементов И, выход которого соединен с информационным входом регистра признака, выход сумматора соединен с вторым входом третьего блока элементов И и вторым информационным входом блока сравнения, выход которого является выходом сигнала ошибки устройства и соединен с установочньш входом регистра адреса, выход первого элемента задержки соединен с управляющим входом блока сравнения. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 482744, кл. Q 06 F 9/16, 1974. 2.Авторское свидетельство СССР № 849891, кл. G, Об F 9/16, 1981. 3.Авторское свидетельство СССР № 703811, кл, Q Об F 9/16, 1981 (прототип).

Авторы

Даты

1983-02-23—Публикация

1981-07-02—Подача