I

Изобретение относится к автоматике и вычислительной технике, в частности к техническим срецствам обучения, и может быть использовано для программированного контроля знаний учащихся.

Известно устройство, содержащее элементы памяти и ответов учащихся, эталонных ответов, пульты учащихся, блок преподавателя Cl .

Данное устройство имеет ограничён.ные дидактические характеристики и низкую точность контроля знаний.

Известно также устройство, содерзкашее бпок ввода ответов, соединенный с узлом сравнения, блок памяти, генератор, распределитель, коммутатор, табло предъявлений и табло оценок l2l .

Указанное устройство имеет низкую точность контроля знаний, ограниченные дидактические характеристики.

Наиболее близким к предлагаемому является устройство, содержащее элементы памяти ответов учащихся и эталонных ответов, схемы сравнения, счетчики

количества вводов ответов и вводов эталона, триггер опроса Гз .

Устройство позволяет повысить точность контроля знаний, однако обладает ограниченными дидактическими возможностями.11ель изобретения - расширение дидактических возможностей устройства за счет распознавания устройством содержательного ответа, независимо от

10 формы его представления.

Поставленная цель достигается тем, что в устройство, содержащее последовательно включенные блок ввода ответов, первый элемент ИЛИ, первый счетчик,

15 первый коммутатор, блок памяти, вход которого соединен со вторым выходом блока ввода ответов, а выход - со вторым входом первого коммутатора, триггер и блок сравнения, введены, в торой,

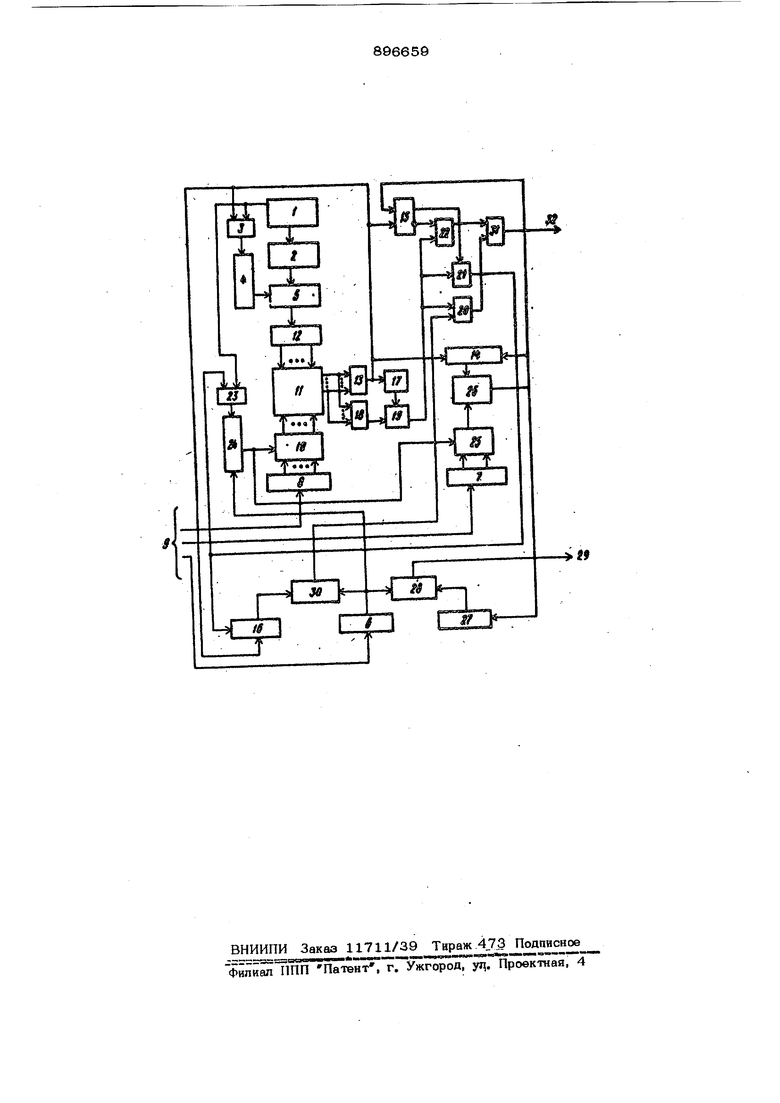

М третий, четвертый и пятый счетчики, второй, .третий и четвертый элементы ИЛИ, три регистра, дешифратор, четыре блока элементов И, второй коммутатор. 3 четыре элемента И, инвертор и элемент . задержки, выход которого через первый элемент И соединен с первыми входами второго, третьего и четвертого элементов И, вход - непосредственно с выходо блока сравнения, подключенным через второй элемент ИЛИ к первому входу второго счетчика, второму входу первого элемента ИЛИ, первому входу тригге ра, первому входу третьего счетчика и входу инвертора, выход которого соединен со вторым входом первого элеме та И, входы регистров являются входами устройства, выход первого регистра соединен с первыми входами первого и вто рого блоков элементов И и четвертого счетчика, второй вход которого подключен к выходу третьего элемента ИЛИ, а выход - к первым входам второго коммутатора и третьего блока элементов И, второй вход которого соединен с выходом второго регистра, а выход - с первым входом блока сравнения, второй вход которого через дешифратор подключен к выходу первого коммутатора, первый вход третьего элемента ИЛИ соединен с первым выходом блока ввода ответов, а второй вход - с выходом второг элемента И, подключенным ко второму входу второго счетчика, выход которого соединен со вторым входом второгс| блока элементов И, вБ1Ход которого подключен ко второму входу третьего элемента И, первый и второй выходы триггера соединены со вторыми входами второго и четвертого элементов И соответственн а второй вход - с выходом четвертого блока элементов И, подключенным ко входу пятого счетчика и второму входу третьего счетчика, выход которого соединен с первым входом четвертого блока злементов И, второй вход которого подключен к выходу второго ко.ммутатора, второй вход которого соединен с выходом третьего регистра, выход пятого счетчика подключен ко второму входу первого блока элементов И, выход которого является первым выходом устройст ва первый и второй входы четвертого элемента ИЛИ соединен с выходами трет его и четвертого элементов И соответственно, а выход - со вторым выходом устройства. На чертеже изображена схема устрой ства для контроля знаний обучаемых, Устройство содержит блок 1 ввода ояветов, связанный непосредственно с блоком 2 памяти ответов учащихся и через элемент ИЛИ 3 со счетчиком 4 9 количества элементов ответа, выходы которого и выходы блока 2 соединены с коммутатором 5, регистр 6 числа групп, регистр 7 числа элементов в группе, регистр 8 кода группы каждого элемента ответа, входы которых являются входами 9 устройства, причем входы регистра 8 через блок 10 элементов И подключены к блоку 11 сравнения, другие входы которых через дешифратор 12 связаны с коммутатором 5. Выходы блока 11 через элемент ИЛИ 13 связаны со счетчиком 14 совпавших элементов, нулевым входом триггера 15, элементом ИЛИ 3, счетчиком 16 несовпавших групп и инвертором 17. Выход инвертора 17 и выход элемента 18 задержки, связанного с выходами блока 11, подключены к элементу И 19, соединенному с первыми входами элементов И 20-22, Второй вход элемента И 22 связан с инверсным входом триггера 15, прямой вход которого соединен со вторым входом -элемента И 21, выходом св51занным со счетным входом счетчика 16 и входом элемента ИЛИ 23. Элемент ИЛИ 23 подключен вторым входом к блоку 1, а выходом - к счетчику 24 групп элементов, выходом соединенному с блоком 1О и коммутатором 25, другим входом связанным с регистром 7, а выходом - с блоком 26 элементов И, Блок 26 подключен к выходу счетчика 14, а выходом к единичному входу триггера 15, счетчику 14 и счетчику 27 совпавших групп. Выходы счетчика 27 и регистра 6 подключены через блок 28 элементов И к выходу 29 устройства, В1;||даюшему сигнал Правильный ответ. Кроме того, регистр 6 связан со счетчиком 24 и блоком 30 элементов И, с входом кото рого соединен счетчик 16, а выход подключен ко второму входу элемента И 20. Выходы элементов И 20 я 22 соединены с элементом ИЛИ 31, выход которого является выходом 32 устройства, выдающим сигнал Ошибка. Конструктируемый ответ на вопрос можно представить в виде: лw,...m2.)vCw...лmp)v...tmg4-l -.w) где т- (ie1i t) - элементы ответа (слова, знаки, буквы, цифры), . объединенные скобками в группы; операция Л -означает, что элементы могут занимать любое место в группе;

операция Y означает, что группа может занимать любое место в ответе.

Для анализа правильности ответа, который может быть представлен в виде (1), необходимо иметь информацию о пр инадлежности элемента к группе, о числе элементов в группе и числе групп, которая вводится из пульта преподавател (не показан) по соответствующим шинам 9 в регистры 8, 7 и 6. Причем, для каждого элемента используемого алфавита символов в регистре 8 отводится соответствующая ячейка, в которую заносится номер группы, которой принадлежит элемент в данный момент. В регистре 7 для каждой группы элементов отводится ячейка, в которой записьшается число элементов. Число, записанное, например, в первой ячейке должно совпадать с числом ячеек в регистре 8, в которых записана 1, т.е. номер условий 1-й группы.

Устройство работает следующим образом.

Из блока 1 учащийся вводит последовательно коды элементов ответа в элементы памяти блока 2, каждый элемент в очередную ячейку. После окончания ввода ответа из блока 1 поступает сигнал готовности (по которому начинается контроль правильности ответа) через элементы ИЛИ 3 и 23 на счетчики 4 и 24, По этому сигналу в счетчики 4 и 24 записывается 1, Через блок 10 на блоке 11 коммутируются направления тех элементов, у которых номер группы совпадает с записанным на счетчике 24. Опновременно, через коммутатор 5, управляемый счетчиком 4, на дешифратор 12 поступает код элемента, записанного в элементах памяти блока 2 первым. Этот код расшифровьюается дешифратором 12 и поступает на вторые входы блока 11. Если направление от дешифратора 12 совпадает хотя бы с одним из направлений от блока 10, то, следовательно, обнаружена группа, содержащая данный элемент. Сигнал совпадения с блока 11 через элемент ИЛИ 13 поступает на счетчик 14, взводит триггер 15, сбрасывает счетчик 16 и как счетный через элемент ИЛИ 3 поступает на счетчик 4 чем обеспечивается подключение к дешифратору 12 следующего элемента ответа. При этом, если содержимое счетчика 14 не равно числу в ячейке регистра 7 (анализ условия обеспечивают блок 26 и коммутатор 25), то операция повторяется. Если при этом обнаруживается несовпадение, то через открытый триггером 15 элемент И 22 на выход 32 (через элемент ИЛИ 31) поступает сигнал

Ошибка, означающий, что в данной Группе ответа содержание элементов отличается от эталона. Если же число совпавших элементов при очередном сигнале совпадення с блока 11 равно числу

элементов в данной группе, записанному в соответствующей $1чейке регистра 7 поступающему на вход блока 26 через коммутатор 25, то с выхода блока 26 снимают сигнал, перевод5Ш1ий триггер

15 в исходное состояние, сбрасьгаакяций счетчик 14 и поступающий на счетный вход счетчика 27. Если все элементы во всех группах совпадают, содержимое счетчика 27 равно содержимому регист

ра 6, что фиксируется Зевсом 28, с выхода которого на выход 29 устройства поступает сигнал Правильный ответ .

Если в момент анализа следующего элемента ответа с блока 11 снимается

сигиал несовпадения через элементы 17 и 18 при исходном состоянии триггера 15, то на вход счетчиков 24 и 16 поступает единичный сигнал. При этом элемент ответа анализируется на наличие в следующей группе до тех пор, пока не будет обнаружено совпадение либо на счетчике 16 накопится число, равное содержимому регистра 6, что фиксируется блоком ЗО и означает, что анализируемого элемента нет в составе эталона.

Сигнал об ошибке при очередном несовпадении через элементы И 20, ИЛИ 31 поступает на выход 32 устройства как сигнал Ошибка. .

Если же в процессе анализа зафиксировано совпадение элемента с эталонными элементами группы, то этот сигнал с блока 11 поступает на счетный вход счегцпса 4 и сбрасывает в исходное состояние 16. Устройство по-, втрряет описанные выше операции.

Устройс-гао позволяет анализировать также ответы типа

tfl Л ttl (Л... Л W

где каждый элемент m распознается как группа из одного элемента.

Если схемой анализируется выборочный ответ, т. е. один элемент т из ряда предложенных учащимся, то при этом эталонный код ( т) содержится в первой группе, в которой только один . элемент.

Устройство может контролировать и результативный ответ, который для по7вьппения надежности его контроля может быть представлен в виде (О;, V вп ) V v(a,,й)V...,), где а,, - цифры в ответе, a скобки означают объединение в произвольные группы цифр результативного ответа. Устройство позволяет контролировать ответ, представленный свободно конструируемой форме, что расширяет, дидак тические возможности устройства, а Имен но представляет обучаемому возможность формировать ответ по существу, не ограничивая его формой ответа. Устройство позволяет также повысить объективность и надежность контроля знаний за счет распознавания информации, представленной в форме, приближенной к естественной, что устраняет необходимость контро ля синтаксических ошибок, не имеющих отношения к содержанию ответа. Формула изобретения Устройство для контроля знаний обучаемого, содержащее последовательно включенные блок ввода ответов, первый элемент ИЛИ, первый счетчик и первый коммутатор, блок памяти, вход которого соединен со вторым выходом блока ввода ответов, а выход - со вторым йходом первого коммутатора, триггер и блок сравнения, отличающееся тем, что, с целью расширения дидактических возможностей устройства, оно содержит второй, третий, четвертый и пятый счетчики, второй, третий и четвертый элементы ИЛИ, три регистра, дешифратор, четыре блока элементов И, второй коммутатор, четыре элемента И, инвертор и элемент задержки, выход которого через первый элемент И соединен с первыми входами второго, третьего и четвертого элементов И, вход - непосред ственно с выходом блока сравнения, подключенным через второй элемент ИЛИ к первому входу второго счетчика, второму входу первого элемента ИЛИ, первому входу триггера, первому входу третьего счетчика и входу инвертора, выход которого соединен со вторым вхо9ДОМ первого элемента И, входы регистров являются входами устройства, выход первого регистра соединен с. первыми входами первого и второго блойов элементов И и четвертого счетчика, второй вход которого подключен к выходу третьего элемента ИЛИ, а выход - к первым входам второго коммутатора и третьего блока элементов И, второй вход которого соединен с выходом второго регистра, а выход - с первым входом блока сравнения, второй вход которого через дешифратор подключен к выходу первого коммутатора, первый вход третьего элемента ИЛИ соединен с первым выходом блока ввода ответов, а второй вход - с выходом второго элемента И, подключенным ко второму входу второго счетчика, вы-ход которого соединен со вторым входом второго блока элементов И, выход которого подключен ко второму входу третьего элемента И, первый и второй выходы триггера соединены со вторыми входами второго и четвертого элементов И соооветственно, а второй вход - с выходом четвертого блока элементов И, подключенным ко входу пятого счетчика и второму входу третьего счетчика, выход которого соединен с первым входом четвертого блока элементов И, второй вход которого подключен к выходу второго коммутатора, второй вход которого соединен с выходом третьего регистра, выход пятого счетчика подключен ко второму входу первого блока элементов И, выход которого является первым выходом устройства, первый и второй входы четвертого элемента ИЛИ соединены с выходами третьего и четвертого элементов И соответственно, а выход - со вторым выходом устройства. Источники информации, принятые во внимание при экспертизе 1,Авторское .свидетельство СССР N9 402902, кл. q 01 В 7/02, 1973. 2,Авторское свидетельство СССР № 456294, кл. Q 09 В 7/00, 1975. 3,Авторское свидетельство СССР № 613361, кл. G 09 В 7/02, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля знаний обучаемых | 1983 |

|

SU1116451A1 |

| Устройство для обучения | 1980 |

|

SU985814A1 |

| Автоматизированный класс для контроля знаний обучаемых | 1981 |

|

SU963065A1 |

| Автоматизированный класс для обучения и контроля знаний учащихся | 1982 |

|

SU1228137A1 |

| Автоматизированный класс для контроля знаний обучаемых | 1984 |

|

SU1196938A1 |

| Устройство для контроля знаний обучаемых | 1981 |

|

SU982063A1 |

| Устройство для контроля знаний обучаемых | 1986 |

|

SU1336082A1 |

| Устройство для контроля знаний обучаемых | 1980 |

|

SU896660A1 |

| Автоматизированный класс для контроля знаний | 1982 |

|

SU1035634A1 |

| Устройство для обучения и контроля знаний обучаемых | 1982 |

|

SU1065869A1 |

Авторы

Даты

1982-01-07—Публикация

1980-04-18—Подача