1

Изобретение относится к вычислительной технике и предназначено для использования в стендах проверки решающих блоков цифровых интегрирующих структур.

Известны распределители импульсов содержащие п-разрядный сдвигающий регистр, п двухвходовых элементов И и многовходовой элемент И. Распределители предназначены для использования в блоках управления цифровых интегрирующих структур и в стендах проверки решающих блоковэтих структур U1 и 12 .

Однако такие распределители импульсов не позволяют менять число выдаваемых распределенных временных импульсов.

Наиболее близким к предлагаемому техническим решением является распределитель импульсов, содержащий п-разрядный сдвигающий регистр, п двухвходовых элементов И и многовходовой элемент А, причем нулевые выходы четных разрядов п-разрядного сдвигающего регистра за исключением последнего разряда соединены со входами многовходового элемента И, выход которого соединен с информационйым входом п-разрядного сдвигающего

регистра, вход синхронизации которорого соединен с тактирующим входом распределителя импульсов,входы каждого из п-двухвходовых элементов И соединены с единичными выходами соседних разрядов п-разрядного сдвигающего регистра, включая и пару первого с последним разрядом, а выходы двухвходовых элементов И соединены с

10 группой выходов распределенных временных импульсов 3.

Недостатком .этого распределителя импульсов является то, что он не позволяет менять число вьщаваемых рас15пределительных временных импульсов. В то же время, в стендах проверки решающих блоков для проверки различных решающих блоков с различной длиной разряд ной сетки подинтегральной функции

требуются распределители импульсов, в которых число выдаваемых временных импульсов могло бы изменяться.

Цель изобретения - расширение функциональных возможностей распределителя имп-ульсов за счет обеспечения возможности изменения числа вьщаваемых временных импульсов.

Поставленная цель достигается тем, что в распределитель импульсов, содержащий п-разрядный сдвигающий реистр, группу из (п-1) двухвходовых лементов И и многовходовой элемент , причем нулевые выходы четных разядов п-разрядного сдвигающего реистра за исключением последнего разяда соединены со входами многовхоового элемента И, выход которого оединен с информационным входом пазрядного сдвигающего регистра,вход инхронизации которого соединен с тактирующим входом распределителя иглпульсов, входы каждого i-го двухвходового элемента И первой группы (i l,...,n-l) соединены с единичными выходами i-го и {1 + 1)-го- разрядов п-разрядного сдвигающего регистра, выход каждого двухвходового элемента И первой группы соединен с выходами распределителя импульсов, дополнительно введены К двухразрядных сдвигающих регистров, четыре группы элементов И, две группы элементов ИЛИ и две группы элементов НЕ, причем единичный выход последнего разряда п-разрядного сдвигающего регистра и единичный выход последнего разряда каждого двухразрядного сдвигаю- . щего регистра за исключением последнего двухразрядного сдвигающего регистра, подключены к первым входам соответствующих элементов И второй группы, выходы которых соединены с информационными входами соответствующих двухразрядных сдвигающих регистров, входе синхронизации каждого из которых соединен с тактирующим входом распределителя импульсов, выход ка}хдого элемента И второй группы соединен со входом соответствующего элемента НЕ первой группы и с первым входом соответствующего элемента и третьей группы, второй вход ка;хдого из которых соединен с единичным выходом первого разряда соответствующего двухразрядного сдвигающего регистра, единичные выходы первого и второго разрядов каждого двухрахрядного сдвигающего регистра соединены со входами соответствующих элементов И четвертой группы, единичный выход последнего разряда п-разрядного сдвигающего регистра и единичный пыход последнего разряда каждого двухразрядного сдвигающего регистра соединены с перВЕЛМи входами соответствующих элементов И пятой группы, второй вход каждого из которых соединен с единичным выходом первого разряда п-разрядного сдвигающего регистра, а третийвход каждого элемента И пятой группы за исключением последнего элемента И соединен с выходом соответствующего элемента НЕ второй группы, вход каждого из кЙторых за исключением последнего соединен с выходом соответствующего элемента ИЛИ первой группы, первый вход ка/кдого из которых соединен с соответствующим управляющим входом группы управляющих входов распределителя импульсов, выход каждого последующего элемента ИЛИ первой группы за исключением первого элемента ИЛИ этой 5 группы соединен со вторым входом предыдущего элемента ИЛИ первой группы, второй вход каждого .элемента и второй группы за исключением последнего элемента И этой группы соединен.

Q с выходом соответствующего элемента ИЛИ первой группы, а второй вход последнего элемента ИЛИ первой группы и вход последнего элемента НЕ второй группы соединены с последним управс ляющим входом из группы управляющих входов распределителя импульсов, выход каждого элемента НЕ первой группы соединен со второй группой входов многовходового элемента И, выход каждого элемента И третьей группы и каждого элемента И пятой группы за исключением- последнего элемента И этой группы соединены с первым и вторым входами соответствующих элементов ИЛИ второй группы, выход

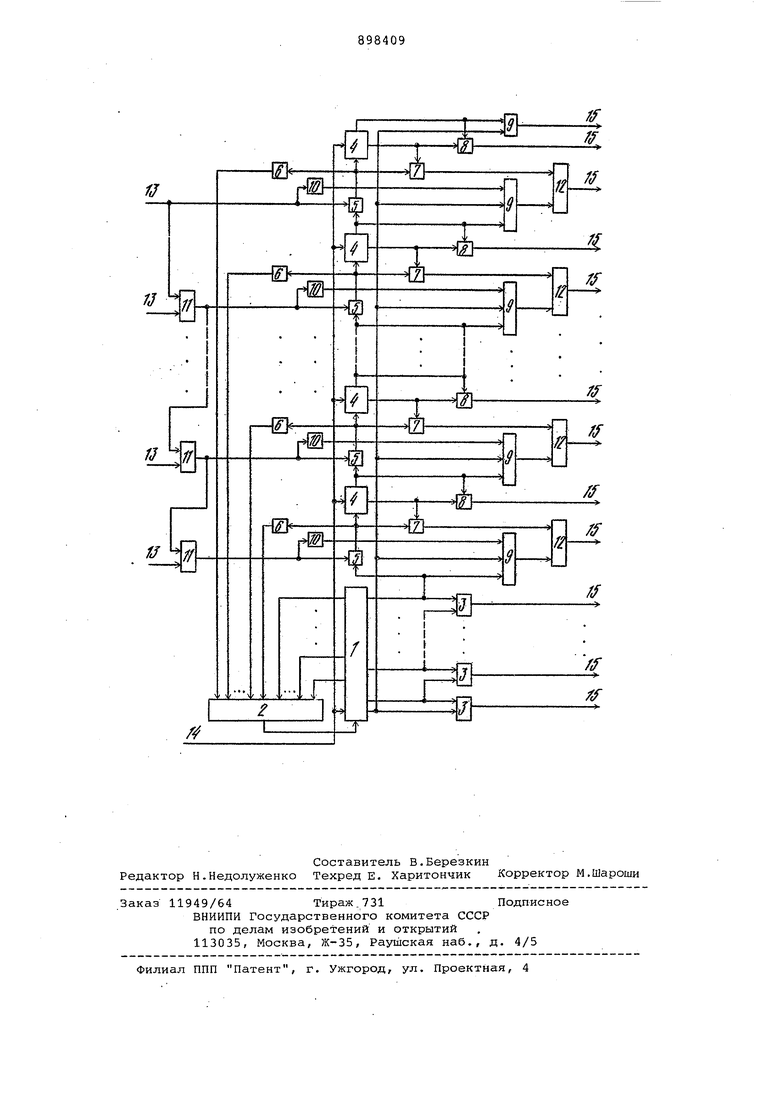

5 каждого Элемента ИЛИ второй группы, каждого элемента И четвертой группы и выход последнего элемента И пятой группы соединены с выходами распределителя импульсов. На чертеже представлена схема распределителя иг.отульсов.

В состав распределителя импульсов входят п-разрядный сдвигающий регистр 1, многовходовой элемент И

5 2, двухвходовые элементы И 3, двухразрядные сдв-игающие регистры 4, элементы И 5, элементы НЕ б, элементы И 1, элементы И 8, элементы И 9, элементы НЕ 10, элементы ИЛИ 11,

() элементы ИЛИ 12, управляющие входы 13, тактирующий вход 14, выходы 15.

Нулевые выходы четных разрядов п-разрядного сдвигающего регистра 1 за исключением последнего разряда соединены с первой группой входом многовходового элемента И 2, выход которого соединен с информационным входом п-разрядного сдвигающего регистра 1. Входы ка кдого из (п-1)-го

-. двухвходовых элементов И 3 соединены

с единичными выходами соседних разрядов п-разрядного сдвигающего регистра 1. Единичный выход последнего разряда п-разрядного сдвигающего регистра 1 и единичный выход последнего разряда камдзого из К двухразрядных сдвигающих регистров 4 за исключением последнего двухразрядного сдвигающего регистра 4 соединены последовательно через Соответствующие

0 элементы И 5 с информационными входами соответствующих двухразрядных сдвигающих регистров 4. Выход каждоТо элемента И 5 соединен со входом соответствующего элемента НЕ б со

5 входом соответствующего элемента И 7, второй вход каждого из которых соединен с единичным выходом первого разряда соответствующего двухразрядного сдвигающего регистра 4. Единичные выходы первого и второго разрядов каждого двухраэрядного сдвигающего регистра 4 соединены со входами соответствующих элементов И О, Единичный выход последнего разряда п-разрядного сдвигающего регистра Iи единичный выход последнего разря да каждого двухразрядного сдвигающего регистра 4 соединены также с первым входом соответствующих элементов И 9, второй вход каждого из которых Соединен с единичным выходом первого разряда п-разрядного сдвигающего регистра 1. Третий вход ка;кдого элемен та И 9 за исключением последнего эл мента И 9 соединен с выходом соответ ствующего элемента НЕ 10, вход каждо го из которых за исключением последнего соединен с выходом соответству|ющего элемента ИЛИ 11, первый вход каждого из которых соединен с соответствующим управляющим входом 13 распределителя импульсов. Выход каждого последующего элемента ИЛИ 11 за исключением первого элемента ИЛИ 11 соединен со вторым входом соответствующего предьщущего элемента ИЛИ 11 Второй вход каждого элемента И 5 за исключением последнего элемента И 5 coiiMii; J:i с выходом соответствующего элемента ИЛИ 11. Второй вход последнего элемента И 5, вход последнего элемента НЕ 10 и второй вход последнего элемента ИЛ IIсоединен с последним управляющим входом 13 распределителя импульсов. Выход каждого элемента НЕ 6 соединен со входом многовходового элемента И 2. Выход каждого элемента И 7 и каждого элемента И 9 за исключением последнего элемента И 9 соединены с первым и вторым входами соответствующих элементов ИЛИ 12..Вход синхронизации п-разрядного сдвигающего регистра 1 и вход синхронизации каждого двухразрядного сдвигающего регистра 4 соединены с тактирующим входом 14 распределителя импульсов. Выход каждого двухвходового элемента И 3, выход каждого элемента И 8, выход последнего элемента И 9 и выход каждого элемента ИЛИ 12 соединены с выходами 15. Распределитель импульсов работает следующим образом. Перед началом работы производится установка требуемого количества выдаваемых распределенных временных импульсов, которое определяется числом разрядов регистра подынтегральной функции и зависит от количества подсоединяемых к п-разрядному сдвигающему регистру 1 двухразрядных сдвигающих регистров 4. При этом . число выдаваемых временных импульсов может измениться от п до ln+2K). Осущ зствляется установка требуемого количества выдаваемых временных импульсов подачей разрешающего сигнала на соответствующий управляющий вход 13. Так, если необходимо получать п+2К) временных импульсов к-к;), то на К -тый управляющий вход 13 подается потенциал, который проходит через соответствующий элемент ИЛИ 11 и откроет соответствующий элемент И 5 и через соответствующий элемент НЕ 10 закроет соответствующий элемент И 9. Кроме того, сигнал с выхода этого элемента ИЛИ 11 пройдет через все предьщущке элементы ИЛИ 11, закроет все предыдущие элементы и 9 и откроет все предыдущие элементы И 5, соединив последовательно п-разрядный сдв-игающий регистр 1 и К двухразрядный сдвигающих регистров 4 (п - четное число). Кроме того, после включения источника питания через тактирующий вход 14 на вход синхронизации регистра 1 и каждого регистра 4.поступят тактирующие импульсы, которые осуществят сдвиг той случайной информации,которая записывается в регистры при включении источника питания, и так-как регистры не закольцованы, то в результате происходит их обнуление. После обнуления регистра 1 и регистров 4 на все входы многовкодового элемента И 2 поступят единичные сигналы и в результате на выходе этого элемента появится тоже единичный сигнал, который поступит на информационный вход сдвигающего регистра 1 и по тактирующему импульсу в первый разряд этого регистра запишется единица. В следующем такте подачей тактирующего сигнала на вход 14 эта единица сдвинется во второй разряд сдвигающего регистра 1, а в первый разряд запишется новая единица. Сигналы с единичных выходов соседних разрядов регистра 1 поступают на входы двухвходовых элементов И 3 и на их выходах образуЕОтся распределенные временные импульсы. Причем при записи единицы во второй разряд на одном из входов многовходового элемента И 2 появится нулевой сигнал, поступающий с нулевого выхода второго разряда регистра 1, Этот сигнал закроет элемент И 2 и прохо;едение сигнала на информационный вход регистра 1 прекратится. Записанный в сдвигающий регистр 1 сигнал, представляющий собой две единицы в соседних разрядах, сдвигается до последнего разряда и производить выработку (п-1 ) распределенных временных импульсов. После того, как записанный в регистр 1 сигнал сдвинется в последние два разряа, откроется последний элемент И 3 и выработается (п-1)-ый временной импульс. Одновременно на BCGX DXOдах -элемента И 2, соединенных с нулевыми выходами четных разрядов регистра 1 за исключением последнего разряда, единичный,сигнал, но в то же время, так как на вход первого элемента И 5 с выхода первого элемента ИЛИ 11 поступает разрешающий сигнал, то единичный сигнал с единичного выход;а последнего разряда регистра 1 одновременно поступит на информационный вход первого двухразрядного сдвигающего регистра 4 и черезпервый элемент НЕ б - на соответствующий вход многовходового элемента И 2, запрещая тем самым поступление новой единицы на информационный вход регистра 1.

Тогда в следующем такте в первый разряд первого двухразрядного сдвигающего регистра 4 запишется единица а единица из предпоследнего разряда регистра 1 перезапишется в последний разряд регистра 1 и в результате на выходе первого элемента И 7 появится п-ый временной импульс, который через соответствующий элемент ИЛИ 12 поступит на соответствующий выход группы выходов 15. В следующем такте единицы записываются в первый и второй разряды первого двухразрядного регистра 4 и на выходе первого элемента И 8 появится следующий (п-{-1)-ый временной импульс, а единичный сигнал с единичного выхода второго разряда первого регистра 4, пройдя через открытый элемент И 5, .поступит на информационный вход следующего Двухразрядного сдвигающего регистра 4 и через соответствующий элемент НЕ б на соо.тветствующий. вход многовходового элемента И 2, запрещая поступление единичного сигнала на информационный вход регистра 1,

В следующем такте произойдет сдви сигнала, состоящего из двух единиц, еще на один разряд и сдвиг этого сигнала и выработка соответствующих временных импульсов продолжается до тех пор, пока этот сигнал не пройдет последний открытый .элемент И 5 и не запишется в первый и второй разряд последнего двухразрядного сдвигающего регистра 4 из К двухразрядных регистров 4, подсоединенных к регистРУ 1.

В результате на выходе соответствующего элемента И 8 появится предпоследний временной импульс. В то же время, так как (К+1)-ый элемент И 5 второй группы этих элементов,подключенный к выходу К-ого двухразрядного сдвигающего регистра 4, закрыт, то единичный сигнал с единичного выхода второго разряда этого регистра 4 не пройдет через этот элемент И 5 и соответствующий элемент НЕ б и не поступит на вход многовходового элемента И 2, и таким образом, на всех входах второй группы входов элементов и 2, так же как и на всех входах первой группы входов этого элемента, единичные сигналы. В результате на выходе элемента И 2 тоже единичный сигнал, который поступает на информационный вход сдвигающего регистра 1. Тогда в следующем такте в первый разряд регистра 1 запишется новая единица,а единица из предпоследнего разряда К -ого двухразрядного регистра 4 запишется в последний. В результате на выходе соответствующего элемента И 9, входы которого подключены к единичному выходу второго разряда К-ого двухразрядного регистра 4, к единичндму выходу первого разряда регистра 1 и к выходу (К +1)-го элемента НЕ 10 (на входе этого элемента НЕ 10 нулевой сигнал, так как единичный сигнал подан при подготовке к работе на К-ый управляющий вход 13) появится последний (п+2 К )-временной импульс, а в следующем такте единицы записываются уже в первый и второй разряды сдвигающего регистра 1 и выработка распределенных временных импульсов начнется уже в новом цикле.

Таким образом введение новых узлов в распределитель импульсов позволяет расширить его функциональные возмолсности за счет обеспечения возможности изменять число выдаваемых временных импульсов и тем самым дает возможность изготовлять для проведения наладки решающих блоковцифровых интегрирующих структур с различной длиной разрядной сетки подынтегральной функции всего лишь один стенд проверки, а не несколько различных, что сокращает затраты на изготовление проверочной аппаратуры и уменьшает время изготовления проверочной аппаратуры.

Формула изобретения

Распределитель импульсов, содержащий п-разрядный сдвигающий регистр, группу из (n-t) двухвходовых элементов И и многовходовой элемент И, причем нулевые выходы четных разрядов п-разрядного сдвигающего регистра за исключением последнего разряда соединены со входами многовходового элемента И, выход которого соединен с информационным входом п-разрядного сдвигающего регистра, вход синхронизации которого соединен с тактирующим входом распределителя импульсов, входы каждого i-ro двухвходового элемента И первой группы (,..,n-1) соединены с единичными выходами i-го и (i +1)-го разрядов п-разрядного сдвигающего регистра, выход каждого двухвходового элемента И первой группы соединен с выходами распределителя импульсов, отличающийс я тем, что, с целью расширения функциональных возможностей за счет изменения числа выдаваемых импульсов в него дополнительно введены К двухразрядных сдвигающих регистров, четы ре группы элементов И, две группы элементов ИЛИ и две группы элементов НЕ,причем единичный выход последнего разряда п-разрядного сдвигающего регистра и единичный выход последнего разряда каждого двухразрядного сдвигающего регистра з.а исключением последнего двухразрядного сдвигающего регистра, подключены к вхо дам соответствующих элементов И второй группы, выходы которых соединены с информационными входами соответствующих двухразрядных сдвигающих регистров, вход синхронизации каждого из которых соединен с тактирующим входом распределителя импульсов, выход каждого элемента И второй группы соединен со входом соответствующего элемента НЕ первой группы и с первым ,входом соответствующего элемента И третьей группы, второй вход каждого из которых соединен с единичным выходом первого разряда соответствующего двухразрядного сдвигающего регистра, единичные выходы первого и второго разрядов каждого двухразрядного сдвигающего регистра соединены со входами соответствуккцих элементов И четвертой группы, единичный выход последнего разряда п-разрядного сдвигающего регистра и единичный выход последнего разряда каждого двухразрядного сдвигающего регистра соединены с первыми входами соответствующих элементов И пятой группы, второй вход каждого из которых соединен с единичным выходом первого разряда п-разрядного сдвигаю щего регистра, третий вход каждого элемента И пятой группы за исключена ем последнего элемента И соединен с выходом соответствующего-элемента НЕ второй группы, вход каждого из которых. за исключением последнего соединен с выходом соответствующего элемента ИЛИ первой группы, первый вход каждого из которых соединен с соответствующим управляющим,входом группы управляющих входов распределителя импульсов, выход каждого последующего элемента ИЛИ первой группы за исключением первого элемента ИЛИ этой группы соединен со вторым входом предьщущего элемента ИЛИ первой группы, второй вход каждого элемента И второй группы за исключением последнего элемента И этой группы соединен с выходом соответствующего элемента ИЛИ первой группы, второй вход последнего элемента и второй группы, второй вход последнего элемента ИЛИ первой группы и вход последнего элемента НЕ второй группы соединены с последним управляющим входом из группы управляющих вход.ов распределителя импульсов, выход каждого элемента НЕ первой группы соединен со входом многовходового элемента И, выход каждого элемента И третьей группы и каждого элемента И пятой группы за исключением последнего элемента И этой группы соединены с первым и вторым входами соответствующих элементов ИЛИ.второй группы, выход кшкдого элемента ИЛИ второй группы, каждого элемента И четвертой группы и выход последнего элемента И пятой группы соединены с выходами распределителя импульсов. Источники информации, принятые во внимание при экспертизе 1.Разработка однородной цифровой интегрирующей структуры на основе цифрового решающего модуля для реализации решающей части систем автоматического регулирования. Отчет по НИР, Гос.per, № 70016121, инв. № Б 309218, Таганрог, 1973, кн. 1, с. 119-120. 2.Исследование принципов построения спецвычисления для автоматического управления автономными адоптивными работами на основе однородных ЦИС. Отчет по НИР, Гос.per.№ 76059197, инв. № Б 564787. Таганрог, 1976, с. 126-127. 3.Разработка функциональных схем устройств цифровой интегрирующей машины для микроэлектронного управления. Отчет по НИР, Гос.per.№ 71028281, инв. № Б 162887. Таганрог, 1971, с. 24-31 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Распределитель импульсов | 1982 |

|

SU1053288A2 |

| УСТРОЙСТВО ДЛЯ РЕГИСТРАЦИИ ТЕЛЕМЕХАНИЧЕСКОЙИНФОРМАЦИИ | 1971 |

|

SU419947A1 |

| Делитель частоты импульсов с управляемым коэффициентом деления | 1980 |

|

SU877791A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU900300A1 |

| Цифровая интегрирующая структура | 1980 |

|

SU960842A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Вычислительный узел цифровой сеточнойМОдЕли для РЕшЕНия диффЕРЕНциАльНыХуРАВНЕНий B чАСТНыХ пРОизВОдНыХ | 1979 |

|

SU798859A1 |

| Преобразователь линейного позиционного кода в двоичный код | 1980 |

|

SU935944A1 |

| Элемент однородной вычислительной структуры | 1984 |

|

SU1211890A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код | 1980 |

|

SU943703A1 |

Авторы

Даты

1982-01-15—Публикация

1980-04-07—Подача