( УСТРОЙСТВО УПРАВЛЕНИЯ ПРЕРЫВАНИЕМ ПРОГРАММ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство управления прерыванием программ | 1983 |

|

SU1096647A1 |

| Устройство для отладки мультипрограммных систем | 1989 |

|

SU1735855A1 |

| Устройство для решения дифференциальных уравнений | 1982 |

|

SU1134949A1 |

| Микропрограммное устройство управления модуля вычислительной системы | 1983 |

|

SU1108447A1 |

| Диспетчер памяти ЭВМ | 1990 |

|

SU1718225A1 |

| Устройство управления взаимным доступом процессора многопроцессорной системы | 1989 |

|

SU1631548A1 |

| Устройство для сопряжения микропроцессора с системной шиной | 1990 |

|

SU1837299A1 |

| Устройство многоуровневого прерывания | 1983 |

|

SU1104516A1 |

| Процессор ввода-вывода | 1983 |

|

SU1149240A2 |

| Устройство многоуровневого прерывания | 1985 |

|

SU1287158A1 |

1

Изобретение относится к вычислительной технике и может быть использовано в мультипрограммных вычислительных системах, работающих в реаль ном масштабе времени.

Известно устройство прерывания содержащее селектор, элементы И, триггер запроса, элемент НЕ, реализующее прерывание системы при поступлении запроса l.

Недостаток этого устройства заключается в ограниченных функциональных возможностях, исключающих применение его в мультипрограммных вычис-лительных системах

Наиболее близким к изобретению по технической сущности и достигаемому результату является устройство для управления прерыванием программ, содержащее регистр запросов, два дешифратора, блок памяти, узел синхронизации, шифратор, регистры, схемы сравнения, элемент ИЛИ, узел приоритета, группы элементов И

Недостатком этого устройства является ориентация на мультипрограммные системы с разделением памяти на фиксированное число разделов опреде- ленной длины, которая должна превышать максимально возможную длину выполняемых программ, т„е, ограниченная область применения

Цель изобретения - расширение области применения устройства.

Поставленная цель достигается тем что в устройство управления прерыванием программ, содержащее первый и второй блоки элементов И, блок памяти, первый элемент ИЛИ, причем первый выход первого регистра соединен с первым входом первого блока элементов И, информационный вход первого регистра является запросным входом устройства, выход первого элемента ИЛИ является выходом прерывания устройства, выход блока памяти соединен с первым входом второго блока элементов И, введены блоки

элементов И с третьего по девятый, первый, второй блоки элементов ИЛИ блок элементов НЕ, сумматор, элементы И с первого по пятый, второй и третий элементы ИЛИ и триггер, причем второй выход первого регистра соединен с первым входом второго элемента ИЛИ и с первыми входами первого и второго элементов И, единичный выход триггера соединен со вторым входом второго элемента ИЛИ, выход второго элемента соединен с первым входом третьего блока элементов ИИ с первым входом четвертого блока элементов И, второй вход третьего блока элементов И соединен с выходом первого регистра, выход третьего блока элементов И Соединен с первым входом пятого блока элементов И, с первым входом шестого блока элементов И и через блок элементов НЕ с первым входом сумматора, первый и второй выходы сумматора соединены с первыми входами соответственно третьего и четвертого элементов И, вторые входы которых соединены с первым входом пятого элемента И и с третьим выходом первого регистра, единичный выход триггера соединен со вторым входом пятого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ,, второй вход которого соединен с выходом пер вого элемента И, второй вход первого элемента И соединен со вторым выходом сумматора, первый выход сумматора соединен со вторым входом второго элемента И и с входом седьмого блока элементов И, первый вход которого соединен с третьим выходом сумматора, выход седьмого блока элементов И соединен с информационным входом второго регистра, выход которого соединен со вторым входом чет вертого блока элементов И, выход которого соединен с первым входом первого блока элементов ИЛИ, второй вхо которого соединен с выходом второго блока элементов И, выход первого блока элементов ИЛИ соединен со вторым входом сумматора, выход третьего элемента И соединен с входом три|- гера, со вторым входом шестого блока элементов И, с управляющим входом третьего регистра и с первым входом первого элемента ИЛИ, выход второго блока элементов ИЛИ соединен с информационным входом четвертого регистра, выход четвертого регистра соединен с первым входом восьмого блока элементов И, вы ход которого является первым информационным выходом устройства, выход третьего элемента ИЛИ соединен со вторым входом первого элемента ИЛИ, со вторым входом первого блока элементов И и с первым информационным входом третьего регистра, второй информационный вход которого соединен с первым входом блока памяти, с третьим входом первого элемента ИЛИ и с выходом четвертого элемента И, выход второго элемента И соединен с четвертым входом первого элемента ИЛИ и со вторым входом пятого блока элементов И, выход которого соединен со вторым входом блока памяти и с первым входом второго блока элементов ИЛИ, второй вход которого соединен с выходом блока памяти, выход первого блока элементов И соединен с третьим входом второго блока элементов ИЛИ, четвертый вход второго блока элементов ИЛИ соединен с выходом шестого блока элементов И, выход третьего регистра соединен с первым входом девятого блока элементов И, второй вход которого соединен с первым управляющим вхоДОМ устройства и со вТорым входом восьмого блока элементов И, выход девятого блока элементов И является вторым информационным выходом устройства, второй вход второго блока элементов И соединен со вторым управляющим входомустройства.

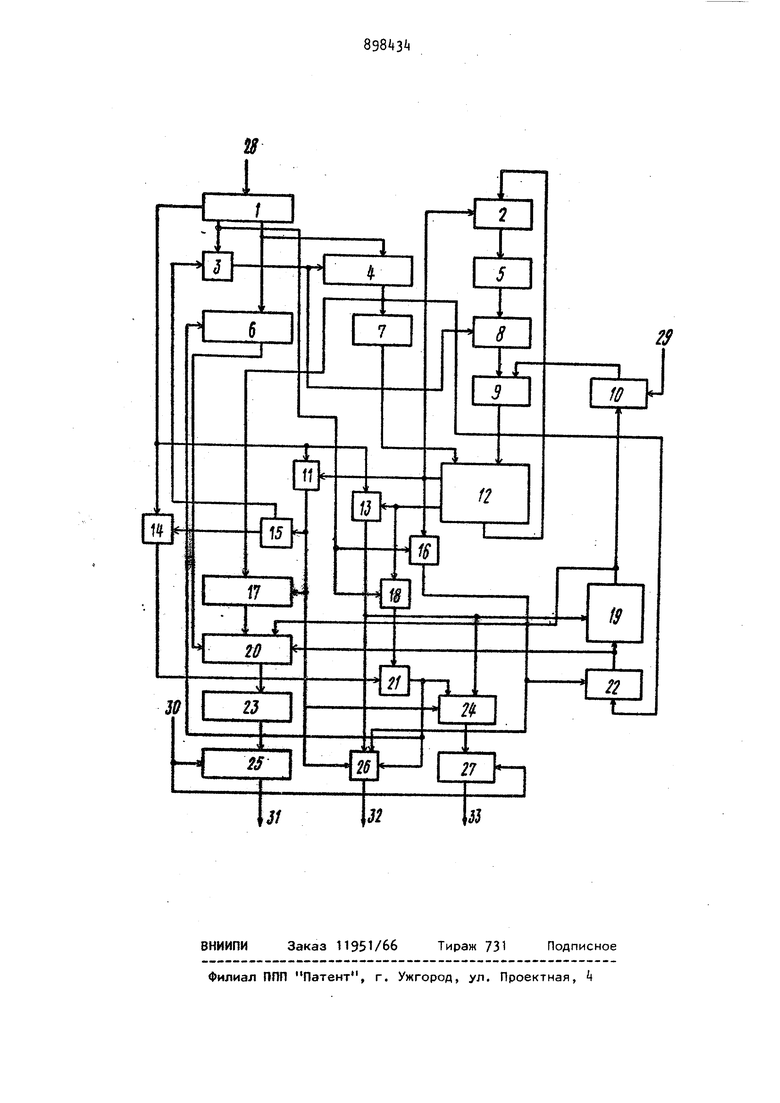

На чертеже приведена структурная схема устройства.

Устройство содержит регистр 1, блок элементов И 2, элемент ИЛИ 3, блок элементов И k, регистр 5, блок элементов И 6, блок элементов НЕ 7, блок элементов И 8, блок элементов ИЛИ 9, блок элементов И 10, элемент И 11, сумматор 12, элемент И 13, элемент И Н, триггер 15, элемент И 16, блок элементов И 17, элемент И 18, блок 19 памяти, блок элементов ИЛИ 20,

элемент ИЛИ 21 ,блок элементов И 22,регистр 23, регистр 2, блок элементов И 25, элемент ИЛИ 26, блок элементов И 27, информационный вход 28 устройства, управляющие входы 29 и 30 устройства, информационный выход 31 устройства, выход 32 прерывания устройства, информационный выход 33 устройства. 5 Устройство работает следующим образом. По информационному входу 28 в регистр 1 вводится поступивший в систему код запроса, который содержит в старшем разряде признак приоритетности, а в остальных - код количества требуемых ресурсов памяти, В зависимости от значений этих параметров, а также от начального состояния триггера 15 и регистра 5 устройством реализуется алгоритм работы. Пусть в системе выполняется приоритетная задача, т„е триггер 15 находится в состоянии 1, старший разряд регистра 1 также - в единичном состоянии и свободные ресурсы, информация о которых содержится на регистре 5, превышают ресурсы, требуемые запросом. Тогда на обоих вхо дах элемента И 14 оказываются единичные сигналы, и его выходной си|- нал через элемент ИЛИ 21 устанавливает код на регистре 24, передает содержимое регистра 1 через блоки (элементов И 6 и элементов ИЛИ 20 на регистр 23 и, наконец, через элемент ИЛИ 26 с выхода 32 посылает в систему сигнал прерывания. Этим самым инициируется работа программы прерывания в системе, в процессе которо на управляющий вход 30 поступает сиг нал, обеспечивающий считывание содер жимого регистров 23 и 24 через блоки элементов И 25 и 27 в систему с выходов 31 и 33. Предположим, что в начальном состоянии система выполняет неприоритет ные программы, т.е. триггер 15 находится в нулевом состоянии Тогда си1- нал с его инверсного выхода через элемент ИЛИ 3 стробирует передачу кода ресурсов с регистра 1 через бло элементов И 4 и блок элементов НЕ 7 на сумматор 12, а также кода свободных ресурсов с регистра 5 через блок элементов И 8, ИЛИ 9 в прямом виде. В данном случае разность на сумматоре оказывается с положительным знаком, т„ео на первом управляющем выходе сумматора устанавливается единичный сигнаЛо В результате через блок элементов И 2 содержимое сумматора пересылается в регистр 5 и срабатывает элемент И 11, выходным сигналом которого содержимое регистра 1 передается через блоки элементов И 4 и 17, ИЛИ 20 на регистр 23, а также 3 устанавливается в 1 триггер 15 и формируется сигнал прерывания на выходе 32. Регистр 24 также устанавливается в нулевое состояние, что соответствует постановке запроса на решение. Вслед за этим срабатывает элемент И 16, который своим выходны м сигналом передает код ресурсов запроса с выхода группы элементов И через группу элементов И 22 в блок памяти 19 и через блок элементов ИЛИ 20 на регистр 23. Если ресурсы в системе меньше ресурсов запроса, на сумматоре образуется разность с отрицательным знаком, которая не пересылается на регистр 5 о В результате срабатывает элемент И 18, выходной сигнал которого через элемент ИЛИ 21 записывает код в регистр 2, что соответствует операции постановки запроса в очередь, затем через блок элементов И 6 передает содержимое регистра 1 через блок элементов ИЛИ 20 на регистр 23 и, наконец, через элемент ИЛИ 26 формирует сигнал прерывания о Наиболее сложная последовательность действий вырабатывается при работе устройства, когда в системе решаются не приоритетные задачи, но для выполнения поступившего приоритетного запроса не хватает свободных ресурсов памяти. После того, как на . сумматоре появляется отрицательная разность,срабатывает элемент И 13. Его выходной сигнал поступает на управляющий вход блока памяти 19 и производит считывание информации о ресурсах, занимаемых последним поставленным на решение неприоритетным запросом. Эта информация поступает через блок элементов ИЛИ 20 на регистр 23. Кроме того, сигнал с выхода элемента И 13 устанавливает на регистре 2k операций код и через элемент ИЛИ 26 формирует сигнал прерывания Программа прерывания, получив описанным ранее путем информацию с регистров 23 и 2, производит упрятывание последней неприоритетной задачи, т,е. освобождение занимаемых ею ресурсов памяти. После завершения процесса упрятывания на вход 29 устройства из системы поступает сигнал, который пересылает код ресурсов задачи через блок элементов ИЛИ 9 и блок элементов И 10 в прямом виде 7 на сумматор. Если результат на сумматоре оказывается опять отрицательным, вновь срабатывает элемент И 13 и цикл повторяется. Так продолжается до тех пор, пока знак результата на сумматоре не становится положительным Тогда результат через блок элементов И 2 пересылается на регистр 5 и, кроме того срабатывает элемент И 11. Его выходной сигнал устанавливает в 1 триггер 15 и в нулевое состояние регистр 24, передает через блоки элементов И 17, ИЛИ 20 код запроса с выхода блока элементов И на регистр 23 и через элемент ИЛИ 2б формирует сигнал пре рывания. Таким образом, устройство позволяет эффективно загрузить систему поступающими заявками и обеспечить оперативную постановку приоритетных заявок на обслуживание, независимо от наличия свободных ресурсов памяти что делает возможным применение его как в обычных мультипрограммных системах, так и в системах реального вр мени, т„е. расширить область примене ния устройства. формула изобретения Устройство управления прерыванием программ, содержащее четыре регистра первый и второй блоки элементов И, блок памяти, первый элемент ИЛИ, причем первый вйход первого регистра соединен с первым входом первого блока элементов И, информационный вход первого регистра является просным входом устройства, выход первого элемента ИЛИ является выходом прерывания устройства, выход блока памяти соединен с первым входом второго блока элементов И, о тличающееся тем, что, с целью расширения области применения устройство содержит блоки элементов И с третьего по девятый, первый вто рой блоки элементов ИЛИ, блок элементов НЕ, сумматор, элементы И с первого по пятый, второй и третий элементы ИЛИ, триггер, причем второ выход первого регистра соединен с первым входом второго элемента ИЛИ и с первыми входами первого и второ го элементов И, единичный выход три гера соединен со вторым входом втор го элемента ИЛИ, выход второго элемента ИЛИ соединен с первым входом третьего блока элементов И и с первым входом четвертого блока элементов И, второй вход третьего блока элементов И соединен с первым выходом первого регистра, выход третьего блока элементов И соединен с первым входом пятого блока элементов И с первым входом шестого блока элементов И и через блок элементов НЕ с первым входом сумматора, первый и второй выходы сумматора соединены с первыми входами соответственно третьего и четвертого элементов И, вторые входы которых соединены с первым входом пятого элемента И, и с третьим выходом первого регистра, единичный выход триггера соединен со вторым входом пятого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, второй вход первого элемента И соединен со вторым выходом сумматора, первый выход сумматора соединен со вторым входом второго элемента И и с входом седьмого блока элементов И, первый вход которого соединен с третьим выходом сумматора, выход седьмого блока элементов И соединен с информационным входом второго регистра, выход которого соединен со вторым входом четвертого блока элементов И, выход, которого соединен с первым входом первого блока элементов ИЛИ, второй вход которого соединен с выходом второго блока элеменIтов и, выход первого блока элементов ИЛИ соединен со вторым входом сумматора, выход третьего элемента И соединен с входом триггера, со вторым входом шестого блока элементов И, с управляю1цим входом третьего регистра и с первым входом первого элемента ИЛИ, выход второго блока элементов ИЛИ соединен с информационным входом четвертого регистра, выход четвертого регистра соединен с первым входом восьмого блока элементов И, выход которого является первым информационным выходом устройства, выход третьего элемента ИЛИ соединен со вторым входом первого элемента ИЛИ,со вторым входом первого блока элементов И и с первым информационным входом третьего регистра, второй информационный вход которого соеди

нен с первым входом блока памяти, с третьим входом первого элемента ИЛИ и с выходом четвертого элемента И, выход второго элемента И соединен с четвертым входом первого элемента ИЛИ и со вторым входом пятого блока элементов И, выход которого соединен со вторым входом блока памяти и с первым входом второго блока элементов ИЛИ, второй вход которого соединен с выходом блока памяти, выход первого блока элементов И соединен с третьим входом второго блока элементов ИЛИ, четвертый вход второго блока элементов ИЛИ соединен с выходом шестого блока элементов И, выход третьего регистра соединен с первым входом девятого блока элементов И, второй вход которого соединен с первым управляющим входом устройства и со вторым входом восьмого блока элементов И, выход девятого блока элементов И, является вторым информационным выходом устройства, второй вход второго блока элементов И соединен со вторым управляющим входом устройства.

Источники информации, принятые во внимание при экспертизе

2,Авторское свидетельство СССР

Н б9б1«59, кл. G 06 F 9/18, 1976 (прототип) ,

Авторы

Даты

1982-01-15—Публикация

1980-04-24—Подача