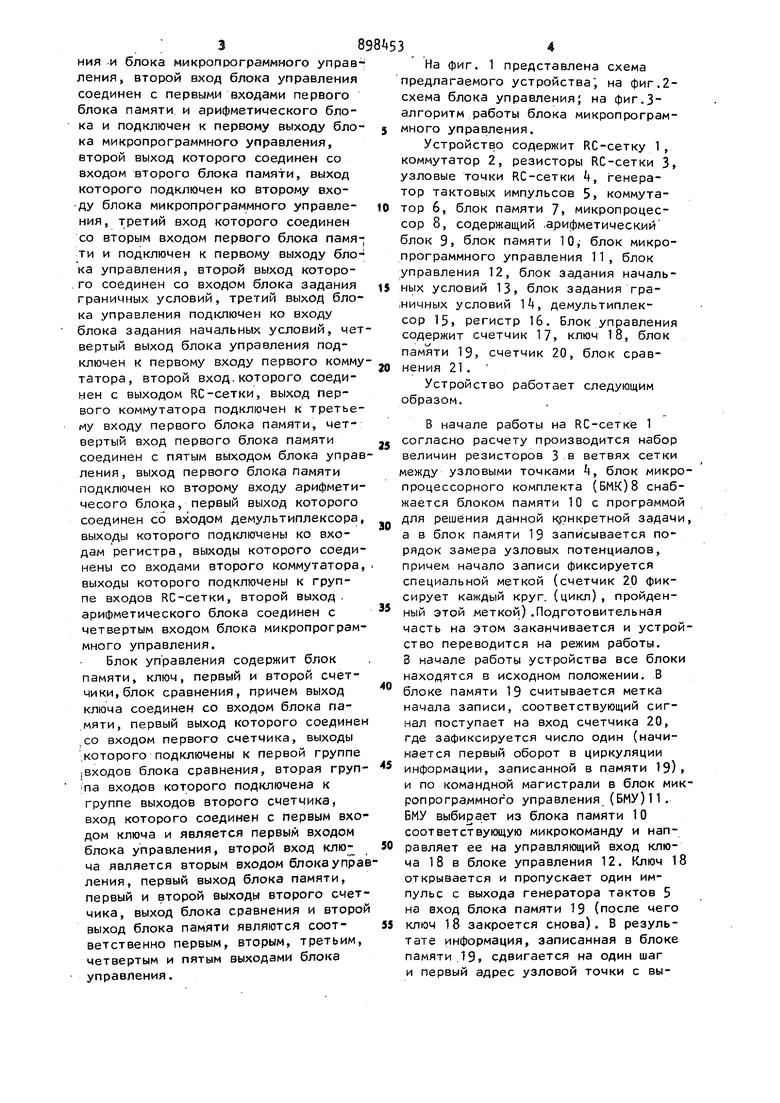

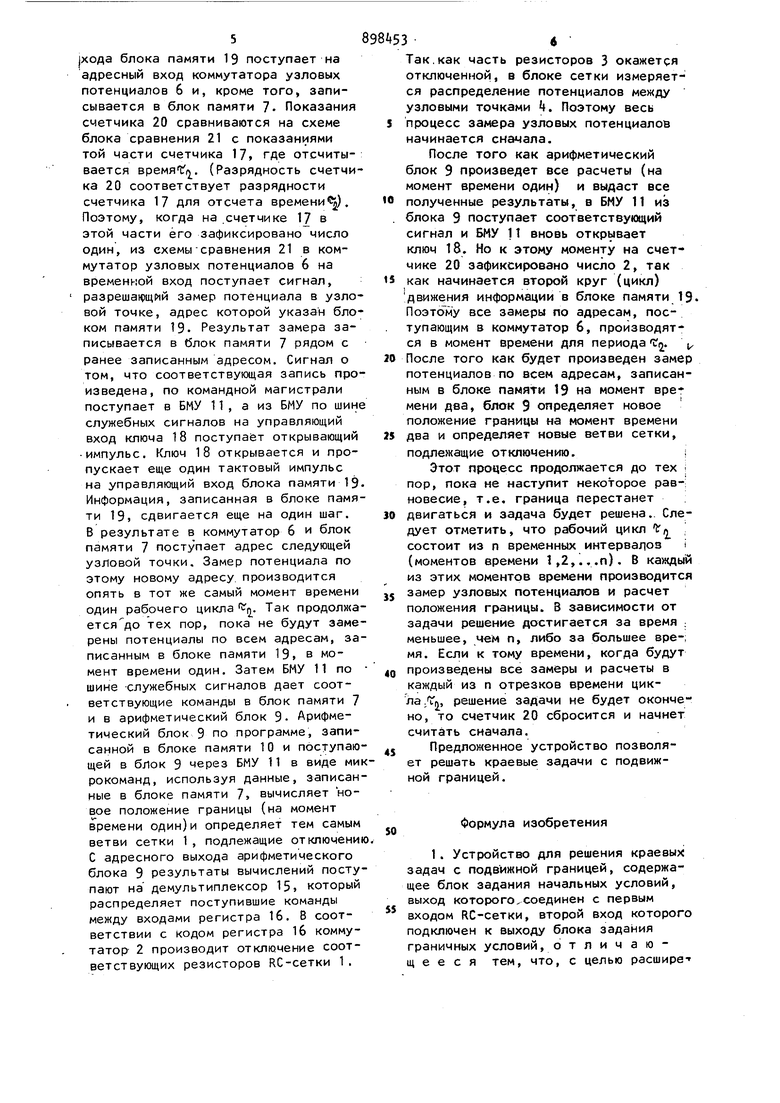

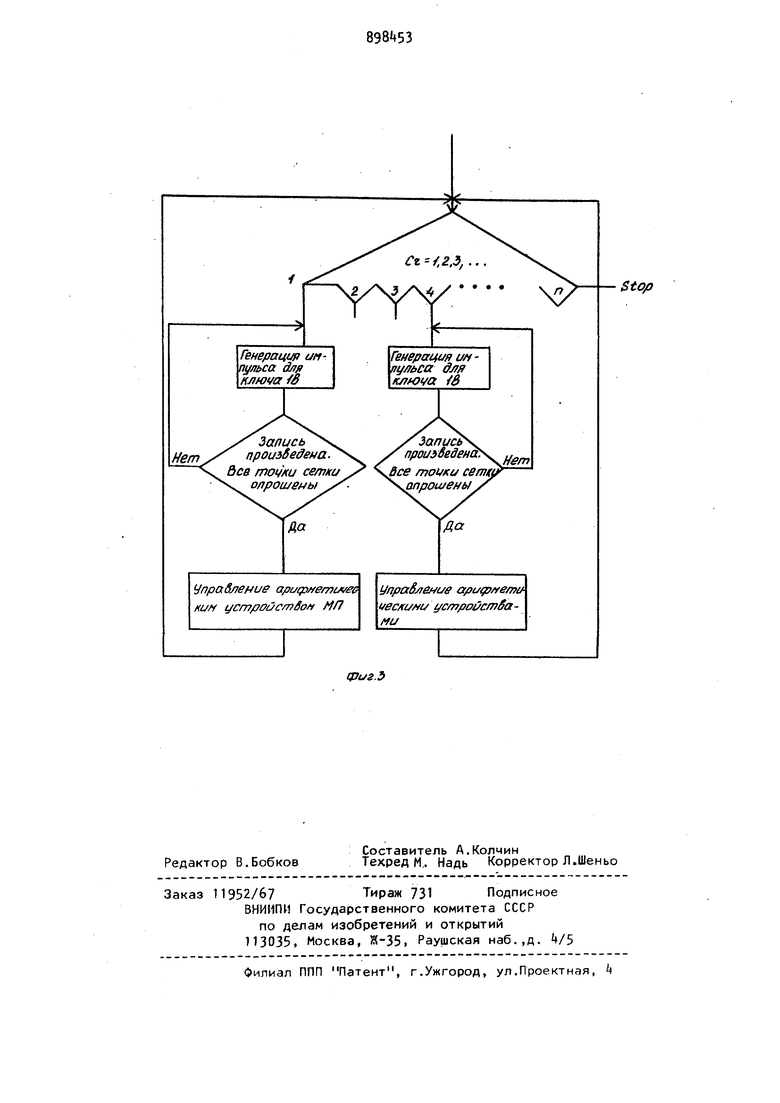

Изобретение относится к вычислительной технике и может быть примене но для решения краевых задач с подви ной границей. Известно электромоделирующее устроиство для решения краевых задач с подвижной границей раздела фаз, содержащее блок модели сетки, блоки начальных и граничных условий 1. Недостатком известного устройства является, то, что общая площадь и конфигурация сетки остаются неизменными, хотя граница раздела фаз изменяется в процессе решения задачи. Наиболее близким по технической сущности к изложенному является устройство, содержащее блок RC, блоки сравнения, блок задания граничных условий, блок задания начальных условий tz. Недостатком данного устройства является то, что в нем можно лишь изменять параметры R и С в зависимос ти от положения движущейся границы, которое определяется потенциалами в узловых точках сетки, но нельзя изменять площадь и конфигурацию работающей части RC-сетки. Цель изобретения - расширение класса решаемых задач за счет обеспечения возможности реконфигурации RC-сетки. Поставленная цель достигается тем, что в устройство для решения краевых задач с подвижной границей, содержащее блок задания начальных условий, выход которого соединен с первым входом RC-сетки, второй вход которой подключен к выходу блока задания граничных, условий, дополнительно введены первый и второй коммутаторы регистр, демультиплексор, первый и второй блоки памяти, арифметический блок, блок микропрограммного управления, блок управления, генератор тактовых импульсов, причем выход генератора тактовых импульсов подключен к первым входам блока управле; 38 ния и блока микропрограммного управ ления, второй вход блока управления соединен с первыми входами первого блока памяти и арифметического блока и подключен к первому выходу блока микропрограммного управления, второй выход которого соединен со входом второго блока памяти, выход которого подключен ко второму входу блока микропрограммного управления, третий вход которого соединен со вторым входом первого блока памяти и подключен к первому выходу блока управления, второй выход которо,го соединен со входом блока задания граничных условий, третий выход блока управления подключен ко входу блока задания начальных условий, чет вертый выход блока управления подключен к первому входу первого комму татора, второй вход.которого соединен с выходом RC-сетки, выход первого коммутатора подключен к третьему входу первого блока памяти, четвертый вход первого блока памяти соединен с пятым выходом блока управ ления , выход первого блока памяти подключен ко второму входу арифметичесого блока, первый выход которого соединен со входом демультиплаксора выходы которого подключены ко входам регистра, выходы которого соеди нены со входами второго коммутатора выходы которого подключены к группе входов RC-сбтки, второй выход, арифметического блока соединен с четвертым входом блока микропрограм много управления. Блок управления содержит блок памяти, ключ, первый и второй счетчики, блок сравнения, причем выход ключа соединен со входом блока памяти, первый выход которого соедине .со входом первого счетчика, выходы которого подключены к первой группе |Входов блока сравнения, вторая груп ;па входов которого подключена к группе выходов второго счетчика, вход которого соединен с первым вхо дом ключа и является первый входом блока управления, второй вход клю- ча является вторым входом блока упра ления, первый выход блока памяти, первый и второй выходы второго счет чика, выход блока сравнения и второ выход блока памяти являются соответственно первым, вторым, третьим, четвертым и пятым выходами блока управления. 3 На фиг. 1 представлена схема предлагаемого устройства; на фиг.2схема блока управления; на фиг.Залгоритм работы блока микропрограммного управления. Устройство содержит RC-сетку 1, коммутатор 2, резисторы RC-сетки 3, узловые точки RC-сетки i|, генератор тактовых импульсов 5, коммутатор 6, блок памяти 7, микропроцессор 8, содержащий .арифметический блок 9, блок памяти 10, блок микропрограммного управления 11, блок управления 12, блок задания начальных условий 13, блок задания гра.ничных условий 1, демультиплексор 15, регистр 16. Блок управления содержит счетчик 17, ключ 18, блок памяти 19, счетчик 20, блок сравнения 21 . Устройство работает следующим образом. В начале работы на RC-сеткё 1 согласно расчету производится набор величин резисторов 3 в ветвях сетки между узловыми точками k, блок микропроцессорного комплекта (БМК)8 снабжается блоком памяти 10 с программой для решения данной конкретной задачи, а в блок памяти 19 записывается порядок замера узловых потенциалов, причем начало записи фиксируется специальной меткой (счетчик 20 фиксирует каждый круг, (цикл), пройденный этой меткой).Подготовительная часть на этом заканчивается и устройство переводится на режим работы. В начале работы устройства все блоки находятся в исходном положении. В блоке памяти 19 считывается метка начала записи, соответствующий сигнал поступает на вход счетчика 20, где зафиксируется число один (начинается первый оборот в циркуляции информации, записанной в памяти 19), и по командной магистрали в блок микропрогра.ммного управления (БМУ)11 . БМУ выбирает из блока памяти 10 соответствующую микрокоманду и направляет ее на управляющий вход ключа 18 в блоке управления 12. Ключ 18 открывается и пропускает один импульс с выхода генератора тактов 5 на вход блока памяти 19 (после чего ключ 18 закроется снова). В результате информация, записанная в блоке памяти 19, сдвигается на один шаг и первый адрес узловой точки с выjxofla блока памяти 19 поступает на адресный вход коммутатора узловых потенциалов 6 и, кроме того, записывается в блок памяти 7. Показания счетчика 20 сравниваются на схеме блока сравнения 21 с показаниями той части счетчика 17, где отсчитывается времяС/, (Разрядность счетчи ка 20 соответствует разрядности счетчика 17 для отсчета времени). Поэтому, когда на .счетчике 17 в этой части его зафиксировано число один, из схемы-сравнения 21 в коммутатор узловых потенциалов 6 на временной вход поступает сигнал, разрешащйй замер потенциала в узло вой точке, адрес которой указан бло ком памяти 19. Результат замера записывается в блок памяти 7 рядом с ранее записанным адресом. Сигнал о том, что соответствующая запись про изведена, по командной магистрали поступает в ЕМУ 11, а из БМУ по шин служебных сигналов на управляющий вход ключа 18 поступает открывающий импульс. Ключ 18 открывается и пропускает еще один тактовый импульс на управляющий вход блока памяти 19 Информация, записанная в блоке памя ти 19, сдвигается еще на один шаг. В результате в коммутатор 6 и блок памяти 7 поступает адрес следующей узловой точки. Замер потенциала по этому новому адресу, производится опять в тот же самый момент времени один рабочего цикла г. Так продолжа етсядо тех пор, пока не будут заме рены потенциалы по всем адресам, за писанным в блоке памяти 19, в момент времени один. Затем БМУ 11 по шине служебных сигналов дает соответствующие команды в блок памяти 7 и в арифметический блок 9. Арифметический блок 9 по программе, записанной в блоке памяти 10 и поступаю щей в блок 9 через БМУ 11 в виде ми рокоманд, используя данные, записан ные в блоке памяти 7, вычисляет новое положение границы (на момент времени один)и определяет тем самым ветви сетки 1, подлежащие отключени С адресного выхода арифметического блока 9 результаты вычислений посту пают на демультиплексор 15, который распределяет поступившие команды между входами регистра 16. В соответствии с кодом регистра 16 коммутатор 2 производит отключение соответствующих резисторов RC-сетки 1. 3« Так.как часть резисторов 3 окажется отключенной, в блоке сетки измеряется распределение потенциалов между узловыми точками . Поэтому весь процесс замера узловых потенциалов начинается сначала. После того как арифметический блок Э произведет все расчеты (на момент времени один) и выдаст все полученные результаты, в БМУ 11 из блока 9 поступает соответствующий сигнал и БМУ 11 вновь открывает ключ 18. Но к этому моменту на счетчике 20 зафиксировано число 2, так как начинается второй круг (цикл) движения информации в блоке памяти 19. Поэт6 му все замеры по адресам, поступающим в коммутатор 6, производятся в момент времени для периода t. После того как будет произведен замер потенциалов по всем адресам, записанным в блоке памяти 19 на момент времени два, блок 9 определяет новое положение границы на момент времени два и определяет новые ветви сетки, подлежащие отключению.: Этот процесс продолжается до тех пор, пока не наступит некоторое рав-; новесие, т.е. граница перестанет : двигаться и задача будет решена. Следует отметить, что рабочий цикл lr,j состоит из п временных интервалов i (моментов времени 1,2,...п). В каждый из этих моментов времени производится замер узловых потенциалов и расчет положения границы. В зависимости от задачи решение достигается за время : меньшее, чем п, либо за большее вре-; мя. Если к тому времени, когда будут произведены все замеры и расчеты в каждый из п отрезков времени цикла .fft, решение задачи не будет окончено, то счетчик 20 сбросится и начнет считать сначала. Предложенное устройство позволяет решать краевые задачи с подвижной границей. Формула изобретения 1. Устройство для решения краевых задач с подвижной границей, содержащее блок задания начальных условий, выход которого,соединен с первым входом RC-сетки, второй вход которого подключен к выходу блока задания граничных условий, о т л и ч а ю щ е е с я тем, что, с целью расшире- ния класса решаемых задач за счет обеспечения возможности реконфигурации КС-сетки, в устройство дополнительно введены первый и второй коммутаторы, регистр, демультиплексор, первый и второй блоки памяти, арифметический блок, блок микропрограммного управления, блок управления, генератор тактовых импульсов, причем выход генерато ра тактовых импульсов подключен к первым входам блока упразленця и блока микропрограммного управления, второй вход блока управления соединен, с первыми входами первого блока памяти и арифметического блока и подключен к первому выходу блока микропрограммного управ ления, второй выход которого соединен со входом второго блока памяти, выход которого подключен ко второму входу блока микропрограммного управления, третий вход которого соединен со вторым входом первого блока памяти и подключен к первому выходу блока управления, второй выход кoтo рого соединен со входом блока задания граничных условий, третий выход блока управления подключен ко входу блока задания начальных условий, чет вертый выход блока управления подключей к первому входу первого комму татора, второй вход которого соедине с выходом RC-сетки, выход первого коммутатора подключен к третьему входу первого блока памяти, четверты вход первого блока памяти соединен с пятым выходом блока управления, вы ход первого блока памяти подключен ко второму входу арифметического 89 8 блока, первый выход которого соединен со входом демультиплексора, выходы которого подключены ко входам регистра, выходы которого соединены со входами второго коммутатора, выходы которого подключены к группе входов RC-сетки, второй выход арифметического блока соединен с четвертым входом блока микропрограммного управления. 2. Устройство по п.1, о т л и чающееся тем, что блок управления содержит блок памяти, ключ, первый и второй счетчики, блок сраане ния, причем выход ключа соединен со входом блока памяти, первый выход которого соединен со входом первого счетчика, выходы которого подключены к первой группе входов блока сравнения, вторая группа входов которого подключена к группе выходов второго счетчика, вход которого соединен с первым входом ключа и является первым входом блока управления, второй вход ключа является вторым входом блока управления, первый выход блока памяти, первый и второй выходы второго счетчика, выход блока сравнения и второй выход блока памяти являются соответственно первым, вторым, третьим, четвертым и пятым выходами |блока управления. Источники информации, принятые во внимание при экспертизе 1.Авторское свитедельство СССР f. I84it72, кл. G.06 G , 1966. 2.Авторское свидетельство СССР Г (, кл. G Об G , 19б5 (прототип),

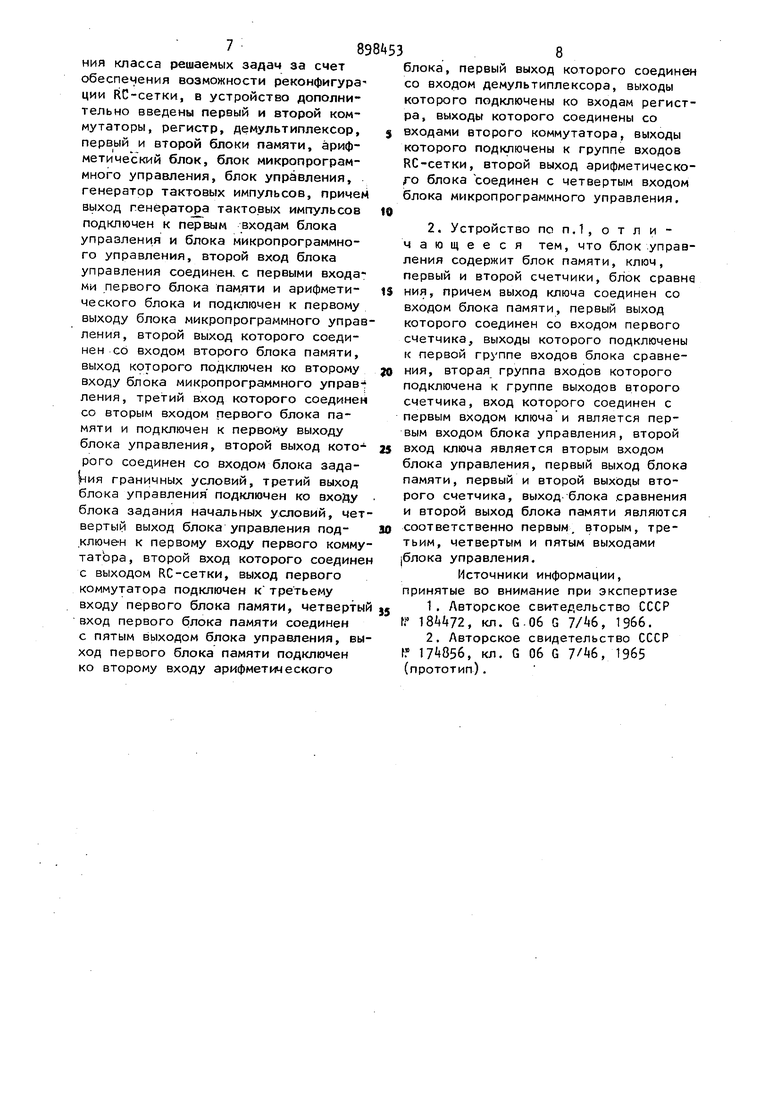

Stofl

Упра&пеиие apLfipf/efnuveG ким ycm/youcmSoff МП

Генерация uff ауаьса dJfff Kflfova /В

Упра&леиив apugfffefmf vecxuMi/ ycmpoi/cfnSaми

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439618A1 |

| Устройство для решения обратных задач теории поля | 1984 |

|

SU1164748A1 |

| Сеточная модель | 1984 |

|

SU1260981A1 |

| Микропрограммное устройство сопряжения | 1989 |

|

SU1700560A1 |

| Функциональный преобразователь многих переменных | 1990 |

|

SU1742836A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1425706A1 |

| Устройство для измерения характеристик синусоидального сигнала | 1985 |

|

SU1307366A1 |

| Сеточная модель | 1987 |

|

SU1483469A1 |

| Устройство для решения краевых задачуРАВНЕНий МАТЕМАТичЕСКОй физиКи | 1979 |

|

SU840959A1 |

Авторы

Даты

1982-01-15—Публикация

1979-12-10—Подача