Изобретение относится к вычислительной технике и может быть использовано для построения различных узлов и устройств цифровых ЭВМ.

Известен управляемый арифметический модуль, содержащий четыре информационных входа и шесть управляющих входов, два выхода, триггер и логические элементы И, ИЛИ , НЕ l.

Недостатком этого модуля является то, что он имеет ограниченные возможности по реализации математических операций, что ухудшает характеристики конструируемых на его основе узлов н устройств. Кроме того, модуль сложен в управлении.

Наиболее близким по технической сущности к предлагаемому является управляемый арифметический модуль, содержащий триггер, по два элемента И, ИЛИ и РАВНОЗНАЧНОСТЬ, два коммутатора, три информационных входа, вход прекоса, вход разрешения выполнения операции, девять управляющих входов и два

выхода, причем управляющие входы nqpвого коммутатора подключены к yigjaanH юшим входам модуля, а его информационные входы - к инфсрмационным входам модуля, выход первого коммутатора сое- . динен со входом первого элемента РАВНОЗНАЧНОСТЬ, второй вход которого является управляющим входом модуля, а выход соединен с управояюшим входом второго коммутатора, второй управляющий

10 вход которого соединен с выходом второго элемента РАВНОЗНАЧНОСТЬ, первый вход которого является управляющим входом модуля, а второй соединен с выходом триггера, счетный вход которого

15 соединен с выходом первого элемента ИЛИ, первый вход которого соединен со входом переноса устройства, а второй с выходом второго коммутатора, информационные входы которого подключены

20 к управляющим входам модуля, а его стробирующяй вход соединен со входом ра ешения вьшолнения операции, входы Первого элемента И соединены со

входом переноса модуля, с выходом второго элемента РАВНОЗНАЧНОСТЬ и с первым Входом второго элемента И, второй вход которого соединен с выходом второго элемента РАВНОЗНАЧНОСТЬ, третий вход является управляющим входом модуля, а его четвертый вход подключен ко входу ра: ёшения выполнения операции, выходы элементов И соединены со входами второго элемента ИЛИ, выход которого является выходом переноса устройства, а выход триггера

является выходом результата устройства 2.

Недостатком известного устройства является его сложность, а также щэедъявление жестких требований к параметрам импульсного сигнала разрешения выполнения операции с целью обеспечения устойчивой работы схемы.

Цель изобретения - упрощение конструкции.

Поставленная цель достигается тем, что управляемый арифметический модуль, содержащий элементы РАВНОЗНАЧНОСТЬ и ИЛИ, два элемента И, триггер и два коммутатора, настроечные входы первого из которых являются управляющими вхо- дами модуля, а информационные входы подключены к информационным входам устройства, выход триггера яёляется выходом результата модуля, информационные входы второго коммутатора являются управляющими входами модуля, выход элемента ИЛИ является выходом переноса модуля, а его входы соединены с выходами элементов И, первые входы которых подключены соответственно ко входу переноса устройства и выходу первого коммутатора, содержит элемент НЕ и третий элемент И, выход которого соединен со входом элемента ИЛИ, его первый вход соединен с выходом первого коммутатора, а второй вход объединен со вторым входом второго элемента И и является управляющим входом модуля, третьи входы второго и третьего эле- ментов И соединены соответственно с прямым и инверсным выхода1у й триггера а их четвертые и пятые входы соединены соответственно с первым и вторым, третьим и четвертым информационными входами второго коммутатора, выход которого соединен со входом элемента РАВНОЗНАЧНОСТЬ, другой вход которого подключен ко входу переноса модуля, а выход соединен со входом первого элемента И и входом элемента НЕ, а

также с единичным входом триггера, выход элемента НЕ соединен с нулевым входом триггера, синхровход триггера является синхровходом модуля, дополнитель- . ный информационный вход модуля является информационным входом первого коммутатора.

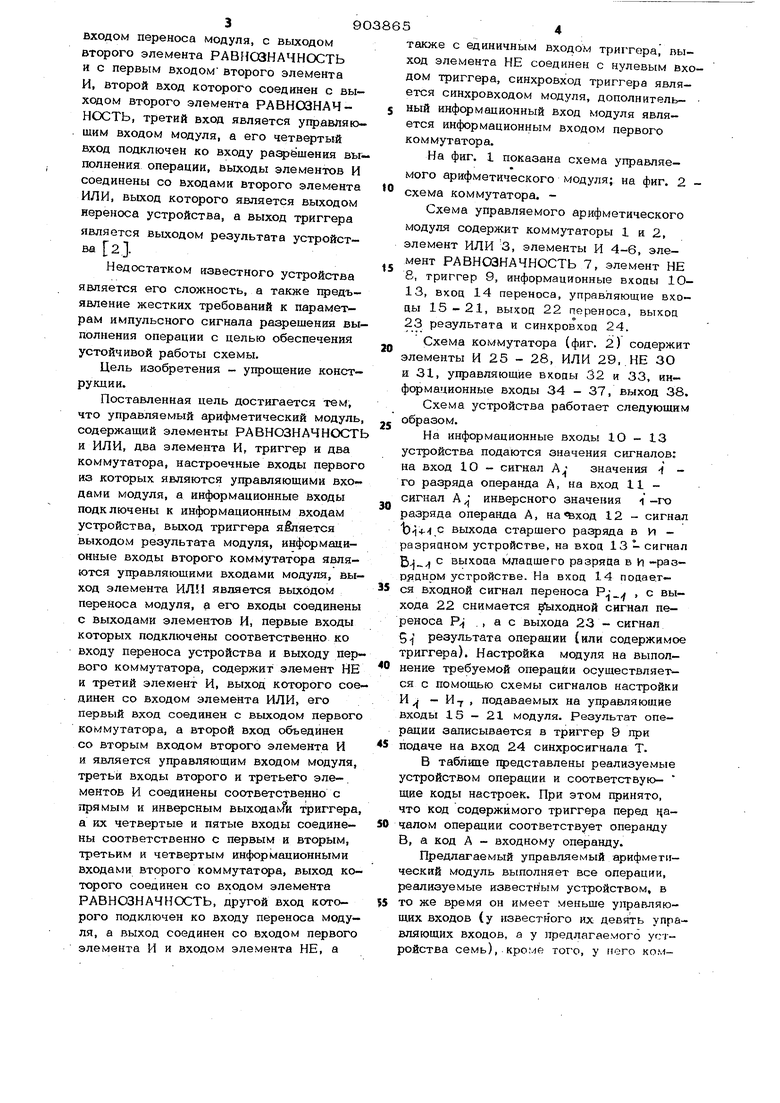

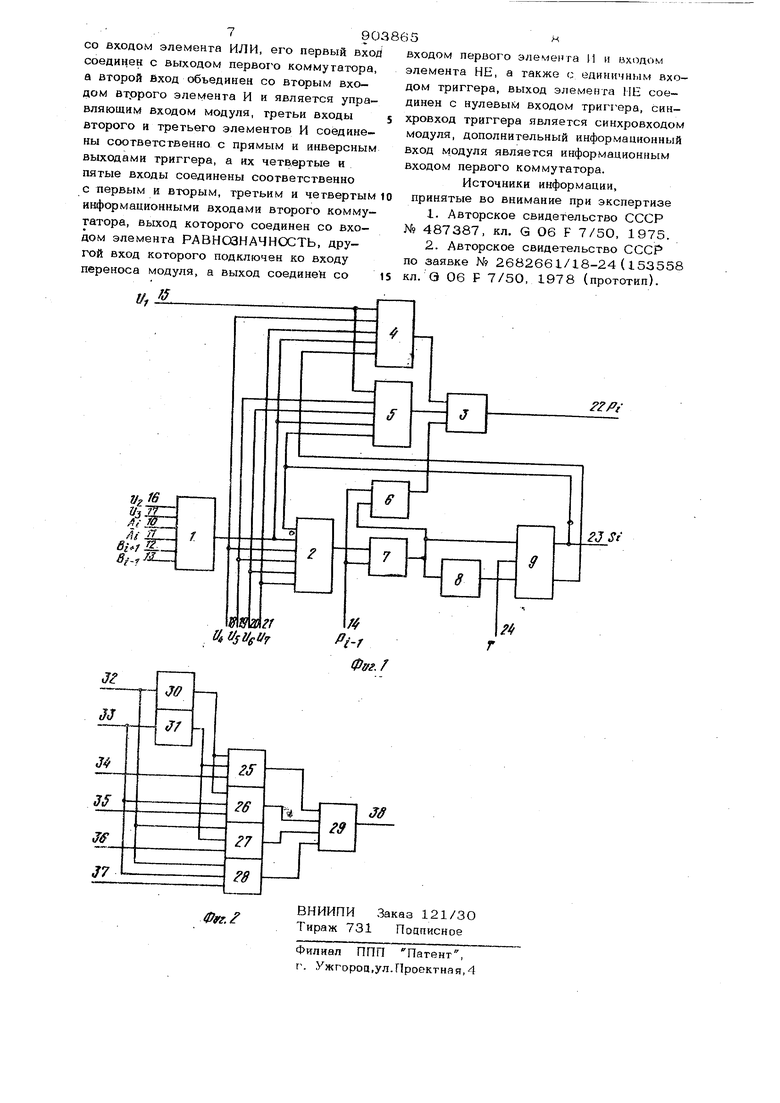

На фиг. I показана схема управляе

мого арифметического модуля; на фиг. 2 схема коммутатора. Схема управляемого арифметического модуля содержит коммутаторы 1 и 2, элемент ИЛИ З, элементы И 4-6, элемент РАВНОЗНАЧНОСТЬ 7, элемент НЕ 8, триггер 9, информационные входы 1013, вход 14 переноса, управляющие входы 15-21, выхоц 22 переноса, выход 23 результата и синхровхоа 24.

Схема коммутатора (фиг, 2) содержит элементы И 25 - 28, ИЛИ 29,. НЕ ЗО и 31, управляющие вхопы 32 и 33, информационные входы 34 - 37, выход 38. Схема устройства работает следующим

образом.

На информационные входы Ю - 13 устройства подаются значения сигналов; на вход Ю - сигнал значения -i го разряда операнда А, на вход 11 сигнал А : инверсного значения i -го разряда операнда А, на«Ьход 12 - сигнал bi-H с выхода старщего разряда в И разряциом устройстве, на вхоа 13 - сигнал ЪА-. с выхода младшего разряда в И -разрядирм усгройсгве. На вход 14 поцае.т5 ся входной сигнал переноса Рл , с выхода 22 снимается Уходной сигнал переноса Р ., а с выхода 23 - скгнал результата операции {или содержимое триггера). Настройка модуля на выпол0 Нение требуемой операции осуществляется с помощью схемы сигналов настройки И - И-т . подаваемых на управляющие входы 15-21 модуля. Результат операции записывается в триггер 9 при

5 подаче на вход 24 синхросигнала Т.

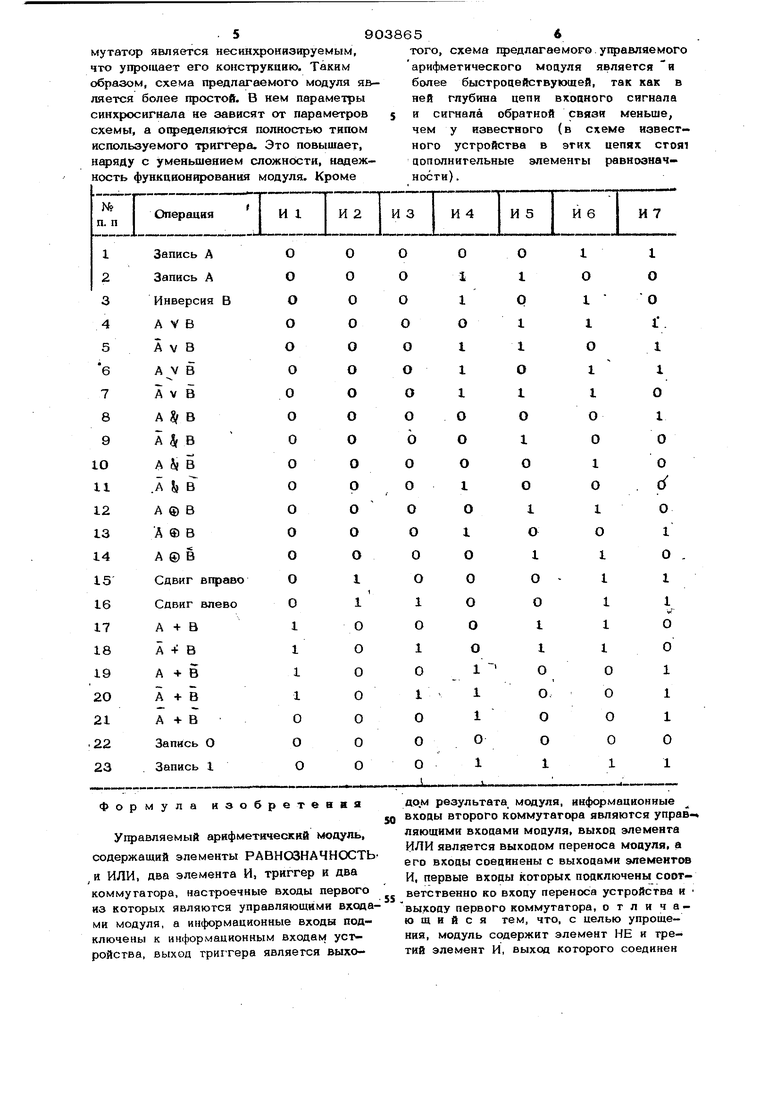

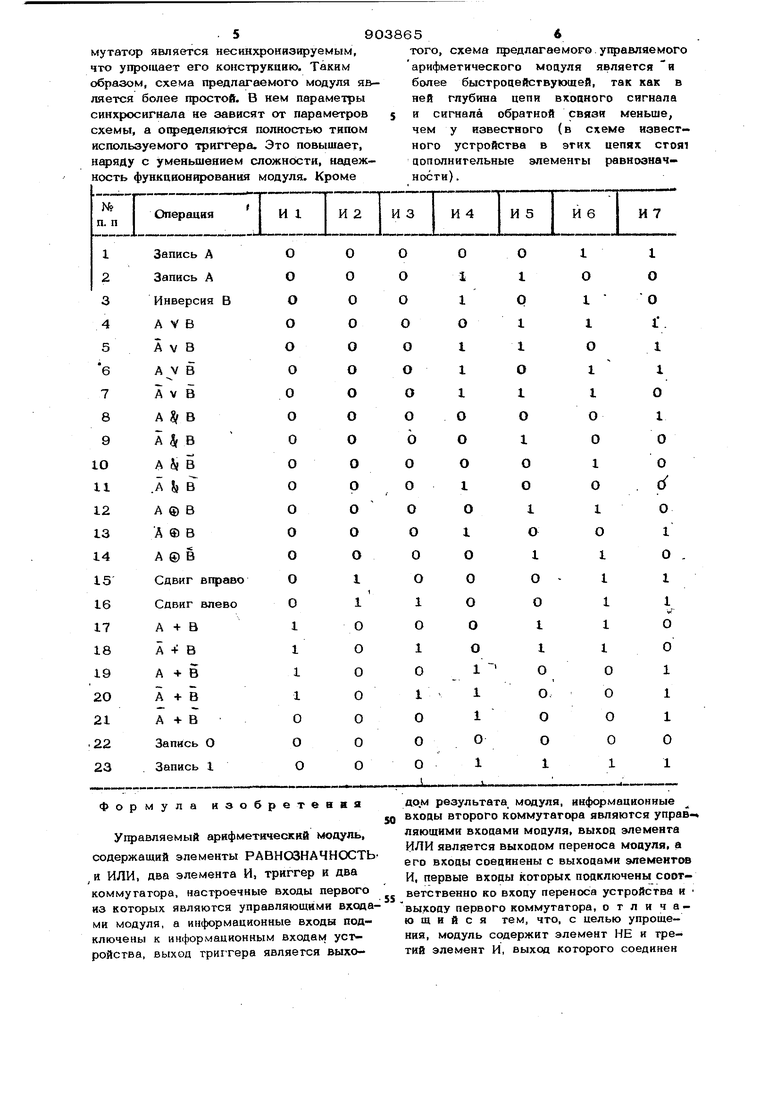

В таблице гфедставлены реализуемые устройством операции и соответствующие коды настроек. При этом принято, что код содержимого триггера перед ца0 чалом операции соответствует операнду В, а код А - входному операнду.

Предлагаемый управляемый арифметический модуль выполняет все операции, реализуемые известным устройством, в

то же время он имеет меньше управляющих входов (у известггого их девять управляющих входов, а у предлагаемого устройства семь), кроме того, у гтего коммутатор является несинхрониэируемым, что упрощает его конструкцию. Таким образом, схема предлагаемого модуля является более простой, В нем параметры синхросигнала не зависят от параметров схемы, а определяются полностью типом используемого триггера. Это повышает, с уменьшением сложнсюти, надежность функцеюнированш модуля. Кроме

того, схема предлагаемого ущэавляемого арифметического модуля является и более быстроцействующей, так как в ней глубина цепи вхоиного сигнала и сигнала обратной связи меньше, чем у известного (в схеме известного устройства в этих цепях стоя1 цополнительные элементы равнозначности) .

| название | год | авторы | номер документа |

|---|---|---|---|

| Управляемый арифметический модуль | 1979 |

|

SU855654A1 |

| Управляемый арифметический модуль | 1978 |

|

SU802961A1 |

| Управляемый арифметический модуль | 1985 |

|

SU1309017A1 |

| Адаптивное вычислительное устройство | 1984 |

|

SU1203506A1 |

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

| Вычислительное устройство с совмещением операций | 1989 |

|

SU1716528A1 |

| Арифметическо-логическое устройство | 1979 |

|

SU822180A1 |

| Процессор с совмещением операций | 1982 |

|

SU1138805A1 |

| СПОСОБ ЦИФРОВОЙ ОБРАБОТКИ СИГНАЛОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2163391C1 |

| Вычислительное устройство | 1980 |

|

SU1022158A1 |

Формула иаобретевия Управляемый арифметический модуль, содержащий элементы РАВНСвНАЧНОСТЬи ИЛИ, два элемента И, триггер и два коммугатора, настроечные входы первого из которых являются управляющими входами модуля, а информационные входы подключены к информационным входам устройства, выход триггера является выходо.м результата модуля, информационные входы второго коммутатора являются управ- ляющими входами модуля, выход элемента ИЛИ является выходом переноса модуля, а его входы соединены с выходами элементов И, первые входы которых подключены соответственно ко входу переноса устройства и выходу первого коммутатора, о т л и ч аю щ и и с я тем, что, с целью упрощения, модуль содержит элемент НЕ и третий элемент И, выход которого соединен со входом элемента ИЛИ, его первый Bxod соединен с выходом первого коммутатора, а второй Вход объединен со вторым входом второго элемента И и является управляющим входом модуля, третьи входы второго и третьего элементов И соединены соответственно с прямым и инверсным выходами триггера, а их четвертые и пятые входы соединены соответственно с первым и вторым, третьим и четвертым информационными входами второго коммутатора, выход которого соединен со входом элемента РАВНОЗНАЧНОСТЬ, другой вход которого подключен ко входу переноса модуля, а выход соединен со IE i( д.- /./ЖГ .уЖ- ттгг I/, t/sl/ffffT входом первого элемента И и их1адом элемента НЕ, а также с единичным входом триггера, выход элемента НЕ соединен с нулевым входом триггера, синхровход триггера является синхровходом модуля, дополнительный информационный вход модуля является информационным входом первого коммутатора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 487387, кл. G Об F 7/50, 1975. 2.Авторское свидетельство СССР по заявке N 2682661/18-24(153558 кл. Q 06 F 7/50, 1978 (прототип).

Авторы

Даты

1982-02-07—Публикация

1980-01-07—Подача