Изобретение относится к вычислительной технике, в частности к устройствам памяти на полупроводниковых приборах.

Целью изобретения является повышение быстродействия оперативного запоминающего устройства.

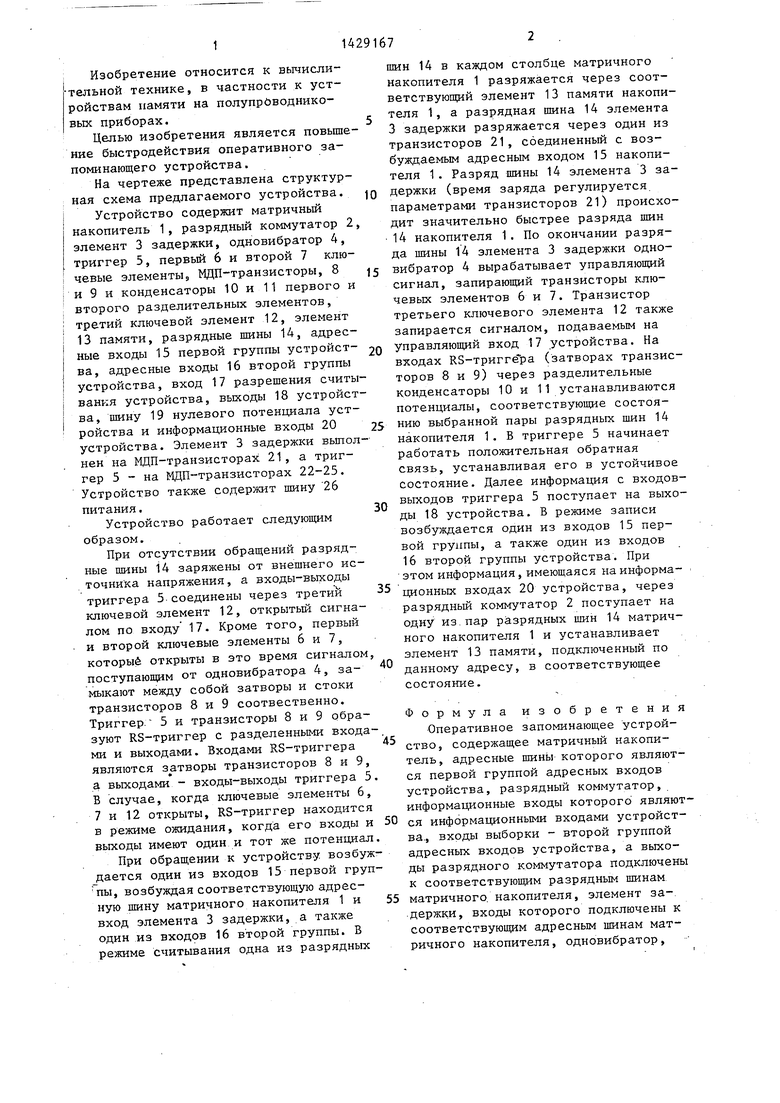

На чертеже представлена структурная схема предлагаемого устройства.

Устройство содержит матричный накопитель 1, разрядный коммутатор 2, элемент 3 задержки, одновибратор 4, триггер 5, первьй 6 и второй 7 ключевые элементы5 МДП-транзисторы, 8 и 9 и конденсаторы 10 и 11 первого и второго разделительных элементов, третий ключевой элемент 12, элемент 13 памяти, разрядные шины 14, адресные входы 15 первой группы устройст- ва, адресные входы 16 второй группы устройства, вход 17 разрешения считывания устройства, выходы 18 устройства, шину 19 нулевого потенциала устройства и информационные входы 20 устройства. Элемент 3 задержки вьшол- нен на МДП-транзисторах 21, а триггер 5 - на МДП-транзисторах 22-25. Устройство также содержит шину 26 питания.

Устройство работает следующим образом.

При отсутствии обращений разрядные шины 14 заряжены от внешнего источника напряжения, а входы-выходы триггера 5 соединены через третий ключевой элемент 12, открытый сигналом по входу 17. Кроме того, первый и второй ключевые элементы 6 и 7, которые открыты в это время сигналом поступающим от одновибратора 4, замыкают между собой затворы и стоки транзисторов 8 и 9 соотвественно. Триггер. 5 и транзисторы 8 и 9 образуют RS-триггер с разделенными входа ми и выходами. Входами RS-триггера являются затворы транзисторов 8 и 9, а выходами - входы-выходы трихтера 5 Б случае, когда ключевые элементы 6, 7 и 12 открыты, RS-триггер находится в режиме ожидания, когда его входы и выходы имеют один.и тот же потенциал При обращении к устройству возбуж дается один из входов 15 первой груп пы, возбуждая соответствующую адресную шину матричного накопителя 1 и вход элемента 3 задержки, а также один из входов 16 вто.рой группы. В режиме считывания одна из разрядных

0 5

5 0 5

0

шин 14 в каждом столбце матричного накопителя 1 разряжается через соот- ветствуюшлй элемент 13 памяти накопителя 1, а разрядная шина 14 элемента 3 задержки разряжается через один из транзисторов 21, соединенный с возбуждаемым адресным входом 15 накопителя 1. Разряд шины 14 элемента 3 задержки (время заряда регулируется параметрами транзисторов 21) происходит значительно быстрее разряда шин 14 накопителя 1. По окончании разряда шины 14 элемента 3 задержки одно- вибратор 4 вырабатывает управляющий сигнал, запираюшлй транзисторы ключевых элементов 6 и 7. Транзистор третьего ключевого элемента 12 также запирается сигналом, подаваемым на управляющий вход 17 устройства. На входах RS-триггё ра (затворах транзисторов 8 и 9) через разделительные конденсаторы 10 и 11 устанавливаются потенциалы, соответствующие состоянию выбранной пары разрядных шин 14 накопителя 1. В триггере 5 начинает работать положительная обратная связь, устанавливая его в устойчивое состояние. Далее информация с входов- выходов триггера 5 поступает на выходы 18 устройства. В режиме записи возбуждается один из входов 15 первой группы, а также один из входов 16 второй группы устройства. При этом информация, имеющаяся на информационных входах 20 устройства, через разрядный коммутатор 2 поступает на одну из.пар разрядных шин 14 матричного накопителя 1 и устанавливает элемент 13 памяти, подключенный по данному адресу, в соответствующее состояние.

Формула изобретения

Оперативное запоминающее устройство, содержащее матричный накопитель, адресные шины которого являются первой группой адресных входов устройства, разрядный коммутатор, информационные входы которого являются информационными входами устройства., входы выборки - второй группой адресных входов устройства, а выходы разрядного коммутатора подключены к соответствующим разрядным шинам матричного, накопителя, элемент задержки, входы которого подключены к соответствующим адресным шинам матричного накопителя, одновибратор.

вход которого соединен с выходом элемента задержки, первый и второй ключевые элементы на МДП-транзисто- рах, затворы которых соединены с выходом одновибратора, триггер,.входы- выходы которого являются выходами устройства и соединены с истоками МДП-транзисторов первого и второго ключевых элементов соответственно, третий ключевой элемент на МДП-тран- зисторе, исток и сток которого соединены с первым и вторым входами-выходами триггера соответственно, а затвор является входом разрешения считывания устройства, отличающееся тем, что, с целью повьше

ния быстродействия устройства, оно содержит разделительные элементы, выполненные на конденсаторах и МДП- TpaH3HCTOpaXj истоки которых подключены к шине нулевого потенциала устройства, стоки соединены, с первым и вторым входами-выходами триггера соответственно, а затворы - с первыми обкладками соответствующих конденсаторов и со стоками МДП-транзисторов первого и второго ключевых элементов соответственно, вторые обкладки конденсаторов разделительных элементов соединены с соответствующими информационными входами разрядного коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Оперативное запоминающее устройство | 1985 |

|

SU1283854A1 |

| Постоянное запоминающее устройство | 1986 |

|

SU1388950A1 |

| Матрица постоянного запоминающего устройства | 1983 |

|

SU1348908A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU842964A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1990 |

|

SU1756939A1 |

| Полупроводниковое запоминающее устройство | 1984 |

|

SU1238157A1 |

| Устройство для записи информации в МДП динамический-матричный накопитель | 1982 |

|

SU1091222A1 |

| Запоминающее устройство | 1985 |

|

SU1269209A1 |

| Матричный накопитель для постоянного запоминающего устройства | 1988 |

|

SU1778790A1 |

| Усилитель считывания | 1981 |

|

SU1015435A1 |

Изобретение относится к вычислительной технике, Б частности к устройствам памяти на полупроводниковых приборах. Целью изобретения является повьшение быстродействия оперативного запоминающего устройства. Устройство содержит матричный накопитель 1, разрядный коммутатор 2, элемент 3 задержки, одновибратор 4, триггер 5, , ключевые элементы 6, 7 МДП-транзисто- рЫ 8, 9, конденсаторы 10 и 11 разделительных элементов, ключевой элемент 12, элемент 13 памяти, разрядные шины 14, шину 19 нулевого потенциала, шину 26 питания. Элемент задержки вьшолнен на МДП-транзисторах 21, а триггер 5,- на МДП-транзисторах 22-25. 1 ил. - .f ю

| Запоминающее устройство | 1982 |

|

SU1109804A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Оперативное запоминающее устройство | 1985 |

|

SU1283854A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-10-07—Публикация

1987-01-06—Подача