. г . . ;

: изобретение относится к контрольно-измерительной технике и может быть ийпользованр при проверке блоков и элементов цифровых устройств.

Известно устройство, контроля цифровых .элементовj содержащее . эталонный элемент и блок сравнения индикации il. . .

Это устройство .не позволяет производить контроль на предельной рабочей частоте.

Наиболееблизким к изобретению по технической сущности является устройство, содержащее блок управления, генератор тактовых импульсов, соединенный с генератором псевдослучайных воздействий, с выходами которого соединены контролируемый и этало зныйэлементы, выходы которых соединены с входом блока сравнений, выход которого соединен через триггер с .индикатором 23.

Однако данное устройство не позволяет контролировать цифровые элеменТЫ, задержки в которых могут превышать период тактовых импульс }в на их предельной рабочей частоте.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения возможности кон.троля цирфовых элементов., задержки в которых могут превышать период тактовых импульсов.

Эта цель достигается тем, что в

10 устройство для динамических испытаний цифровых элементов, содержащее блок управления, генератор тактовых, импульсов, генератор псевдослучайных воздействий, с ш 1ходами которого

15 соединены входы эталонного и проверяемого элементов, блок сравнения, входы которого соединены с выходами эталонного и проверяемого элементов, триггер индикации, соединенный с

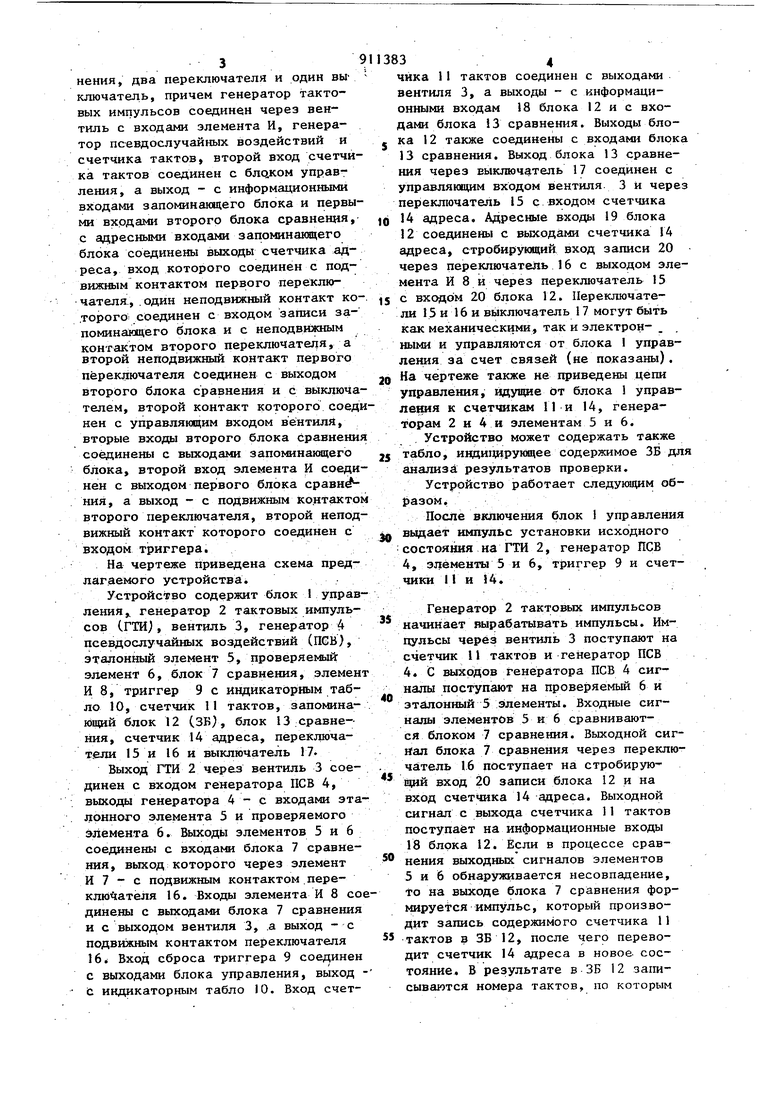

20 блоком управления, и индикаторное табло, введены вентиль, элемент И, .счетчик тактов, счетчик адресов, за:поминаюощй блок, второй блок срав3нения, два переключателя и один выключатедь, причем генератор тактовых импульсов соединен через вентиль с входами элемента И, генератор псевдослучайных воздействий и счетчика тактов, второй вход счетчи ка тактов соединен с управг ления, а выход - с информационными входами запоминающего блока и первы ми входами второго блока сравнения, с адресными входами запоминакщего блока соединены выходы счетчика адреса, вход которого соединен с подвижным контактом первого переключателя, .один неподвижный контакт ко торого: соединен с входом записи запоминающего блока и с неподвижным контактом второго переключателя, а второй неподвижный контакт первого переключателя соединен с выходом второго блока сравнения и с выключа телем, второй контакт которого соед нен с управляющим входом вентиля, вторые входы второго блока сравнени соединены с выходами запоминающего блока, второй вход элемента И соеди нен с выходом itepiBoro блока сравн ния, а выход - с подвижным контакто второго переключателя, второй непод вижный контакт которого соединен с входом триггера. На чертеже приведена схема предлагаемого устройства. Устройство содержит блок 1 управ ления,, генератор 2 тактовых импульсов (ГТЙ, вентиль 3, генератор псевдослучайных; воздействий (ПСВ}, эталонный элемент 5, проверяемый элемент 6, блок 7 сравнения, элемен И 8, триггер 9 с индикаторным табло 10, счетчик 11 тактов, запоминающий блок 12 СЗБ, блок 13 сравне-ния, счетчик 14 адреса, переключатели 15 и 16 и выключатель 17. Выход ГТИ 2 через вентиль 3 соединен с входом генератора ПСВ 4, выходы генератора 4 - с входами эта лонного элемента 5 и проверяемого элемента 6. Выходы элементов 5 и 6 соединены с входами блока 7 сравнения, выход которого через элемент И 7 - с подвижным контактом переклю ателя 16. Входы элемента И 8 со динены с выходами блока 7 сравнения и с выходом вентиля 3, .а выход - с подвижным контактом переключателя 16. Вход сброса триггера 9 соединен с выходами блока управления, выход с индикаторным табло 10. Вход счет34чйка 1I тактов соединен с выходами вентиля 3, а выходы - с информационными входам 18 блока 12 и с входами блока 13 сравнения. Выходы блока 12 также соединены с входами блока 13 сравнения. Выход блока 13 сравнения через выкгаочатель 17 соединен с управляющим входом вентиля 3 и через переключатель 15 с входом счетчика 14 адреса. Адресные входы 19 блока 12 соединены с выходами счетчика 4 адреса, стробирующий вход записи 20 через переключатель 16с выходом элемента И 8 и через переключатель 15 с входом 20 блока 12. Переключатели 15 и 16 и выключатель 17 могут быть как механическими, так и электронными и управляются от блока 1 управления за счет связей (не показаны). На чертеже также не приведены цепи управления, идущие от блока 1 управления к счетщ1кам II и 14, генераторам 2 и 4 и элементам 5 и 6. Устройство может содержать также табло, икдшщрующее содержимое ЗБ для анализа, результатов проверки. Устройство работает следукнцим образом. После включения блок 1 управления выдает импульс установки исходного состояния на ГТИ 2, генератор ПСВ 4, элементы 5 и 6, триггер 9 и счетчики II и 14. Генератор 2 тактовых импульсов начинает вырабатывать импульсы. Импульсы через вентиль 3 поступают на счетчик П тактов и генератор ПСВ 4. С выходов Генератора ПСВ 4 сигналы поступает на проверяемый б и эталонший 5 элементы. Входные сигналы элементов 5 и 6 сравниваются блоком 7 сравнения. Выходной сигнал блока 7 сравнения через переключатель 16 поступает на стробирующий вход 20 записи блока 12 и на вход счетчика 14 адреса. Выходной сигнал с выхода счетчика 11 тактов поступает на информационные входы 18 блока 12. Если в процессе сравнения выходных сигналов элементов 5 и 6 обнаруживается несовпадение, То на выходе блока 7 сравнения формируется импульс, который производит запись содержимого счетчика I1 тактов в ЗБ 12, после чего переводит счетчик 14 адреса в новое состояние. В рез1ультате в ЗБ 12 записываются номера тактов, по которым

произошло несовпадение выходных сигналов проверяемого и эталонного элементов.

После заполнения счетчика 11 тактов его выходной сигнал поступает на блок I управления, который, в свою очередь, останавливает генератор 2 тактовых импульсов, вновь выдает импульс устан-овки генератора пев, эталонно1 о 5 и проверяемого 6 элементов, триггера 9 и счетчиков 1I и 14 в исходное состояние

Блок 1 управления устанавливает переключатели 15 и 16 в нижнее по схеме положение, выключатель 17 в замкнутое и вновь разрешает генерацию тактовых импульсов. В результате происходит, как и s описанном случае, генерация еигналов ПСВ и сравнение выходных сигналов эталонного и проверяемого элементов. Однако когда в процессе счета номер такта совпадет с первым номером, хранящимся в ЗБ, выходной сигнал с блока 13 сравнения через выключатель 17 поступает на вентиль 3 и запрещает поступление одного тактового импульса на генератор ПСВ 4, счетчик П тактов и элемент И. В результате сигнал несовпадения, вызванный задержкой отклика, превышающий один такт, но меньший двух тактов, не проходит через элемент И, и триггер 9 остается в исходном состоянии. Если же несовпадение вызвано задержкой отклика более чем н два такта или неисправностью проверемого устройства, то сигнал с блока 7 сравнения по первому тактовому импульсу, идущему за пр(эпущенным, переключает триггер 9 в состояние, противоположное исходному, и загорается табло 10 Брак.

Импульс с выхода блока.13 сравнения переключает также счетчик 14 адреса в следующее состояние, и устройство продолжает .сравнение откликов в следующих тактах до заполнени счетчика 11, после чего блок 1 управления -останавливает работу усройства. Если все несовпадения вызываются задержками в появлении откликов, не превьш1ающими одного такта, то на триггер сигнал переключения he поступает ни разу, и он остается в исходном состоянии, что соответствует исправности проверяемой ячейки. Если же хотя бы одно несовпдение вызывается задержкой отклика более чем на два такта или неисправ ностью проверяемого устройства, ТО триггер 9 переключается, и загорается табло Брак, которое остает ся гореть и после окончания проверки. Если в устройстве установлено табло, инди1 рующее . содержимое ЗБ, то по информации, записанной в ОЗУ,

можно определить, на скольких тактах и на каких конкретно произошло несовпадение, проанализировать доступность увеличения задержки на этих тактах и принять более обоснованное реше

ние о исправности проверяемой ячейки.

Предлагаемое устройство позволяет проверять на рабочей частоте ячейки, задержки в которых могут превы-. шать период тактовых импульсов, что существенно расширяет область применения предлагаемого устройства по сравнению с областью применения из- вестного.

25

Формула изобретения

Устройство для динамических испытаний цифровых элементов, содержащее блок управления, генератор тактовых импульсов, генератор псевдослучайных воздействий, с выходами которого соединены входы эталонного н проверяемого элементов, блок сравнения, входы которого соединены с выходами эталонного и проверяемого элементов, триггер индикации, соединенный с блоком управления, и индикаторное табло, отличающееся тем, что, с целью расширения.функциональных возможностей, в него введены вентиль, элемент И, сче-Гчик тактов, счетчик адресов, запоминающий блок, второй блок сравнения, два переключателя и один выключатель, причем генератор тактовых импульсов соединен через вентиль с входами элемента И, reHepaTopia псевдослучайных воздейстВИЙ и счетчика тактов, второй вход счетчика тактов соединен с блоком управления, а выход - с информаци онными входами запоминающего блока и первыми входами второго блока сравнения, с адресными входами запоминающего блока соединены выходы счетчика адреса, вход которого соединен с подвижным контактом первого переключателя, один неподвижный кон-,

79

такт которого соединен с входом записи запоьшнающего блока и с непод-вижным контактом второго переключателя, а второй неподвижный контакт .первого переключателя соединен с выходом второго блока сравнения и с выключателем, второй контакт которого соединен с управляющим входом вентиля, вторые входы второго блока сравнения соединены с выходами запоминающего блока, второй вход элемента И соединен с выходом первого

113838

блока сравнения, а выход - с подвишш .контактом второго переключателя, второй неподвижный контакт которого соединен с входом триггера.

S

Источники информации,

принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 483633, кл. .G 01 Н 31/28, .1975. 10 2. Авторское свидетельство СССР № 530287, кл. G 01 R 31/28, 1976 (прототип). . .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля цифровых узлов | 1984 |

|

SU1231506A1 |

| Устройство для контроля цифровых блоков | 1981 |

|

SU1037259A1 |

| Устройство для поиска неисправностей в логических узлах | 1981 |

|

SU970283A1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Устройство для контроля микропроцессорных блоков | 1988 |

|

SU1531099A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| Устройство контроля микропроцессорных блоков | 1986 |

|

SU1332320A2 |

| Устройство для задания тестов | 1983 |

|

SU1141379A2 |

| Цифровой компаратор | 1987 |

|

SU1552136A1 |

| Устройство для контроля цифровых узлов | 1987 |

|

SU1483456A1 |

Авторы

Даты

1982-03-07—Публикация

1980-02-22—Подача