(S) УСТРОЙСТВО для ВЫЧИСЛЕНИЯ МОДУЛЯ КОМПЛЕКСНОГО ЧИСЛА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления модуля комплексного числа | 1981 |

|

SU1001085A1 |

| Устройство для вычисления модуля комплексного числа | 2016 |

|

RU2618188C1 |

| Устройство для вычисления модуля комплексного числа | 1982 |

|

SU1104505A2 |

| Устройство для вычисления модуля комплексного числа | 1984 |

|

SU1193662A1 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1287151A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1315999A1 |

| Устройство для вычисления квадратного корня | 1986 |

|

SU1359778A1 |

| Устройство для вычисления модуля комплексного числа | 1984 |

|

SU1233145A1 |

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1983 |

|

SU1115060A1 |

| Устройство для выполнения быстрого преобразования Фурье | 1980 |

|

SU940168A1 |

1

Изобретение относится к вычислительной технике.

Известно устройство для вычисления квадратного корня из суммы квадратов двух чисел, содержащее регистры, сумматоры и логические элементы fl 3«

Известно также устройство для вычисления модуля комплексного числа, которое содержит два регистра, два сумматора, два коммутатора, два блока сдвига, элементы НЕ, блок анализа знака, причем знаковые разряды регистров соединены с входами блока анализа знаков, выход его соединен с управляющими входами коммутаторов, на остальные входы коммутаторов поступают сигналы с выходов блоков сдвига, а также с выходов схем НЕ, подключенных к выходам блоков сдвига, входы блоков сдвига соединены с выход ми регистров, выходы коммутаторов соединены с входами сумматоров,вто2

рые входы которых соединены с выходами регистров f2 J., .

Недостатком известных устройств Является их значительная сложность.

Цель изобретения - уггрощение устройства.

Указанная цель достигается тем, что в устройстве для вычисления модуля комплексного числа, содержащем регистры, сумматоры и коммутаторы,

to причем входы первого и второго регистров подключены к первому и второму информационным входам устройства, прямые выходы разрядов первого регистра подключены к группе первых

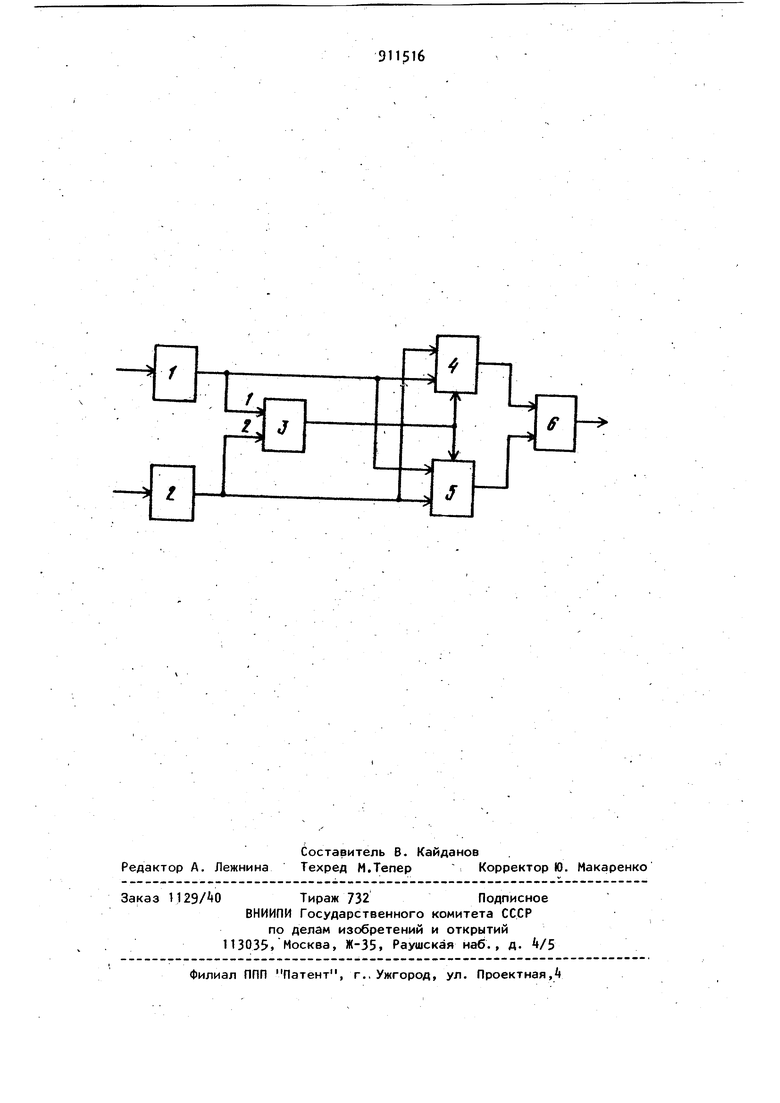

ts входов первого сумматора соответственно, выход первого коммутатора подключен к первому входу второго сумматора, прямые выходы разрядов первого регистра подключены к первым группам информационных входов первого и второго коммутаторов, вторые группы информационных входов которых Подключены к прямым выходам разрядов 39 второго регистра, инверсные выходы которого подключены к группе вторых входов первого сумматора, выход которого подключен к управляющим входа первого и второго коммутаторов,выход второго коммутатора подключен к второму входу второго сумматора, выход которого подключен к выходу устройства. На чертеж представлена структурная схема предлагаемого устройства. Устройство содержит первый регистр t , второй регистр 2, первый . сумматор 3| первый коммутатор 4,второй коммутатор 5 и второй сумматор 6 Устройство работает следующим образом. В начальный момент времени в первый регистр 1 и второй регистр 2 заносятся соответственно п-разрядные мантисы прямых кодов дeйctвительной и мнимой составляющих компг.ексного числа. С выхода первого регистра I прямой код действительной составляющей поступает на первые входы первого сумматора 3, первого коммутатора , а (п-2) разряда этого кода на второй зход второго коммутатора 5 С выхода второго регистра 2 инверсйый код мнимой составляющей поступает на второй вход первого ;cyw«aTopa 3 прямой код - на второй вход коммутатора , а (п-2) старших разряда этого кода - на второй вход второго коммутатора 5. Сигнал с выхода знакового разряд сумматора 3 поступает на управляющий вход коммутаторов t и 5 На выходе коммутатора k при соответствующем управляющем сигнале выраба тываётся код максимальной комплексн составляющей, а на выходе второго коммутатора 5 ) старшй9 разря да меньшей комплексной составляющей Сигналы с выходов коммутаторов и поступают на входы второго сумматора 6, результат сложения определяет значение модуля комплексного числа. Предлагаемое устройство позволяет производить вычисление модуля комплексного числа при сокращении оборудования по сравнению с известным устройством. Формула изобретения Устройство для вычисления модуля комплексного числа, содержащее регистры, сумматоры и коммутаторы, причем входы первого и второго регистров подключены к первому и второму информационным входам устройства, прямые выходы разрядов первого регистра подключены к группе первых exojqoe первого сумматора соответственно, выход первого коммутатора подключен к первому второго сумматора, отличающееся тем, что, с целью упрощения устройства, прямые выходы разрядов первого, регистра подключены к первым группам информационных .входов первого и второго коммутаторов, вторые группы информационных входов которых подключены к прямым выходам разрядов второго регистра, инверсные выходы которого подключены к группе вторых входов первого сумматора, выход которого подключен к управляющим входам первого и второго коммутаторов, выход второго коммутатора подключен к второму входу второго сумматора, выход которого подключен к выходу устройства.. Источники информации, принятые во.внимание при экспертизе 1.Авторское свидетельство СССР Н- , кл. G 06 F 7/38, 1976. 2.Авторское свидетельство .СССР № 623202, кл. G Об F 7/38, 1976 Гпрототип).

Авторы

Даты

1982-03-07—Публикация

1980-06-30—Подача