гистров контрольных разрядов, выход второго сумматора по модулю два соединен с третьим входом блока 1193662 (Свертки по модулю три, четвертьш вход которого соединен с выходом первого сумматора по модулю два.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления модуля комплексного числа | 1984 |

|

SU1233145A1 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1287151A1 |

| Устройство для вычисления модуля комплексного числа | 1982 |

|

SU1104505A2 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1444750A1 |

| Устройство для вычисления модуля комплексного числа | 1987 |

|

SU1508206A1 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1254478A1 |

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

| Устройство для определения модуля трехмерного вектора | 1986 |

|

SU1388854A2 |

| Устройство для контроля по модулю умножения комплексных чисел | 1986 |

|

SU1386997A1 |

| Устройство для вычисления модуля комплексного числа | 1989 |

|

SU1693599A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МОДУЛЯ КОМПЛЕКСНОГО ОДСЛА, содержащее два регистра аргументов, три сумматора, два регистра контрольных разрядов, два коммутатора и блок свертки по модулю три, причем информационные Входы первого и второго регистров аргументов подключены соответственно к входам действительной и мнимой части комплексного числа устройства, выход первого регистра аргумента соединен с входом первого операнда первого сумматора, вход второго операнда которого соединен с инверсньм выходом второго регистра аргумента, прямой выход которого соединен с входом первого операнда второго сумматора, выход которого соединен с первым информационным входом первого коммутатора, управляющий вход которого соединен с выходом знакового разряда первого сумматора, а второй информационный вход первого коммутатора соединен с выходом третьего сумматора, вход первого операнда которого соединен с выходом первого регистра аргумента, выход первого коммутатора является информационным выходом устройства, контрольным выходом которого является выход блока свертки по модулю три, первьй и второй входы которого подключены к выходам первого и второго коммутаторов, управляющий вход второго коммутатора соединен с выходом знакового разряда первого сумматора, а информационные входы первого и второго регистров контрольных разрядов подключены к входам контрольных разрядов соответственно действительной и мнимой части комплекс(Л ного числа устройства, о т л и :чающееся тем, что, с целью повышения точности вычисления, устройство дополнительно содержит § сумматор по модулю три, два сумматора по модулю два, причем выходы ; первого и второго регистров аргументов соединены со сдвигом на CD OP О) один разряд в сторону младших разрядов соответственно с входами второго регистра аргумента второго О) и третьего сумматоров, выходы hd младших разрядов первого и второго регистров аргументов соединена соответственно с первым и вторым информационными входами второго коммутатора, управляющийвход которого соединен с первыми входами первого и второго сумматоров по модулю два, вторые входы которых (Соединены с выходом сумматора по модулю три, первый и второй входы которого соединены с выходами соответственно первого и второго ре-

1

Изобретение относится к области вычислительной техники.

Целью изобретения является повьш1е1 ие точности вычислений модуля комплексного числа.

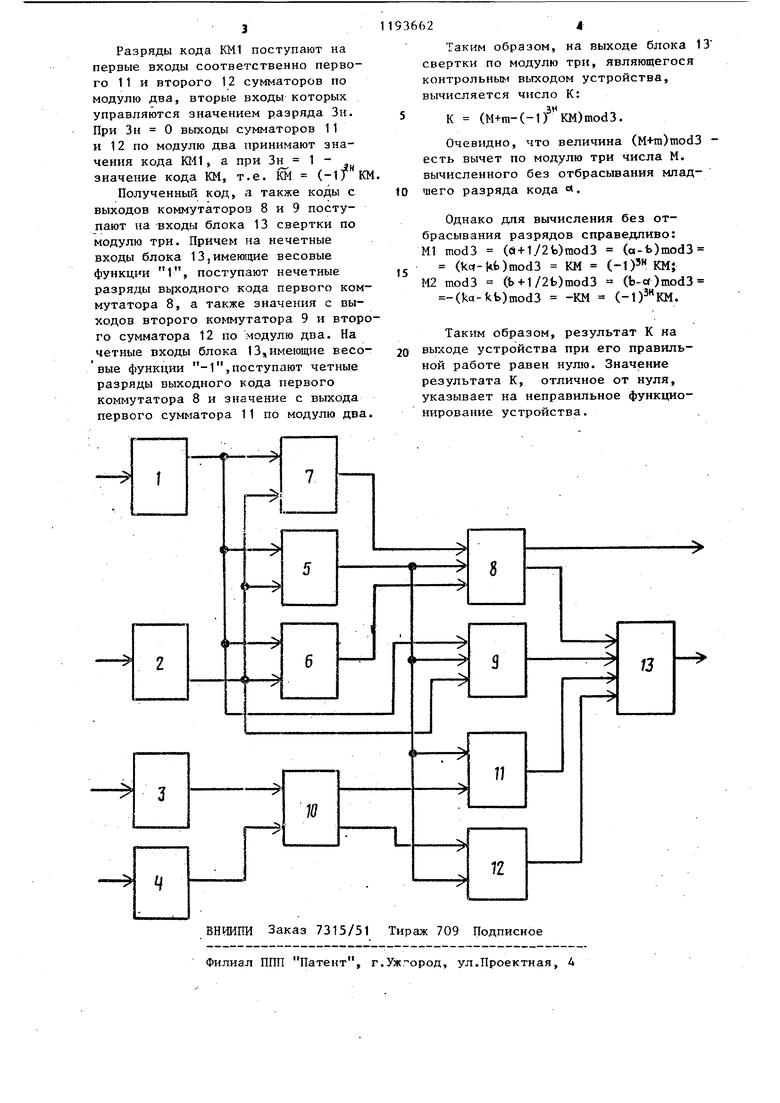

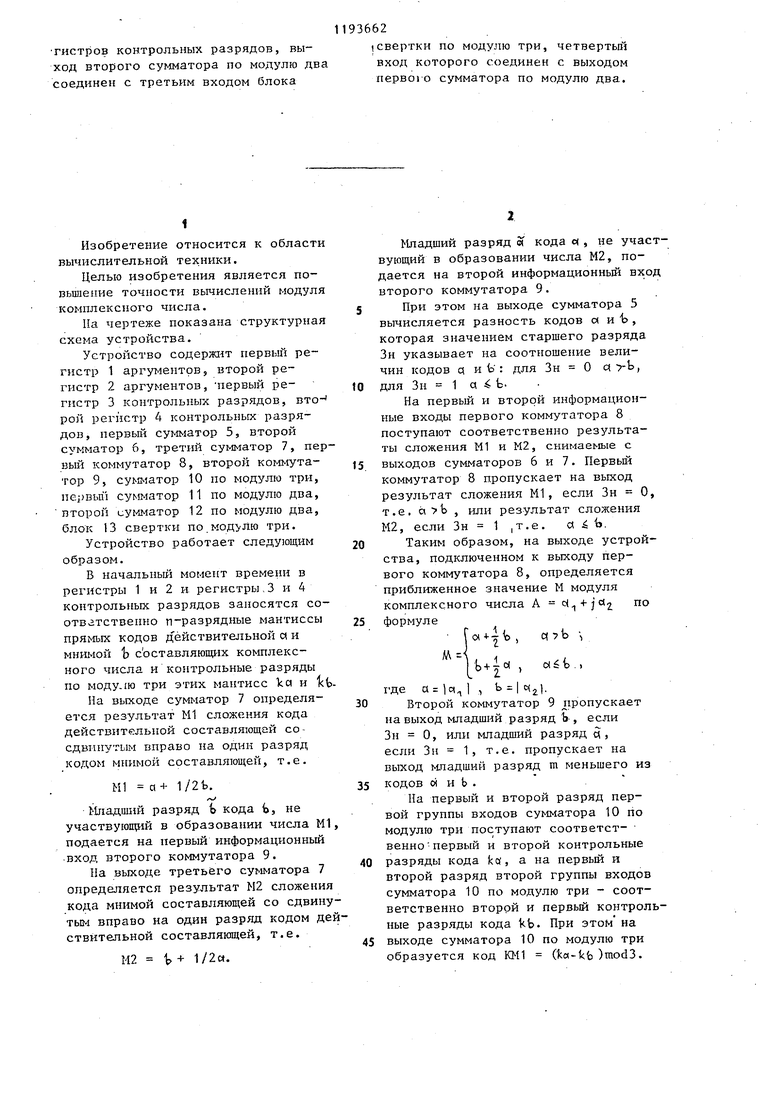

Па чертеже показана структурная схема устройства.

Устройство содержит первый регистр 1 аргументов, второй регистр 2 аргументов, первый регистр 3 контрольных разрядов, вто- рой регистр 4 контрольных разрядов , первый сумматор 5, второй сумматор 6, третий сумматор 7, первый коммутатор 8, второй ком гутатор 9, сумматор 10 по модулю три, nepBbrii сумматор 11 по модулю два, второй сумматор 12 по модулю два, блок 13 свертки по модулю три.

Устройство работает следующим образом.

В начальньш момент времени в регистры 1 и 2 и регистры,3 и 4 контрольных разрядов заносятся соответственно п-разрядные мантиссы прямых кодов действительной « и мнимой Ь составляющих комплексного числа и контрольные разряды по моду.ш три этих мантисс и выходе сумматор 7 определяется результат М1 сложения кода действительной составляющей со сдвинутым вправо на один разряд кодом мнимой составляющей, т.е.

Ml а+ 1/2Ъ. f

№1ад1шш разряд Ь кода Ь, не участвующий в образовании числа Ml подается на первый информационный вход второго коммутатора 9.

Па выходе третьего сумматора 7 опредапяется результат М2 сложения кода мнимой составляющей со сдвинуть04 вправо на один разряд кодом дествительной составляющей, т.е.

М2 V + 1/2я.

Младший разряд of кода « , не участвующий в образовании числа М2, подается на второй информадионньй вход второго коммутатора 9. При этом на выходе сумматора 5 вычисляется разность кодов ск и Ъ, которая значением старшего разряда Зн указывает на соотношение величин кодов Q и Ъ: для Зн О а гЬ,

для Зн 1 а ЬНа первый и второй информационные входы первого коммутатора 8 поступают соответственно результаты сложения Ml и М2, снимаемые с

выходов сумматоров 6 и 7. Первый коммутатор 8 пропускает на выход результат сложения М1, если Зн О, т.е. , или результат сложения М2, если |Т.е. с(Ь.

Таким образом, на выходе устройства, подключенном к выходу первого коммутатора 8, определяется приближенное значение М модуля комплексного числа А ij- 2

формуле

40(4- - Ь , С( 7 b

М

b + ld , .,

,, Ь

а 01,

где -- 1

Второй коммутатор 9 дтропускает на выход младший разряд Ъ , если Зн О, или младший разряд q, если Зн 1, т.е. пропускает на выход младший разряд m меньшего из

кодов oi и b .

Па первый и второй разряд первой группы входов сумматора 10 по модулю три поступают соответственно -первый и второй контрольные

разряды кода ka, а на первый и

второй разряд второй группы входов сумматора 10 пс) модулю три - соответственно второй и первый контрольные разряды кода kb. При этом на

выходе сумматора 10 по модулю три образуется код КМ1 (ka-kfc )mod3.

Разряды кода КМ1 поступают на первые входы соответственно первого 1 1 и второго 12 сумматоров по модулю два, вторые входы которых управляются значением разряда Зн. При Зн О выходы сумматоров 11 и 12 по модулю два принимают значения кода КМ1, а при Зн 1 значение кода КМ, т.е. КМ (-1; КМ

Полученный код, а также коды с выходов коммутаторов 8 и 9 поступают на входы блока 13 свертки по модулю три. Причем на нечетные входы блока 13,имеющие весовые функции 1, поступают нечетные разряды вь|ходного кода первого коммутатора 8, а также значения с выходов второго коммутатора 9 и второго сумматора 12 по модулю два. На четные входы блока 13,имеющие весовые функции -1,поступают четные разряды выходного кода первого коммутатора 8 и значение с выхода первого сумматора 11 по модулю два.

1936624

Таким образом, на выходе блока 13 свертки по модулю три, являющегося контрольныь выходом устройства, вычисляется число К:

5 К (М-ьт-(-1ГкМ)тоаЗ.

Очевидно, что величина (M+m)mod3 есть вычет по модулю три числа М. вычисленного без отбрасывания младшего разряда кода «.

10

Однако дня вычисления без отбрасывания разрядов справедливо: Ml mod3 (a + 1./2t)raod3 (a-b)mod3

(kct-Kfc)mod3 KM (-1) KM; M2 mod3 (b + 1/2b)mod3 (b-or)mod3

-(ka-kb)mod3 -KM (-1)KM.

Таким образом, результат К на выходе устройства при его правильной работе равен нулю. Значение результата К, отличное от нуля, указывает на неправильное функционирование устройства.

| КОМБИНИРОВАННАЯ ПАРОГАЗОВАЯ УСТАНОВКА | 0 |

|

SU377531A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления модуля комплексного числа | 1982 |

|

SU1104505A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-11-23—Публикация

1984-05-11—Подача