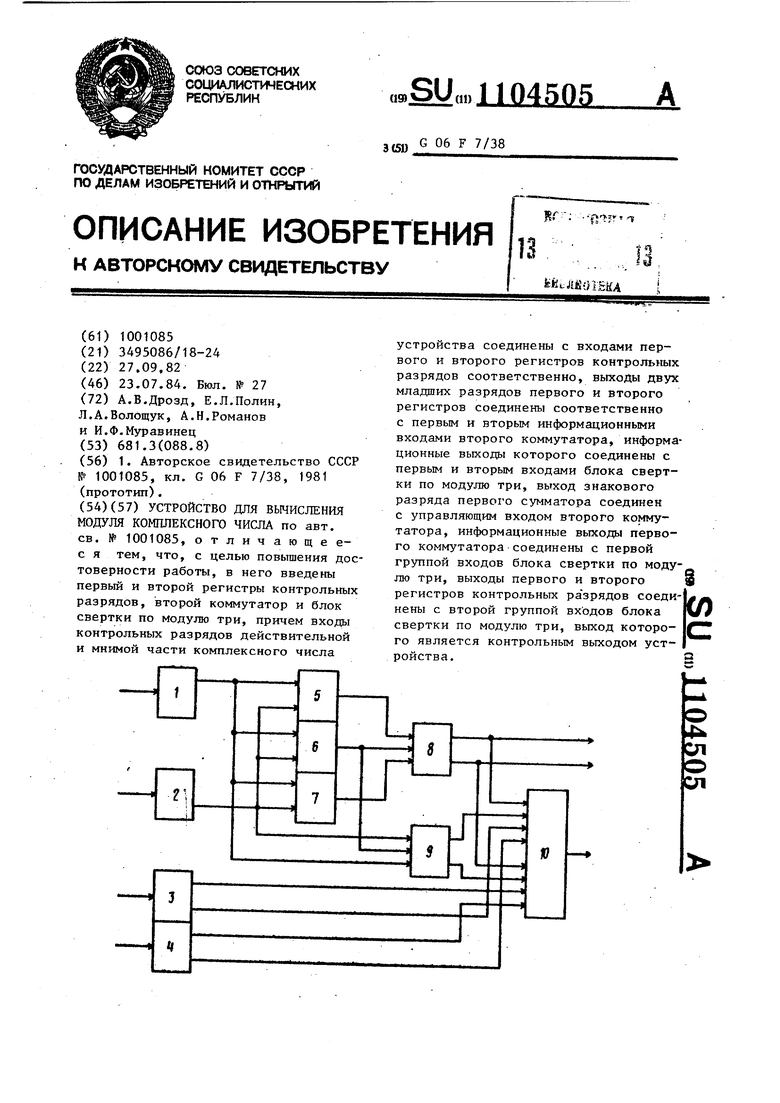

Изобретение относится к вычислительной технике. По основному авт.св. № 1001085 известно устройство для вычисления модуля комплексного числа, содержащее регистры, сумматоры и первый коммутатор, причем входы разрядов первого и второго регистров подключены к информационным входам устройства соответственно, прямые выходы разрядов первого регистра подключены к первой группе входов первого сумма тора соответственно, инверсные выходы второго регистра подключены к второй группе входов первого сумматора соответственно, прямой и инверс ный выходы знакового разряда которого подключены к управляющему входу первого коммутатора, первая группа входов второго сумматора подключена к прямым выходам разрядов первого регистра соответственно (ti-2) старших разрядов которого подключены к первой группе входов третьего сумматора соответственно, вторая группа входов которого подключена к прямым выходам разрядов второго регистра соответственно, прямые выходы (и-2) старших разрядов которого пoдк Iючeны к второй группе входов второго сумматора соответственно, выходы разрядов второго и третьего сумматоров подключены к первой и второй группам информационных входов первого коммутатора соответственно, выходы которо го подключены к выходам устройства l Недостатком известного устройства является низкая достоверность фун ционирования, так как устройство осуществляет вычисление модуля комп лексного числа без контроля. Цель изобретения - повышение достоверности работы устройства. Поставленная цель достигается тем что в устройство для вычисления моду ля комплексного числа введены первьй и второй регистры контрольных разрядов, второй коммутатор и блок свертки по модулю три, причем входы контрольных разрядов действительной и мнимой части комплексного числа устройства соединены с входами первого и второго регистров контрольных разрядов соответственно, выходы двух младших разрядов первого и второго регистров соединены соответственно с первым и вторым информационными входами второго коммутатора, инфорйа ционные выходы которого соединены с первым и вторым входами блока свертки по модулю три, вь1ход знакового разряда первого сумматора соединен с управляющим входом второго коммутатора, информационные выходы первого коммутатора соединены с первой группой входов блока свертки по модулю три, выходы первого и второго регистров контрольных разрядов соединены с второй группой входов блока свертки по модулю три, выход которого является контрольным выходом устройства. На чертеже представлена структурная схема устройства. Устройство содержит первый 1 и второй 2 регистры, первьй 3 и второй 4 регистры контрольных разрядов, второй 5, первый 6, третий 7 сумматоры, первый 8 и второй 9 коммутаторы, блок 10 свертки по модулю три. Входы разрядов первого 1 и второго 2 регистров подключены к информа.ционным входам устройства соответственно, прямые выходы разрядов первого регистра 1 подключены к первой группе входов первого сумматора 6 соответственно, инверсные выходы разрядов второго регистра 2 подключены к второй группе .входов первого сумматора 6 соответственно, прямой и инверсный выходы знакового .разряда которого подключены к управляющему входу первого коммутатора 8, первая групра входов второго сумматора 5 подключена к прямым выходам первого регистра 1 соответственно, (п-2) старших разрядов которого пoдк ючeны к первой группе входов третьего сумматора 7 соответственно, вторая группа входов которого подключена к прямым выходам разрядов второго регистра 2 соответственно, прямые выходы (ti-2) старших разрядов которого подключены к второй группе входов второго сумматора 5 соответственно, выходы разрядов второго 5 и третьего 7 сумматоров подключены к первой и второй группам информационных входов первого коммутатора 8 соответственно, выходы которого подключены к выходам устройства, к первой группе входов блока 10 свертки по модулю три подключены нечетные выходы первого 8 и второго 9 коммутаторов и выходы четных разрядов первого 3 и второго 4 регистров контрольных разрядов, к

второй группе входов блока 10 свертки по модулю три подключены четные выходи первого 8 и второго 9 коммутаторов и выходы нечетньк разрядов первого 3 и второго 4 регистров контрольйых разрядов, входы которых подключены к контрольным входам устройства соответственно, первая и вторая группа входов второго коммутатора 9 подключены к прямым выходам двух младших разрядов второго 2 и первого 1 регистров соответственно, а выход знакового разряда -первого сумматора 6 подключен к управляющему входу второго коммутатора 9, выход блока 10 свертки по модулю три подключен к контрольному выходу устройств

Устройство работает следующим образом.

В начальньм момент времени в первый 1 и второй 2 регистры и в первый 3 и второй 4 регистры контрольных разрядов заносятся соответственн П-разрядные мантиссы прямых кодов действительной а и мнимой о составляющих комплексного числа и контрольные разряды по модулю три этих мантисс : и 1сЪ .

С выходов первого 1 и второго 2 регистров коды а и b подаются на входы первого 6, второго 5 и третьего 7 сумматоров. При этом на первый и второй входы второго сумматора 5 поступают соответственно код действительной составляющей и п -2 старших разряда кода мнимой составляющей комплексного числа. На выходе второго сумматора 5 определяется результат сложения Ml кода действительной составляющей со сдвинутым вправо на два разряда кодом мни-юй составляющей, т.е. Ml 01 +7.

Два младших разряда кодаb , не участвовавшие в вычислении числа Ml, подаются на первый вход второго коммутатора 9.

На первый и второй входы третьего сумматора 7 поступают соответственно код мнимой составляющей им-2 старших разряда кода действительной составляющей комплексного числа. На выходе третьего сумматора 7 определяется результат сложения М2 кода мнимой составляющей со сдвинутым вправо на два разряда кодом действительной составляющей, т.е. М2 Ь + q .

Два младших разряда а кода d , не участвующие в вычислении числа М2,

подаются на второй вход второго коммутатора 9. На первый вход и второй инверсный вход первого сумматора 6 .поступают соответственно коды а и Ь. При зтом на выходе первого сумматора 6 вычисляется разность кодов d и b, которая значением старшего разряда Зн указыв ает на соотношение величин кодов а иЬ: при Зн 0,0(Ъ, при Зн 1, а Ъ .

Сигнал с выхода разряда Зн поступает на управляющие входы первого 8 и второго 9 коммутаторов. На первый и второй информационные входы первого коммутатора 8 поступают соответственно результаты сложения Ml и М2, снимаемые с выходов второго 5 и третьего 7 сумматоров.

Первый коммутатор 8 пропускает на выход результат сложения М1, если Зн О, т.е. , или М2, если Зн 1, т.е. а 6 Ь .

Таким образом, на выходе устройства определяется величина

а + Т b , если а Ъ ,

М Ь + 7 если Ь а ,

используемая в ряде задач в качестве модуля комплексного числа А , где а 1а,1 , Ь .

Второй коммутатор 9 пропускает на выход или два младших, разряда Ъ , если Зн О, или два младших разряа а , если Зн 1, т.е. пропускает ладшие разряды щ меньшего из коов q и Ъ . .

Сигналы, снимаемые с выходов нечетных разрядов первого 8 и второго 9 коммутаторов, а также с выходов четных разрядов первого 3 и второго 4 регистров контрольных разрядов поступают на первую группу входов блока 10 свертки по модулю три. Входы первой группы имеют весовые функции, равные 1.

На вторую группу входов блока 10 свертки по модулю три поступают сигналы, снимаемые с ВЬЕХОДОВ четных разрядов первого 8 и второго 9 коммутаторов, а также с выходов нечетных разрядов первого 3 и второго 4 регистров контрольных разрядов. Входы второй группы имеют весовые, функции, равные -1 (или 2). Таким образом, блок 10 свертки по модулю три реализует вычисление некоторого числа К по формуле К (М tn-Va-k1))mod3. Очеввдио, что величии (M-nii)mod3 есть вычет по модулю три числаМ, найденного без отбрасывания двух младших разрядов наименьшего из катодов аи Ь однако для вЬпислений без отбрасьшания разрядов справедливо () {Q+b) M2mo33-()mod3(b + a)moa3j WlmoJ M2moa ila b)nod3(kafkb)mod3. Следовательно( (ka k motJB. Таким образом, результат К на выходе устройства при его правильной работе равен нулю. Значение результата. К, отличное от нуля, указывает на неправильное функционирование устройства. Предлагаемое устройство позволяет повысить достоверность вычисления мЬдуля комплексного числа, так как вероятность отказа устройства для вьмисления модуля комплексного числа на порядок вьше, чем вероятность otKasa вновь введенной аппаратуры контроля.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления модуля комплексного числа | 1984 |

|

SU1193662A1 |

| Устройство для вычисления модуля комплексного числа | 1984 |

|

SU1233145A1 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1287151A1 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1254478A1 |

| Устройство для вычисления модуля комплексного числа | 1990 |

|

SU1753472A1 |

| Устройство для вычисления модуля комплексного числа | 1985 |

|

SU1444750A1 |

| Устройство для вычисления модуля комплексного числа | 1987 |

|

SU1508206A1 |

| Устройство для контроля по модулю три умножения комплексных чисел | 1987 |

|

SU1434438A1 |

| Устройство для вычисления модуля комплексного числа | 2016 |

|

RU2618188C1 |

| Устройство для вычисления модуля комплексного числа | 1981 |

|

SU1001085A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ МОДУЛЯ КОМПЛЕКСНОГО ЧИСЛА по авт. св. № 1001085, отличающеес я тем, что, с целью повышения достоверности работы, в него введены первый и второй регистры контрольных разрядов, второй коммутатор и блок свертки по модулю три, причем входы контрольных разрядов действительной и мнимой части комплексного числа устройства соединены с входами первого и второго регистров контрольных разрядов соответственно, выходы двух младших разрядов первого и второго регистров соединены соответственно с первым и вторым информационными входами второго коммутатора, информационные выходы которого соединены с первым и вторым входами блока свертки по модулю три, выход знакового разряда первого сумматора соединен с управляющим входом второго коммутатора, информационные выходы первого коммутатора соединены с первой группой входов блока свертки по модулю три, выходы первого и второго регистров контрольных разрядов соеди(Л нены с второй группой входов блока свертки по модулю три, выход которого является контрольным выходом устройства. V

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для вычисления модуля комплексного числа | 1981 |

|

SU1001085A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-23—Публикация

1982-09-27—Подача